Giorgos Dimitrakopoulos Anastasios Psarras Ioannis Seitanidis

# Microarchitecture of Network-onchip Routers

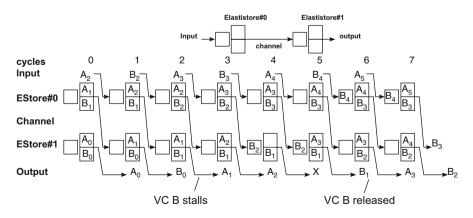

A Designer's Perspective

Microarchitecture of Network-on-Chip Routers

Giorgos Dimitrakopoulos • Anastasios Psarras Ioannis Seitanidis

# Microarchitecture of Network-on-Chip Routers

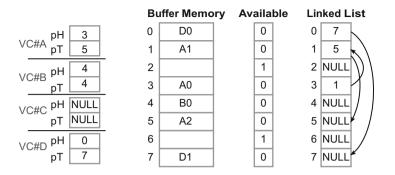

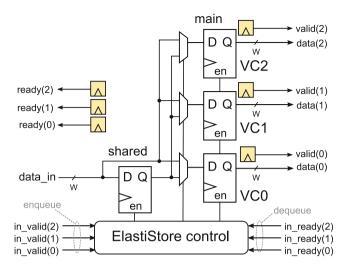

A Designer's Perspective

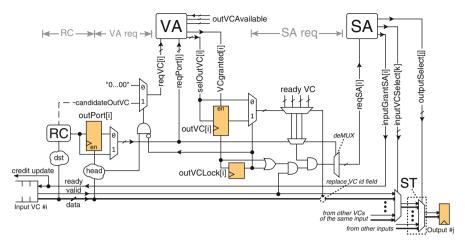

Giorgos Dimitrakopoulos Electrical and Computer Engineering Democritus University of Thrace Xanthi, Greece

Ioannis Seitanidis Electrical and Computer Engineering Democritus University of Thrace Xanthi, Greece Anastasios Psarras Electrical and Computer Engineering Democritus University of Thrace Xanthi, Greece

ISBN 978-1-4614-4300-1 ISBN 978-1-4614-4301-8 (eBook) DOI 10.1007/978-1-4614-4301-8 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2014945972

#### © Springer Science+Business Media New York 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To Alexandros, Labros, and Marina G.D.

*To Yiannis and Aphrodite A.P.*

To Ioannis and Vassiliki I.S.

# Preface

Modern computing devices, ranging from smartphones and tablets up to powerful servers, rely on complex silicon chips that integrate inside them hundreds or thousands of processing elements. The design of such systems is not an easy task. Efficient design methodologies are needed that would organize the designer's work and reduce the risk for a low-efficiency system. One of the main challenges that the designer faces is how to connect the components inside the silicon chip, both physically and logically, without compromising performance. The network-on-chip (NoC) paradigm tries to answer this question by applying at the silicon chip level well established networking principles, after suitably adapting them to the silicon chip characteristics and to application demands. The routers are the heart and the backbone of the NoC. Their main function is to route data from source to destination, while they provide arbitrary connectivity between several inputs and outputs that allows the implementation of arbitrary network topologies.

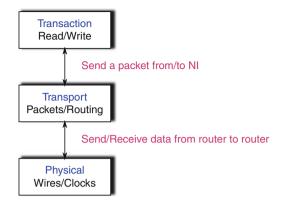

This book focuses on the microarchitecture of NoC routers that together, with the network interfaces, execute all network functionalities. The routers implement the transport and physical layers of the NoC, and their internal organization critically affects the speed of the network in terms of clock frequency, the throughput of the network in terms of how many packets can the network service per clock cycle and, the network's area and energy footprint on the silicon die.

The goal of this book is to describe the complex behavior of network routers in a compositional approach following simple construction steps that can be repeated by any designer in a straightforward manner. The micro-architectural features presented in this book are built on top of detailed examples and abstracted models, when necessary, that do not leave any dark spots on the operation of the presented blocks and reveal the dependencies between the different parts of the router, thus enabling any possible future optimization. The material of each chapter evolves linearly, covering simpler cases before moving to more complex architectures.

Chapter 1 gives an overview of network-on-chip design at the system level and discusses the layered approach followed for transforming the abstract read and

write transactions between the modules of the system to actual bits that travel in parallel on the links of the network finding their path towards their final destination, using the routers of the network.

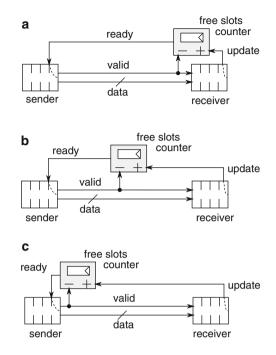

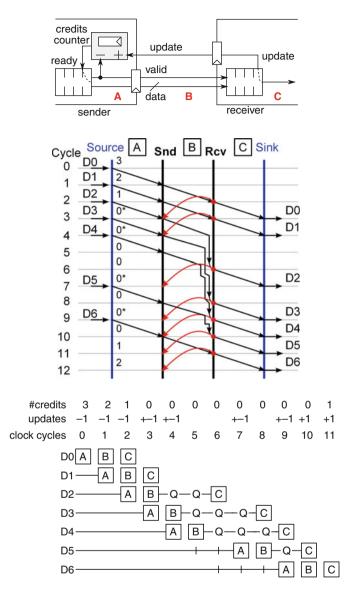

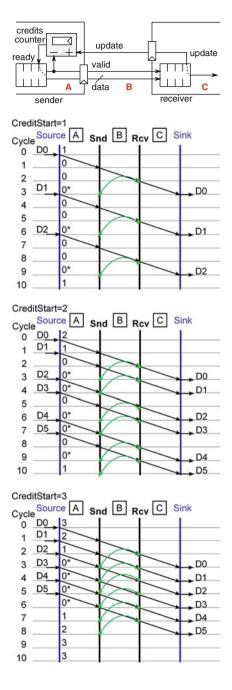

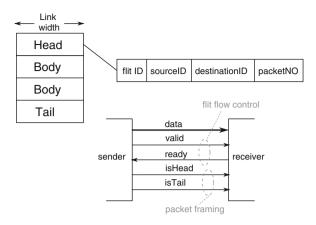

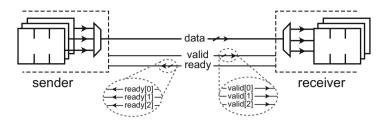

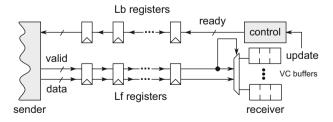

- Chapter 2 deals with link-level flow control policies and associated buffering requirements for guaranteeing lossless and full throughput operation for the communication of a single sender and receiver pair connected with a simple point-to-point link. The discussion includes both simple ready/valid flow control as well as credit-based policies under a unified abstract flow control model. The behavior of both flow control policies when used in pipelined links is analyzed and analytical bounds are derived for each case. The chapter ends with the packetization process and the enhancement needed to link-level flow control policies for supporting multiword packets.

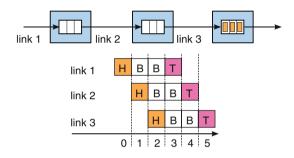

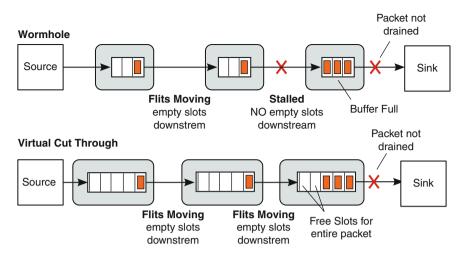

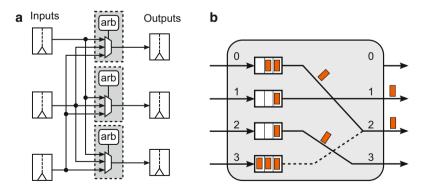

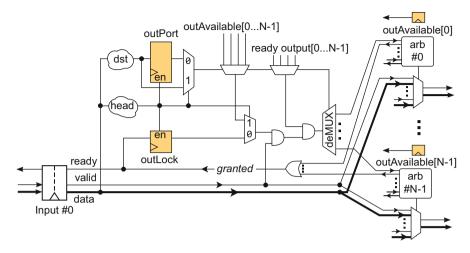

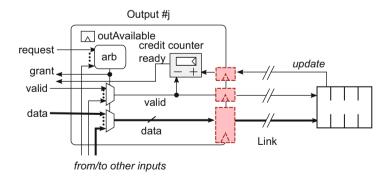

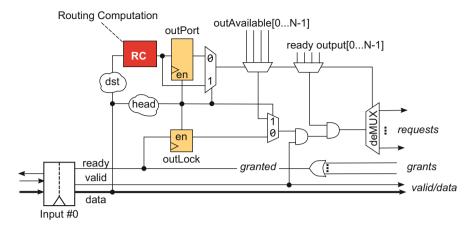

- Chapter 3 departs from point-to-point links and discusses in a step-by-step manner the organization of many-to-one and many-to-many switched connections supporting either simple or fully unrolled datapaths. The interplay between arbitration, multiplexing and flow control is analyzed in detail using both credits and ready/valid protocols. The chapter ends with the design of a full wormhole (or virtual-cut through) router that includes also a routing computation module that allows routers to be embedded in arbitrary network topologies.

- Chapter 4 departs from router microarchitecture and describes in detail the circuitlevel organization of the arbiters and multiplexers used in the control and the datapath of the routers. A unified approach is presented that merges algorithmically the design of arbiters that employ various arbitration policies with that of multiplexing and allows the design of efficient arbiter and multiplexing circuits. Additionally, arbiters built on top of 2D relative priority state are also discussed in detail.

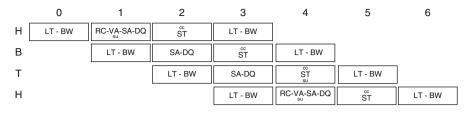

- Chapter 5 dives deeper in the microarchitecture of a wormhole router and discusses in a compositional manner the pipeline alternatives of wormhole routers and their implementation/performance characteristics. Multiple pipelined organizations are derived based on two pipeline primitive modules. For each case, complete running examples are given that highlight the pipeline idle cycles imposed by the router's structural dependencies, either across packets or inside packets of the same input, and the way such dependencies are removed after appropriate pipeline modifications.

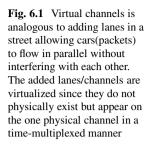

- Chapter 6 introduces virtual channels together with the flow control mechanism and the buffering architectures needed to support their operation. Virtual channels correspond to adding lanes to a street network that allow cars (packets) to utilize in a more efficient manner the available physical resources. Lanes are added virtually and the packets that move in different lanes use the physical channels of the network in a time-multiplexed manner. The interplay of buffering, flow-control latencies and the chosen flow control mechanism (ready/valid or credits) are analyzed in detail in this chapter and the requirements of each configuration are identified.

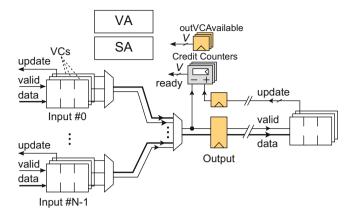

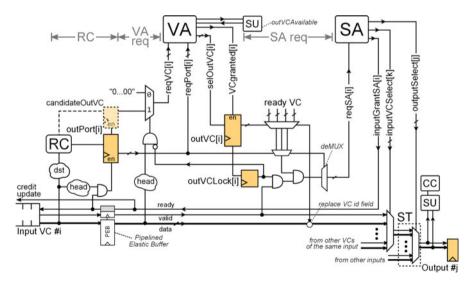

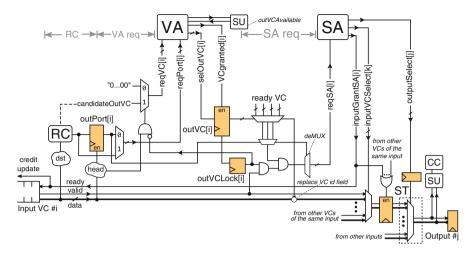

- Chapter 7 introduces the microarchitecture of routers that connect links that support multiple virtual channels. The design of virtual-channel-based switching

connections begins from a simple many-to-one switching module and evolves to a complete virtual-channel-based router. The operation of a virtual-channelbased router involves several tasks that are analyzed in detail together with their dependencies and their interaction with the flow-control mechanism.

- Chapter 8 builds on top of Chap. 7 and presents the organization of high-speed allocators that speedup significantly the operation of a baseline single-cycle virtual-channel-based router. Multiple alternatives are presented that allow either the reduction of the needed allocation steps or their parallel execution that effectively reduces the hardware delay of the router.

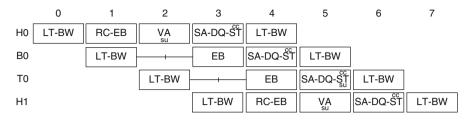

- Chapter 9 deals with the pipelined organization and microarchitecture of virtualchannel-based routers. The pipelined configurations of the virtual-channel-based routers are described in a modular manner, beginning from the description of the structure and operation of three primitive pipeline stages. Then, following a compositional approach, several multi-stage pipelined configurations are derived by connecting the presented primitive stages in a plug-and-play manner, which helps in understanding better the operation of complex organizations and their associated timing-throughput tradeoffs.

Overall, we expect system, architecture, circuit, and EDA researchers and developers, who are interested in understanding the microarchitecture of networkon-chip routers, the associated design challenges, and the available solutions, to benefit from the material of this book and appreciate the order of presentation that evolves in a step-by-step manner, from the basic design principles to sophisticated design techniques.

Xanthi, Greece June 2014 Giorgos Dimitrakopoulos Anastasios Psarras Ioannis Seitanidis

# Contents

| 1 | Introduction to Network-on-Chip Design |                                                           |    |  |  |

|---|----------------------------------------|-----------------------------------------------------------|----|--|--|

|   | 1.1                                    |                                                           |    |  |  |

|   | 1.2                                    | Flow Control                                              |    |  |  |

|   | 1.3                                    | Read–Write Transactions                                   |    |  |  |

|   | 1.4                                    | Transactions on the Network: The Transport Layer          |    |  |  |

|   |                                        | 1.4.1 Network Interfaces                                  | 6  |  |  |

|   |                                        | 1.4.2 The Network: The Physical Layer                     | 8  |  |  |

|   | 1.5                                    | Putting It All Together                                   | 9  |  |  |

|   | 1.6                                    | Take-Away Points                                          | 10 |  |  |

| 2 | Link-Level Flow Control and Buffering  |                                                           |    |  |  |

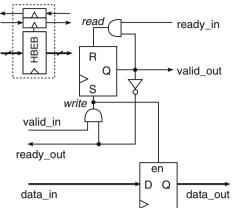

|   | 2.1                                    | Elastic Buffers                                           | 12 |  |  |

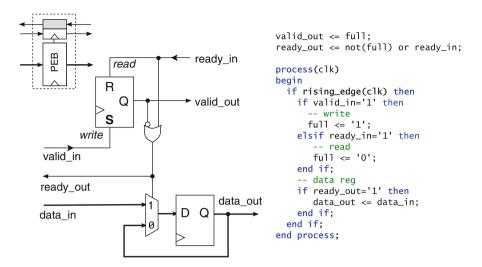

|   |                                        | 2.1.1 Half-Bandwidth Elastic Buffer                       | 13 |  |  |

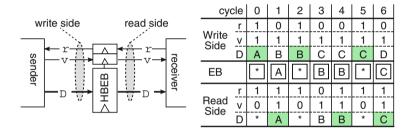

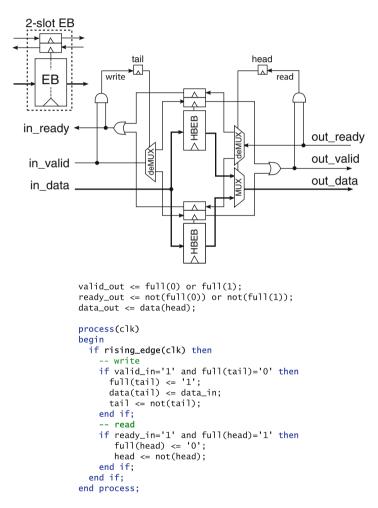

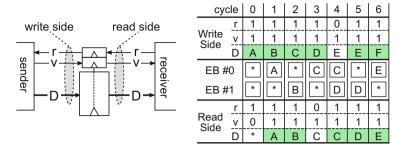

|   |                                        | 2.1.2 Full-Bandwidth 2-Slot Elastic Buffer                | 15 |  |  |

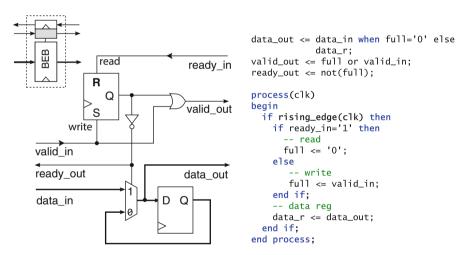

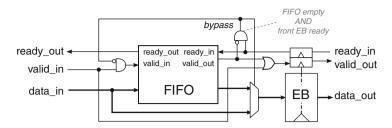

|   |                                        | 2.1.3 Alternative Full-Throughput Elastic Buffers         | 16 |  |  |

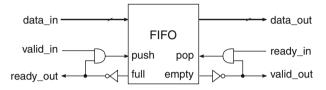

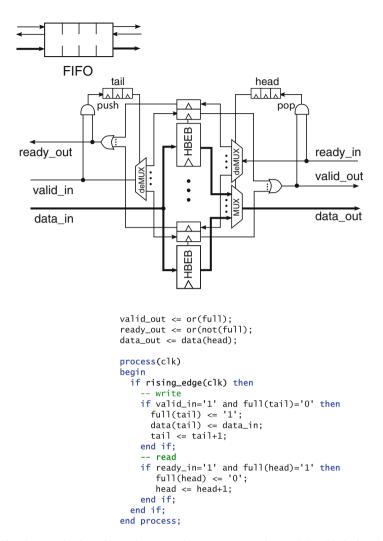

|   | 2.2                                    | Generic FIFO Queues                                       | 18 |  |  |

|   | 2.3                                    | Abstract Flow Control Model                               | 20 |  |  |

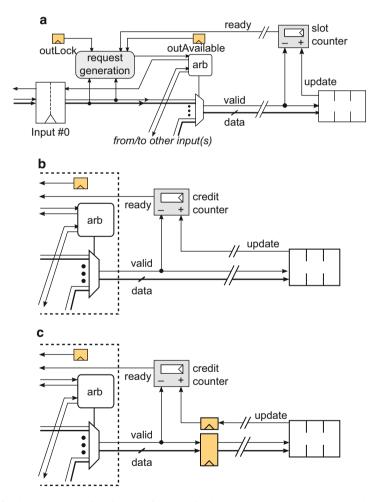

|   | 2.4                                    | Credit-Based Flow Control                                 | 21 |  |  |

|   | 2.5                                    | Pipelined Data Transfer and the Round-Trip Time           | 22 |  |  |

|   |                                        | 2.5.1 Pipelined Links with Ready/Valid Flow Control       | 24 |  |  |

|   |                                        | 2.5.2 Pipelined Links with Elastic Buffers                | 27 |  |  |

|   |                                        | 2.5.3 Pipelined Links and Credit-Based Flow Control       | 28 |  |  |

|   | 2.6                                    | Request-Acknowledge Handshake and Bufferless Flow Control | 31 |  |  |

|   | 2.7                                    | Wide Message Transmission                                 | 32 |  |  |

|   | 2.8                                    | Take-Away Points                                          | 35 |  |  |

| 3 | Bas                                    | eline Switching Modules and Routers                       | 37 |  |  |

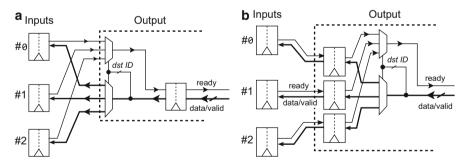

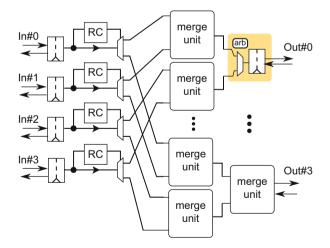

|   | 3.1                                    | Multiple Inputs Connecting to One Output                  | 38 |  |  |

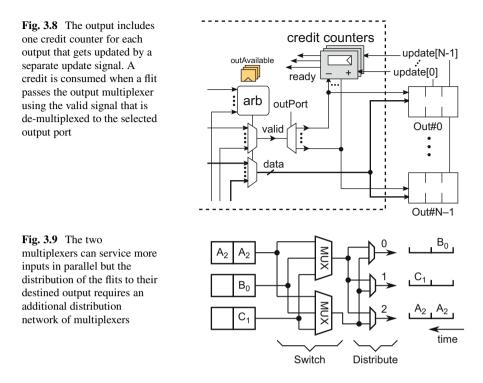

|   |                                        | 3.1.1 Credit-Based Flow Control at the Output Link        | 41 |  |  |

|   |                                        | 3.1.2 Granularity of Buffer Allocation                    | 42 |  |  |

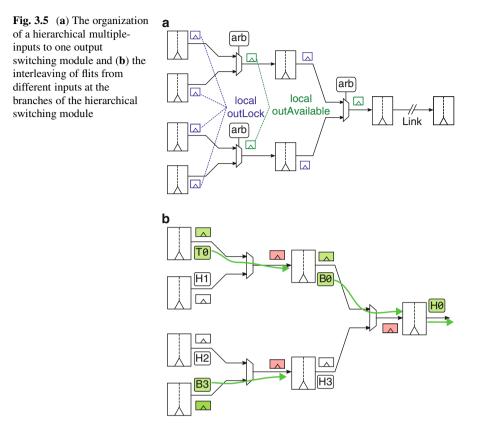

|   |                                        | 3.1.3 Hierarchical Switching                              | 43 |  |  |

|   | 3.2                                                                                                                 | The Reverse Connection: Splitting One Source to Many                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                    |

|---|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|   |                                                                                                                     | Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                 |

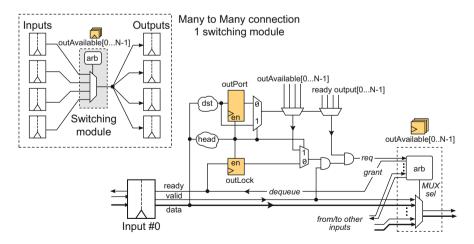

|   | 3.3                                                                                                                 | Multiple Inputs Connecting to Multiple Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

|   |                                                                                                                     | Using a Reduced Switching Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46                                                                                                 |

|   |                                                                                                                     | 3.3.1 Credit-Based Flow Control at the Output Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                                                                 |

|   |                                                                                                                     | 3.3.2 Adding More Switching Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                                 |

|   | 3.4                                                                                                                 | Multiple Inputs Connecting to Multiple Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

|   |                                                                                                                     | Using an Unrolled Switching Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                 |

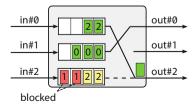

|   | 3.5                                                                                                                 | Head-of-Line Blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                 |

|   | 3.6                                                                                                                 | Routers in the Network: Routing Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                                 |

|   |                                                                                                                     | 3.6.1 Lookahead Routing Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                 |

|   | 3.7                                                                                                                 | Hierarchical Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                                                 |

|   | 3.8                                                                                                                 | Take-Away Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                 |

| 4 | Arh                                                                                                                 | itration Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                 |

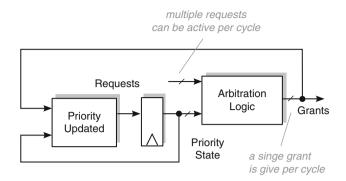

|   | 4.1                                                                                                                 | Fixed Priority Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                                 |

|   |                                                                                                                     | 4.1.1 Generation of the Grant Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                                                 |

|   | 4.2                                                                                                                 | Round-Robin Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                                 |

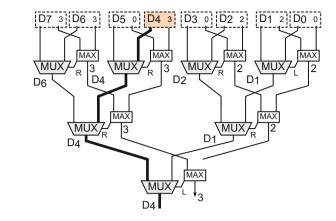

|   |                                                                                                                     | 4.2.1 Merging Round-Robin Arbitration with Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                                                                                 |

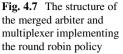

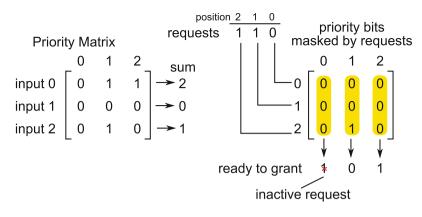

|   | 4.3                                                                                                                 | Arbiters with 2D Priority State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68                                                                                                 |

|   |                                                                                                                     | 4.3.1 Priority Update Policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                 |

|   | 4.4                                                                                                                 | Take-Away Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71                                                                                                 |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| _ | <b>D</b> !                                                                                                          | Paral Wennel als Developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                 |

| 5 |                                                                                                                     | elined Wormhole Routers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                 |

| 5 | <b>Pipe</b><br>5.1                                                                                                  | Review of Single-Cycle Router Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                 |

| 5 |                                                                                                                     | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75<br>76                                                                                           |

| 5 | 5.1                                                                                                                 | <ul><li>Review of Single-Cycle Router Organization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75<br>76<br>76                                                                                     |

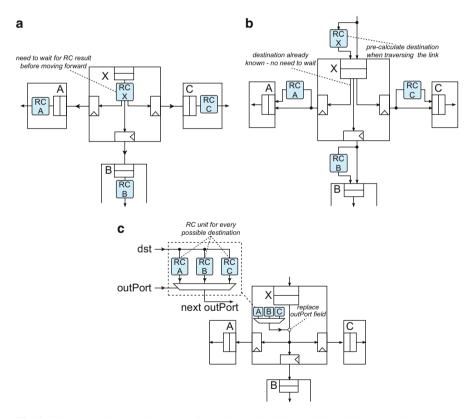

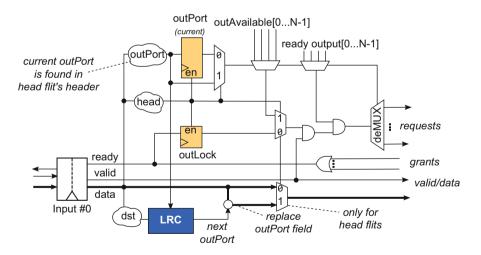

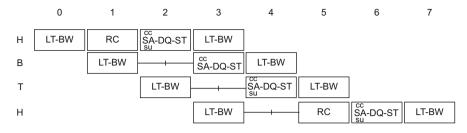

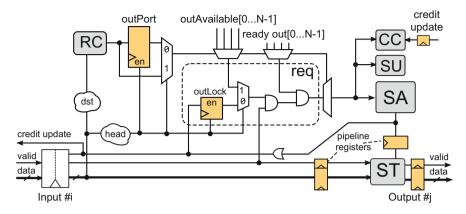

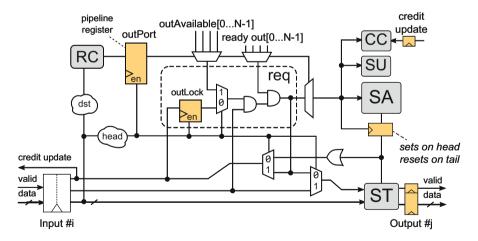

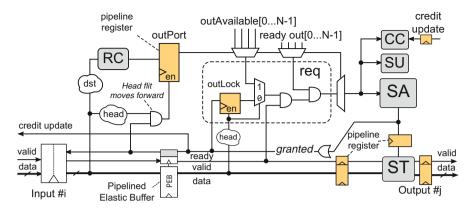

| 5 |                                                                                                                     | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75<br>76<br>76<br>77                                                                               |

| 5 | 5.1<br>5.2                                                                                                          | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>77<br>80                                                                         |

| 5 | 5.1                                                                                                                 | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75<br>76<br>76<br>77<br>80<br>82                                                                   |

| 5 | 5.1<br>5.2                                                                                                          | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage5.3.1Elementary Organization                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>77<br>80<br>82<br>82                                                             |

| 5 | 5.1<br>5.2                                                                                                          | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage                                                                                                                                                                                                                                                                                                                                                                              | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>82<br>84                                                 |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                                       | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage                                                                                                                                                                                                                                                                                                                                                           | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>82<br>84<br>86                                           |

| 5 | 5.1<br>5.2                                                                                                          | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage                                                                                                                                                                                                                                                                                                                                                           | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>82<br>84<br>86<br>88                                     |

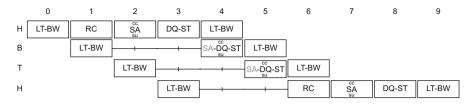

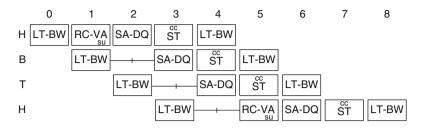

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                                       | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path                                                                                                                                                                                                               | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>82<br>84<br>88<br>88                               |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                                           | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the Datapath                                                                                                                                                                                                          | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>82<br>84<br>86<br>88<br>88<br>88                         |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                         | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline StageThe Switch Allocation Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Points                                                                                                                                                                                          | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>88<br>89<br>91                   |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt</li> </ul>                           | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Points                                                                                                                                                                                                                              | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>88<br>89<br>91<br>93             |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt 6.1</li> </ul>                       | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Pointsual-Channel Flow Control and BufferingThe Operation of Virtual-Channel Flow Control                                                                                      | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>89<br>91<br>93<br>94             |

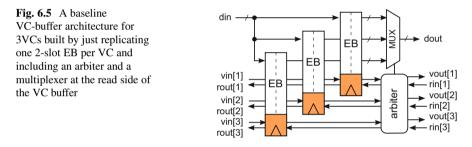

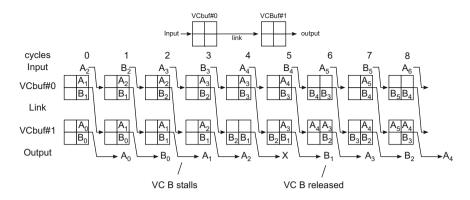

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt</li> <li>6.1</li> <li>6.2</li> </ul> | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Pointsual-Channel Flow Control and BufferingThe Operation of Virtual-Channel Flow ControlVirtual-Channel Buffers                                                               | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>89<br>91<br>93<br>94<br>97       |

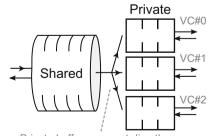

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt 6.1</li> </ul>                       | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Pointsual-Channel Flow Control and BufferingThe Operation of Virtual-Channel Flow ControlVirtual-Channel BuffersBuffer Sharing                                                 | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>89<br>91<br>93<br>94             |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt</li> <li>6.1</li> <li>6.2</li> </ul> | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Pointsual-Channel Flow Control and BufferingThe Operation of Virtual-Channel Flow ControlVirtual-Channel BuffersBuffer Sharing6.3.1The Organization and Operation of a Generic | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>89<br>91<br>93<br>94<br>97<br>99 |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Virt</li> <li>6.1</li> <li>6.2</li> </ul> | Review of Single-Cycle Router Organization5.1.1Credit Consume and State Update5.1.2Example of Packet Flow in the Single-Cycle RouterThe Routing Computation Pipeline Stage5.2.1Idle-Cycle Free Operation of the RC Pipeline Stage5.3.1Elementary Organization5.3.2Alternative Organization of the SA Pipeline Stage5.3.3Idle-Cycle Free Operation of the SA Pipeline Stage5.3.4Pipelined Routers with RC and SA Pipeline Stages5.4.1Pipelining the Router Only in the Control Path5.4.2Pipelining the Router in the Control and the DatapathTake-Away Pointsual-Channel Flow Control and BufferingThe Operation of Virtual-Channel Flow ControlVirtual-Channel BuffersBuffer Sharing                                                 | 75<br>76<br>76<br>77<br>80<br>82<br>82<br>84<br>86<br>88<br>88<br>89<br>91<br>93<br>94<br>97       |

#### Contents

|   | 6.4  | VC Flow Control on Pipelined Links                                               | 105        |  |

|---|------|----------------------------------------------------------------------------------|------------|--|

|   |      | 6.4.1 Pipelined Links with VCs Using Ready/Valid                                 |            |  |

|   |      | Flow Control                                                                     | 106        |  |

|   |      | 6.4.2 Pipelined Links with VCs Using Credit-Based                                |            |  |

|   |      | Flow Control                                                                     | 108        |  |

|   | 6.5  | Take-Away Points                                                                 | 109        |  |

| 7 | Base | Baseline Virtual-Channel Based Switching Modules and Routers                     |            |  |

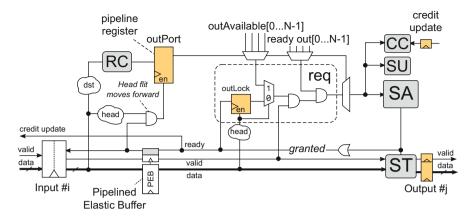

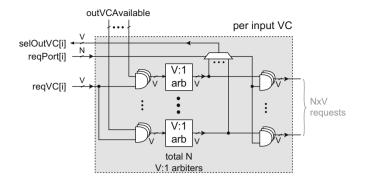

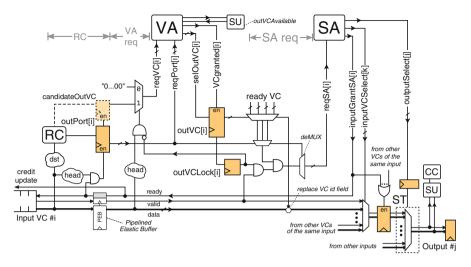

|   | 7.1  | Many to One Connection with VCs                                                  | 111        |  |

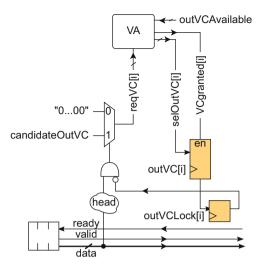

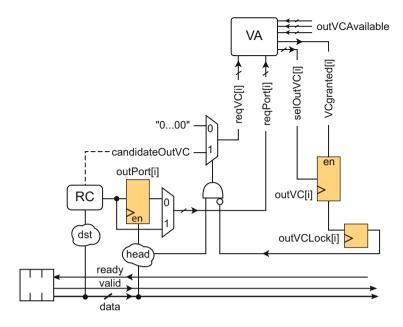

|   |      | 7.1.1 State Variables Required Per-Input and Per-Output VC                       | 112        |  |

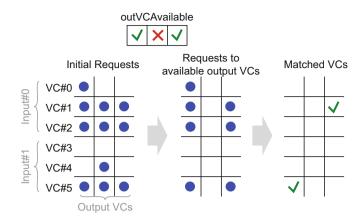

|   |      | 7.1.2 Request Generation for the VC Allocator                                    | 113        |  |

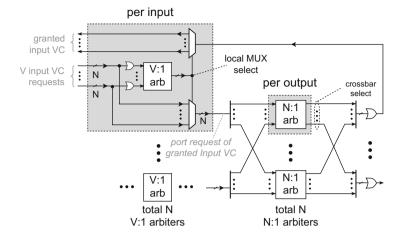

|   |      | 7.1.3 Request Generation for the Switch Allocator                                | 115        |  |

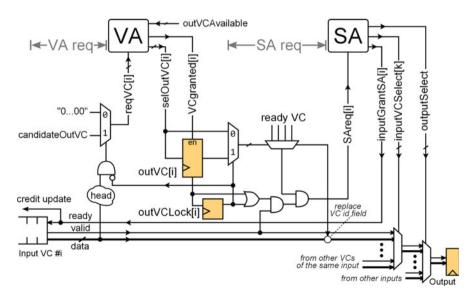

|   |      | 7.1.4 Gathering Grants and Moving to the Output                                  | 117        |  |

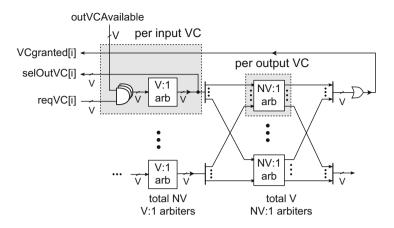

|   |      | 7.1.5 The Internal Organization of the VC Allocator                              |            |  |

|   |      | for a Many-to-One Connection                                                     | 117        |  |

|   |      | 7.1.6 The Internal Organization of the Switch Allocator                          |            |  |

|   |      | for a Many-to-One Connection                                                     | 119        |  |

|   |      | 7.1.7 Output-First Allocation                                                    | 121        |  |

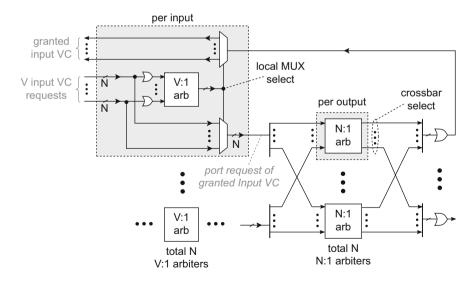

|   | 7.2  | Many-to-Many Connections Using an Unrolled Datapath:                             |            |  |

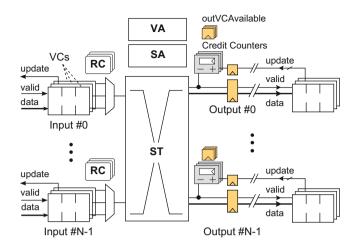

|   |      | A Complete VC-Based Router                                                       | 121        |  |

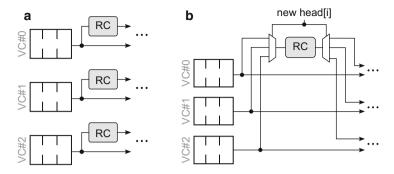

|   |      | 7.2.1 Routing Computation                                                        | 122        |  |

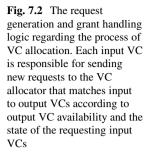

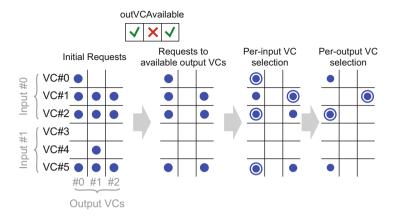

|   |      | 7.2.2 Requests to VC the Allocator                                               | 123        |  |

|   |      | 7.2.3 Requests to the Switch Allocator                                           | 123        |  |

|   |      | 7.2.4 Gathering Grants and Moving to the Output                                  | 126        |  |

|   |      | 7.2.5 The Internal Organization of the VC Allocator                              | 107        |  |

|   |      | for a VC-Based Router                                                            | 127        |  |

|   |      | 7.2.6 The Internal Organization of the Switch Allocator<br>for a VC-Based Router | 120        |  |

|   | 7.3  | VA and SA Built with Centralized Allocators                                      | 129<br>131 |  |

|   | 7.5  | Take-Away Points                                                                 | 131        |  |

|   |      | •                                                                                | 155        |  |

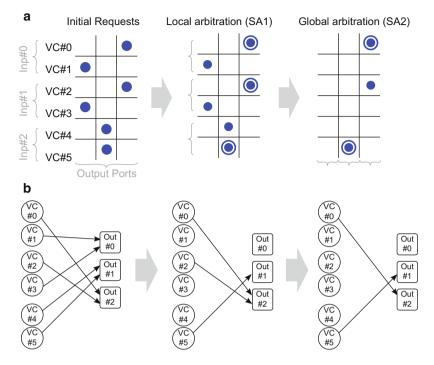

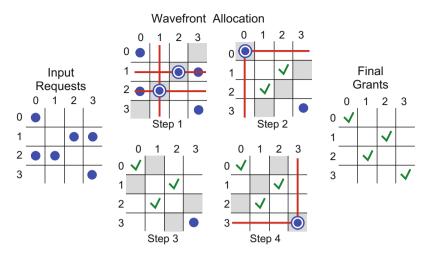

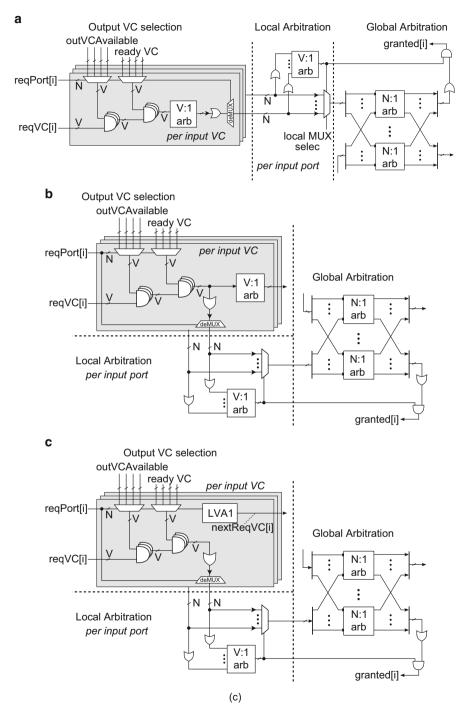

| 8 | Hig  | h-Speed Allocators for VC-Based Routers                                          | 135        |  |

|   | 8.1  | Virtual Networks: Reducing the Complexity of VC Allocation                       | 136        |  |

|   | 8.2  | Lookahead VA1                                                                    | 137        |  |

|   | 8.3  | VC Allocation Without VA2: Combined Allocation                                   | 138        |  |

|   |      | 8.3.1 Combined Allocation with VA1 in Series to SA                               | 139        |  |

|   |      | 8.3.2 Combined Allocation with VA1 in Parallel to SA                             | 139        |  |

|   |      | 8.3.3 Combined Allocation with Lookahead VA1                                     | 141        |  |

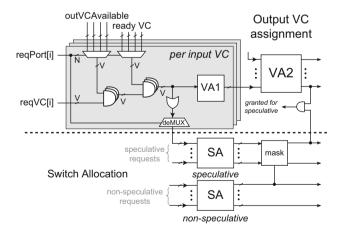

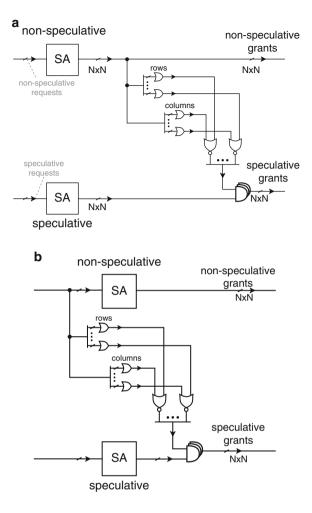

|   | 8.4  | Speculative Switch Allocation                                                    | 141        |  |

|   |      | 8.4.1 Handling the Speculative and the Non-speculative Grants                    | 143        |  |

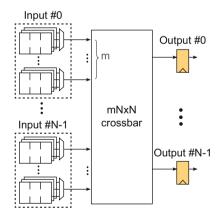

|   | 8.5  | VC-Based Routers with Input Speedup                                              | 145        |  |

|   | 8.6  | Take-Away Points                                                                 | 147        |  |

| 9 | Pipe | lined Virtual-Channel-Based Routers                                              | 149        |  |

|   | 9.1  | Review of Single-Cycle VC-Based Router Organization                              | 150        |  |

|   |      | 9.1.1 Example 1: Two Packets Arriving at the Same                                |            |  |

|   |      | Input VC                                                                         | 151        |  |

|   |      |                                                                                  |            |  |

|         | 9.1.2  | Example 2: Two Packets Arriving at Different           |     |

|---------|--------|--------------------------------------------------------|-----|

|         |        | Input VCs                                              | 152 |

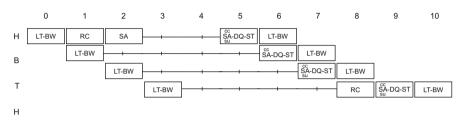

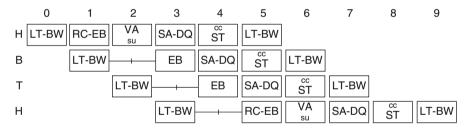

| 9.2     | The R  | outing Computation Pipeline Stage                      | 153 |

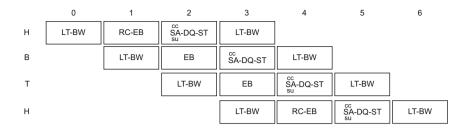

|         | 9.2.1  | Pipelining the Router Only in the Control Path         | 154 |

|         | 9.2.2  | Pipelining the Router in the Control and the Data Path | 155 |

| 9.3     | The V  | C Allocation Pipeline Stage                            | 157 |

|         | 9.3.1  | Example 1: Two Packets Arriving at the Same            |     |

|         |        | Input VC                                               | 158 |

|         | 9.3.2  | Example 2: Two Packets Arriving at Different           |     |

|         |        | Input VCs                                              | 159 |

|         | 9.3.3  | Obstactes in Removing the Deficiency of the VA         |     |

|         |        | Pipeline Stage                                         | 160 |

| 9.4     | The S  | witch Allocation Pipeline Stage                        | 161 |

|         | 9.4.1  | Credit Consume and State Update                        | 162 |

| 9.5     | Multi- | -stage Pipelined Organizations for VC-Based Routers    | 163 |

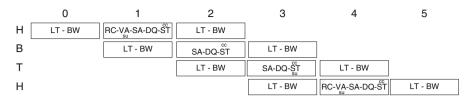

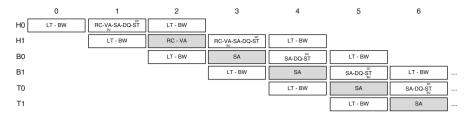

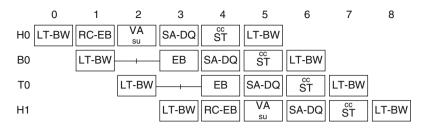

|         | 9.5.1  | Three-Stage Pipelined Organization: RCIVAISA-ST        | 164 |

|         | 9.5.2  | Three-Stage Pipelined Organization: RC–VAISAIST        | 166 |

|         | 9.5.3  | Four-Stage Pipelined Organization: RCIVAISAIST         | 167 |

| 9.6     | Take-  | Away Points                                            | 169 |

|         |        |                                                        |     |

| Referen | ces    |                                                        | 171 |

## Chapter 1 Introduction to Network-on-Chip Design

Computing technology affects every aspect of our modern society and is a major catalyst for innovation across different sectors. Semiconductor technology and computer architecture has provided the necessary infrastructure on top of which every computer system has been developed offering high performance for computationally-intensive applications and low-energy operation for less demanding ones. Innovation in the semiconductors industry provided more transistors for roughly constant cost per chip, while computer architecture exploited the available transistor budget and discovered innovative techniques to scale systems' performance.

We have reached a point where transistor integration capacity will continue to scale, though with limited performance and power benefit. Computer architects reacted to this challenge with multicore architectures. The first systems developed followed an homogeneous architecture, while recent ones move gradually to heterogeneous architectures that look like complex platform Systems-on-Chip (SoCs) integrating in the same chip latency-optimized cores, throughput optimized cores (like GPUs) and some specialized cores that together with the associated memory hierarchies and memory controllers (mostly for off-chip DRAM) allows them to cover the needs of many application domains. SoCs for mobile devices were heterogeneous from the beginning including various specialized components such as display controllers, camera interfaces, sensors, connectivity modules such as Bluetooth, WiFi, FM radio, GNSS (Global Navigation Satellite System), and multimedia subsystems. Programming such heterogeneous systems in a unified manner is still an open challenge. Nevertheless, any revolutionary development in heterogeneous systems programming should rely on a solid computation and communication infrastructure that will aid and not limit the system-wide improvements.

Scalable interconnect architectures form the solid base on top of which heterogeneous computing platforms and their unifying programming environments will be developed; parallelism is all about cooperation that cannot be achieved without the equivalent concurrency in communication. The interconnect implements

A Designer's Perspective, DOI 10.1007/978-1-4614-4301-8\_1

G. Dimitrakopoulos et al., Microarchitecture of Network-on-Chip Routers:

the physical and logical medium for any kind of data transfer and its latency, bandwidth and energy efficiency directly affects overall system performance. Interconnect design is a multidimensional problem involving hardware and software components such as network interfaces, routers, topologies, routing algorithms and communication programming interfaces.

Modern heterogeneous multiprocessing systems have adopted a Network-on-Chip (NoC) technology that brings interconnect architectures inside the chip. The NoC paradigm tries to find a scalable solution to the tough integration challenge of modern SoCs, by applying at the silicon chip level well established networking principles, after suitably adapting them to the silicon chip characteristics and to application demands (Dally and Towles 2001; Benini and Micheli 2002; Arteris 2005). While the seminal idea of applying networking technology to address the chip-level interconnect problem has been shown to be adequate for current systems (Lecler and Baillieu 2011), the complexity of future computing platforms demands new architectures that go beyond physical-related requirements and equally participate in delivering high-performance, quality of service, and dynamic adaptivity at the minimum energy and area overhead (Bertozzi et al. 2014; Dally et al. 2013).

The NoC is expected to undertake the expanding demands of the ever increasing numbers of processing elements, while at the same time technological and application constraints increase the pressure for increased performance and efficiency with limited resources. Although NoC research has evolved significantly the last decade, crucial questions remain un-answered that call for fresh research ideas and innovative solutions. Before diving in the details of the router microarchitecture that is the focus of this book, we will briefly present in this chapter the technical issues involved in the design of a NoC as a whole and how it serves its goal for offering efficient system-wide communication.

#### **1.1 The Physical Medium**

The available resources that the designer has at the physical level are transistors and wires. Using them appropriately the designer can construct complex circuits that are designed at different abstraction levels, following either custom or automated design methodologies. Interconnect architectures should use these resources in the most efficient manner offering a globally optimum communication medium for the components of the system.

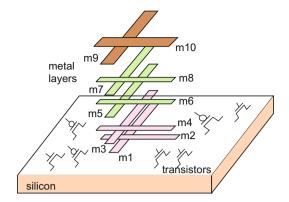

The wires are used as the physical medium for transferring information between any two peers. On-chip wires are implemented in multiple metal layers that are organized in groups (Weste and Harris 2010), as shown in Fig. 1.1. Each group satisfies a specific purpose for the on-chip connectivity. The first metal layers are tailored for local connectivity and are optimized for on-chip connections spanning up to several hundreds of  $\mu$ m. They offer highly dense connections that allow thousands of bits to be transferred in close distance. Upper metal layers, are built

Fig. 1.1 The transistor and the metal layers of an integrated circuit

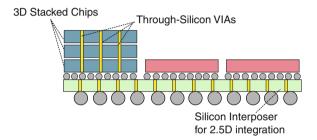

Fig. 1.2 2.5D and 3D integration possibilities for large SoCs

with larger cross sections, that offer lower resistance, and allow transferring bits in longer distance with lower delay. Due to manufacturing limitations upper metal layers should be placed further apart and should have a larger minimum width thus limiting the designer to use less wires per connection bus. Still, the wires that belong to the upper metal layers can be a very useful resource since they allow crossing several mms of on-chip distance very fast (Golander et al. 2011; Passas et al. 2010). In every case, using wisely the density of the upper and the lower metal layers allows for the design of high-bandwidth connections between any two components (Ho et al. 2001).

Technology improvement provides the designer with more connectivity. For example 2.5D integration offers additional across-chip wires with good characteristics allowing fast connections within the same package using the vertical through-silicon vias of a silicon interposer (Maxfield 2012) as depicted in Fig. 1.2. On the other hand, 3D integration promises even more dense connectivity by allowing vertical connections across different chips that are stacked on top of each other offering multiple layers of transistor and metal connections. Instead of allowing stacked chips to communicate using wired connections, short-distance wireless connectivity can be used instead, using, either inductive, or capacitive data transfer across chips (Take et al. 2014). Finally, instead of providing more wiring

connections as is the mainstream approach followed so far, several other research efforts try to provide a better communication medium for the on-chip connections utilizing on-chip optical connections (Bergman et al. 2014).

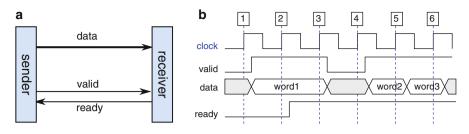

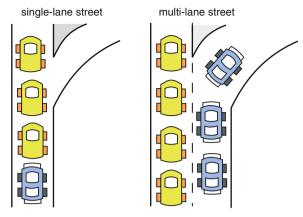

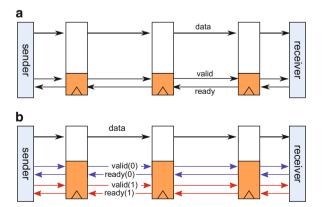

#### 1.2 Flow Control

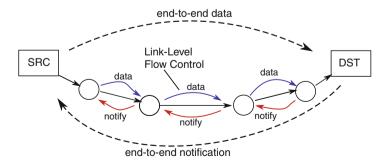

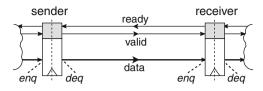

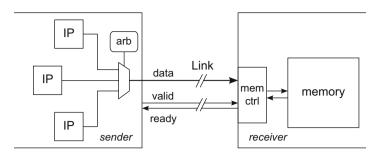

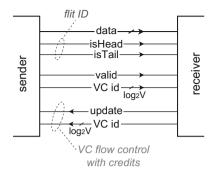

At the system level, using only a set of data wires in a communication channel between two peers (a sender and a receiver module) is not enough. The receiver should be able to distinguish the old data sent by the sender from the new data that it sees at its input. Also, the sender should be informed if the data that has sent has been actually accepted by the receiver or not. Therefore, some additional form of information needs to be conveyed across the sender and the receiver that would allow them to understand when a transaction between them has been completed successfully. Such information is transferred both in the forward and in the backward direction, as depicted in Fig. 1.3, and constitutes the flow-control mechanism.

The flow control mechanism can be limited at the borders of a single wire (called link-level flow control) or it can be expanded between any source and destination possibly covering many links and thus called end-to-end flow control (Gerla and Kleinrock 1980). Figure 1.3 tries to explain graphically the difference between the local and the global flow control mechanisms. While link-level flow control is explicitly implemented by the additional flow control wires of the link, end-to-end flow control can be either explicitly or implicitly implemented in a NoC environment. Explicit implementation requires several flow control wires arriving at each node from different destinations, that each one would describe the status of the corresponding connection. Implicit implementation means that any source or destination node has a mechanism to understand the status of the other side using the normal or special messages transmitted between them. Message transmission in this case, would have used all the intermediate links between the source and destination pair.

Fig. 1.3 Link-level and end-to-end flow control

Flow-control strategies are connected in one or in another way with the availability of buffering positions either at the other end of the link or at the destination. Therefore, the semantics of the flow-control protocol lead to various constraints regarding the implementation of the buffering alternatives.

The messages transferred across any two peers depend on the applications running on the system. Therefore, it is very common the granularity of the messages that are transferred at the application level to be different from the physical wiring resources available on the links. The selection of the channel width depends on a mix of constraints that span from application-level requirements down to physical chip-level integration limitations.

The messages between a source and a destination can be short and fit the channel width or can be longer and need to be serialized to many words that traverse the link in multiple cycles. This attribute should be also reflected to the flow-control mechanism that decides the granularity to which it allocates the channels and the buffers at the receive side. Coarse-grained flow control treats each message (or packet) as an atomic entity, while fine-grained flow control mechanisms operate at the sub-message (sub-packet) level, allowing parts of the message to be distributed to several stages.

#### **1.3 Read–Write Transactions**

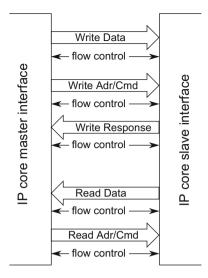

Besides simple data transfers between two IP cores on the same chip, the exchange of information across multiple IP cores requires the implementation of multiple interfaces between them that would allow them to communicate efficiently and implement high-level protocol semantics. In widely accepted interfaces such as AMBA AXI and OCP-IP, each core should implement distinct and independently flow-controlled interfaces for writing, and reading from another IP core, including also interfaces for transferring additional notification messages (ARM 2013; Accelera 2013). An example of two connected cores via a single channel, where each core implements the full set of interfaces needed by AXI is shown in Fig. 1.4.

In most cases, where such address-based load/store transactions are used for the communication of two IPs the interfaces shown in Fig. 1.4 suffice to describe the needed functionality. The implementation of these interfaces and respecting the rules that come with the associated interconnect protocol, e.g., AXI, constitute the transaction layer of the network-on-chip communication architecture. Every transaction is initiated by a core (called the master for this transaction) via the request interface (read or write) and completed via the corresponding reply interface, while it may include an additional transaction response. Each transaction always involves a master and a slave core (that receives and services the request), while the two peers of a transaction are identified by the address used in the request and reply interfaces. Transaction-layer communication is an end-to-end operation between a master and slave and its definition, besides the support for the necessary physical interfaces, does not constrain the designer on how to implement it.

Fig. 1.4 An example of master and slave interfaces as needed by the AXI transaction protocol

#### 1.4 Transactions on the Network: The Transport Layer

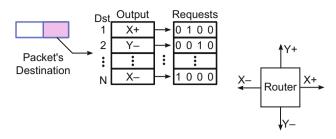

Directly supporting all the interfaces of the transaction layer in all links of the system is an overkill that requires an enormous number of wiring resources. Following the encapsulation principle followed by any network, the required interfaces can be substituted by transport layer interfaces that exchange packets of information that include in their headers the information delivered by each encapsulated interface (Mathewson 2010). Each packet can be either a read or a write packet consisting of a header word and some payload words. The packet header encodes the read/write address of the transaction and all other transaction parameters and control signals included in the original transaction-layer interface. Also, the header signal should include the necessary identification information that would guide the packet to its appropriate destination.

#### 1.4.1 Network Interfaces

Interfacing between the transport and the transaction layer of communication is done at the network interfaces (NIs), located at the NoC periphery. The NI is responsible for both sending packets to the network as well as receiving packets from the network and after the appropriate manipulation to present it to the connected IP core according to the semantics of the transaction-layer interface (Saponara et al. 2014).

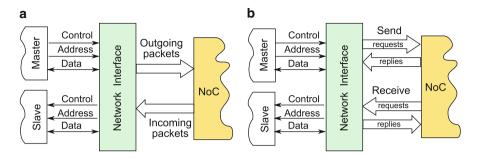

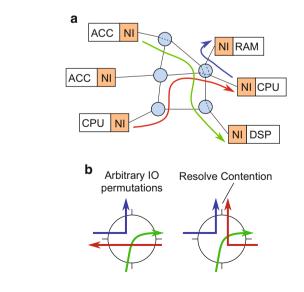

Fig. 1.5 Connection of the network interfaces using (a) simple connections to the network or (b) separate request and reply connections

For example as shown in Fig. 1.5a, the NI connected to a master implements a slave interface, while a NI connected to slave acts as a master to it. At the network's side, the send and receive paths at the edge of the NoC and the NI act as two independent flow-controlled channels that transfer packets according to the rules imposed by the transport layer.

The request and the responses of the transaction layer often assume that they are completely independent and isolated from each other thus eliminating any logical and architectural dependencies and allowing for deadlock-free operation at the transaction-protocol level. Enabling this separation by default at the transaction layers means that the transport and the physical layer provide a packet isolation mechanism. At the transport layer, this means that different packet classes such as request and reply packets should not interfere in the network in such a way that creates dependencies between them that may lead to a deadlock condition.

This can happen by imposing isolation either in space or in time. Isolation in space means that each packet class uses completely separated physical resources (separate request/reply channels, different switching mechanism), e.g., like adding different lanes on a road network for the different types of cars we don't want to interfere (see Fig. 1.5b) (Wentzlaff et al. 2007; Kistler et al. 2006). On the other hand, isolation in time means that different time slots are used by different packet classes. This time-sharing mechanism is equivalent to emulating the different lanes of a road network by virtual lanes, called virtual channels that each one appears at the physical channel in a different time instance (Dally 1992).

Any isolation mechanism implemented either in space or in time can be also used for providing deadlock-free routing for the packets travelling in the network. A routing deadlock can happen when a set of packets request access to already allocated channels and the chain of dependencies evolve in a cyclic manner that blocks any packet from moving forward (Duato et al. 1997).

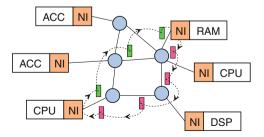

#### 1.4.2 The Network: The Physical Layer

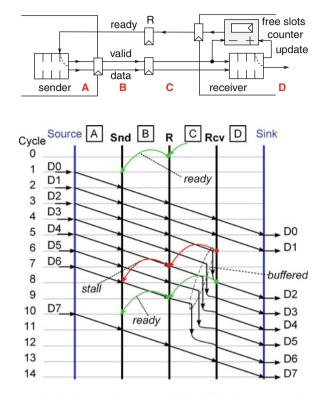

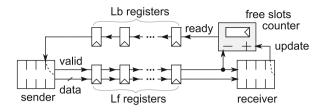

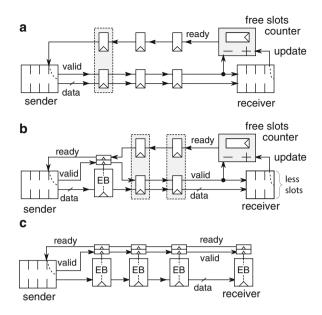

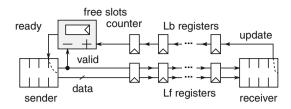

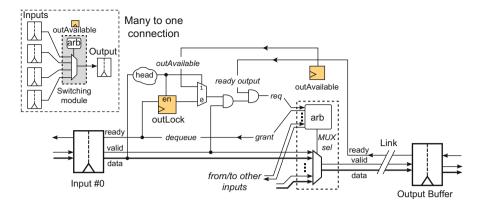

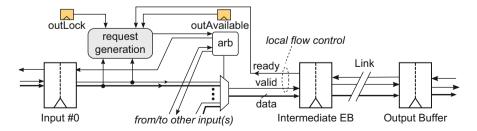

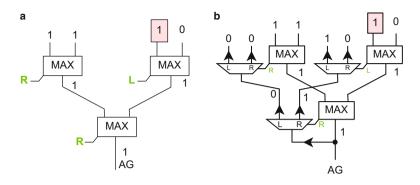

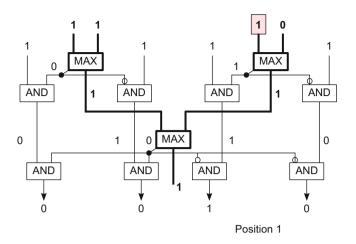

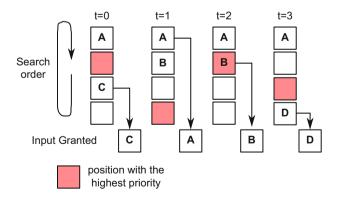

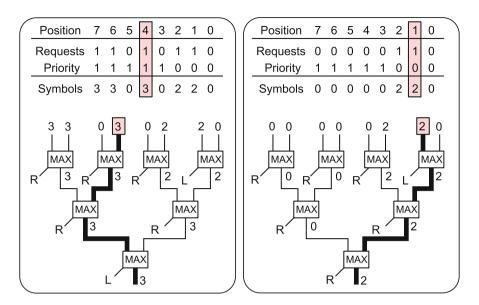

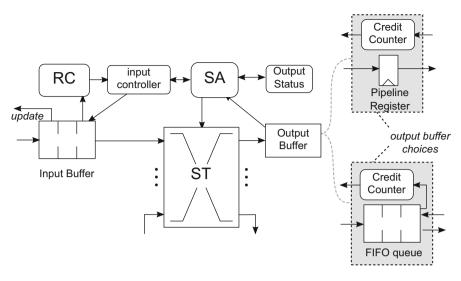

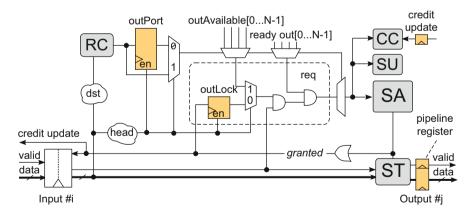

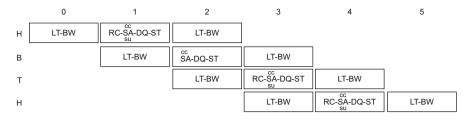

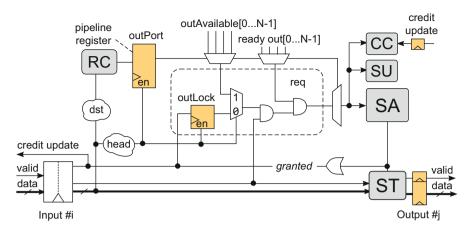

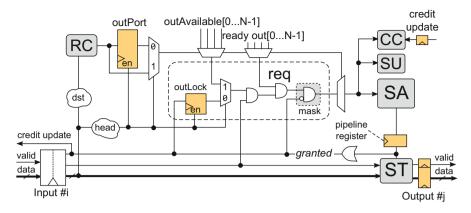

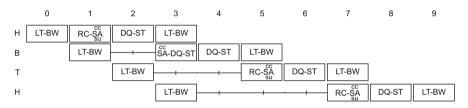

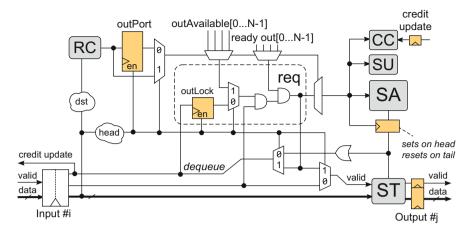

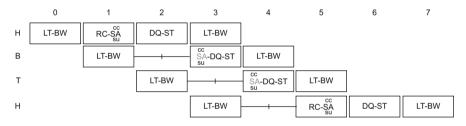

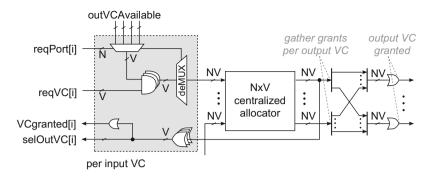

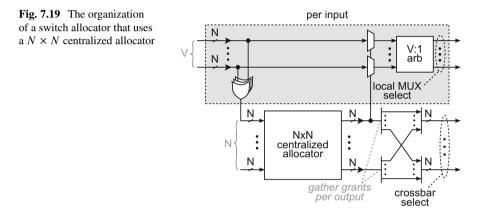

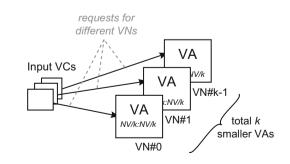

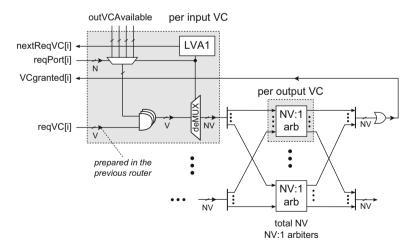

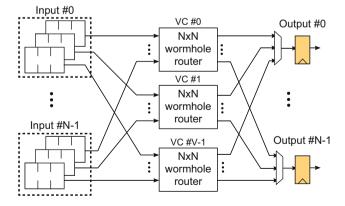

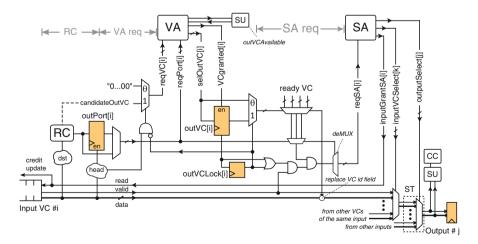

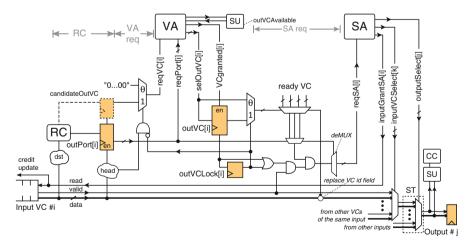

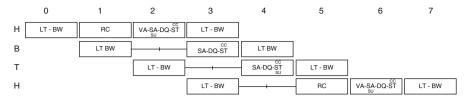

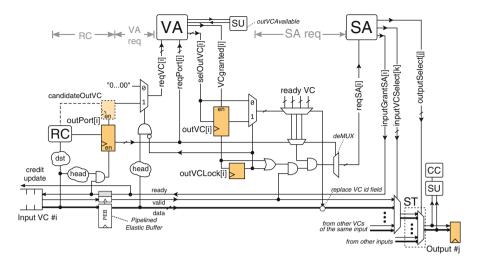

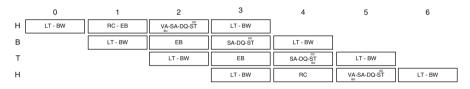

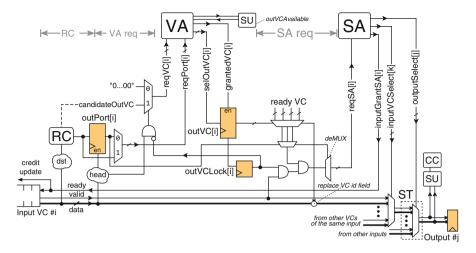

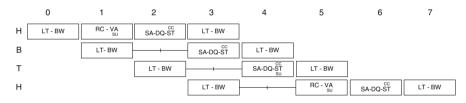

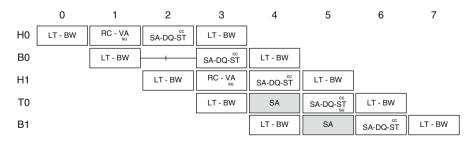

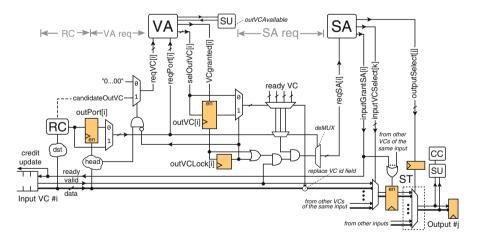

The packets generated by the NIs reach their destination via a network of routers and links that are independently flow-controlled and form an arbitrary topology (Balfour and Dally 2006; Kim et al. 2007). Each router, in parallel to the network links, can connect to one or multiple NIs thus allowing to some of the cores of the system to communicate locally without their data to enter the network (Kumar et al. 2009).