## A 1-V 99-to-75dB SNDR, 256Hz-16kHz bandwidth, 8.6-to-39µW Reconfigurable SC $\Delta\Sigma$ Modulator for Autonomous Biomedical Applications

Serena Porrazzo<sup>1</sup>, Venkata Narasimha Manyam<sup>2</sup>, Alonso Morgado<sup>2,3</sup>, David San Segundo Bello<sup>2</sup>, Chris Van Hoof<sup>2,3,4</sup>, Arthur H.M. van Roermund<sup>1</sup>, Refet Firat Yazicioglu<sup>2</sup> and Eugenio Cantatore<sup>1</sup>

<sup>1</sup> Mixed Signal Microelectronics Group (MSM), Eindhoven University of Technology, Eindhoven, Netherlands

# <sup>2</sup> IMEC, Leuven, Belgium

Abstract— The paper presents a reconfigurable Delta-Sigma Modulator ( $\Delta \Sigma M$ ) suitable for three operation modes, whose application ranges from bio-potential signal monitoring to hearing aids. A feed-forward  $2^{nd}$ -order SC  $\Delta\Sigma M$  architecture with 4-bit quantizer is selected according to an analytic power optimization procedure. The  $\Delta \Sigma M$  features programmable sampling capacitors in the first integrator and novel reconfigurable power-gated OTAs to adjust power consumption in each operation mode. An asynchronous embedded SAR converter implements low-power quantization and passive addition in the feed-forward topology. The prototype is implemented in a 0.18µm CMOS technology and operates from a supply voltage of 1V. Measurements show peak SNDRs from 99 to 75dB for signal bandwidths spanning from 256Hz to 16kHz, achieving figures of merit which are almost constant in the different modes, and range from 0.20 to 0.27pJ/c.s.

#### I. INTRODUCTION

The growing demand of autonomous sensor nodes for biomedical applications requires the development of powerefficient analogue-to-digital converters (ADCs) [1]. There is an on-going trend to design ADCs that are power-scalable (i.e. their power consumption scales with bandwidth and resolution) and maximize energy efficiency in all their operation modes [2]-[12]. Furthermore, reconfigurable ADCs able to address a number of applications are attractive for their high added value and shared development time, while their area can be comparable to that of tailored implementations achieving similar performances. A number of reconfigurable Nyquist ADCs have succeeded in keeping state-of-the-art figure of merit (FoM) for different operation modes [2]-[3], but their resolution is typically below 12 bits, which is a limitation for high-performance bio-medical signal acquisition readouts. Reconfigurable delta-sigma modulators ( $\Delta\Sigma Ms$ ) offer higher resolution, but the solutions reported in literature

<sup>3</sup>KU Leuven, Leuven, Belgium

<sup>4</sup> IMEC/Holst Center, Eindhoven, Netherlands

[4]-[12] till now did not succeed in keeping the FoM minimum and constant in all modes of operation.

This paper presents a feed-forward (FF) 2<sup>nd</sup>-order switched-capacitor (SC)  $\Delta\Sigma M$  with a 4-bit quantizer that can be used for EEG, ECG, EMG and hearing aids. The experimental results show that this  $\Delta \Sigma M$  IC can be configured from 99 to 75dB peak SNDR and 256Hz to 16kHz bandwidth (BW) (see Table I). The power consumption ranges from 8.6 to 39µW, achieving best-in-class figures of merit (from 0.2 to 0.27pJ/c.s.) in the target SNDR range.

RECONFIGURATION STRATEGY FOR MINIMUM POWER П

Table I summarizes the specifications for the different operation modes of the proposed  $\Delta \Sigma M$ : High-Resolution Low-BW (HRLB), Medium-Resolution Moderate-BW (MRMB), and Low-Resolution High-BW (LRHB) modes have been chosen to enable the digitization of bio-potential (EEG, ECG, EMG) and audio signals. Several reconfigurable  $\Delta\Sigma$ Ms exist in literature [4]-[12]. A number of them employ high-order cascade architectures where stages are suitably switched on and off [5]. However, this results in increased power dissipation (to compensate for the mismatch between the cascade analogue and digital circuitry in the first stage, and

TABLE I.  $\Delta\Sigma M$  specifications

|                            | HRLB     | MRMB   | LRHB         |

|----------------------------|----------|--------|--------------|

| Target application         | EEG, ECG | EMG    | Hearing aids |

| ENOB*                      | 16       | 14     | 12           |

| BW                         | 256Hz    | 2048Hz | 16kHz        |

| OSR                        | 128      | 64     | 32           |

| Sampling frequency fs      | 65kHz    | 262kHz | 1.05MHz      |

| First integrator $C_{s,l}$ | 16pF     | 2pF    | 0.5pF        |

| OTAs' GBW                  | 330kHz   | 1.3MHz | 5.2MHz       |

\*ENOB=(SNDR-1 76)/6 02

to power the additional stages) and in area overhead (due to the additional integrators and quantizers in the last stages). Single-loop  $\Delta\Sigma Ms$  can also enable power-efficient reconfigurability by suitably varying OSR, filter order, quantizer resolution, and featuring tunable passive components together with power-scalable analog core blocks [8]. The analitic-based method developed in [13] to design power-efficient single-loop SC  $\Delta\Sigma$ Ms is applied here to determine the power-optimal  $\Delta\Sigma M$  architecture for each operation mode in Table I. After merging the solutions found for the three operation modes and simplifying the hardware to minimize area, the power-vs.-resolution trade-off is optimized by choosing a feed-forward (FF) 2nd-order SC  $\Delta \Sigma M$  architecture with a 4-bit quantizer. Programmable sampling capacitors in the first integrator  $C_{s,l}$  and GBWadjustable OTAs (see Figure 1) are used to scale power consumption in the different operation modes. To meet the required BW and resolution, the sampling frequency is tuned between 65kHz and 1.05MHz, implementing OSRs between 128 and 32.

### III. CIRCUIT IMPLEMENTATION

In our approach to reconfigurability, the sampling capacitors  $C_{s,l}$  and the OTA of the first integrator are programmed to optimize the energy efficiency. Therefore, the  $\Delta\Sigma M$  is designed as thermal-noise-limited in each mode of operation while the equivalent load of the first integrator is minimized. The specifications listed in Table I for  $C_{s,l}$  and for the GBW of OTAs are derived using the analytic approach described in [13] and verified using time-domain behavioural simulations. The  $\Delta\Sigma M$  behavioural model has been built using the blocks described in [14].

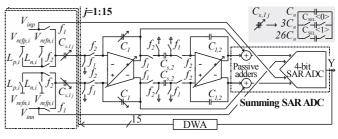

The embedded quantizer combines a 4-bit SAR ADC with passive addition [15] (see Figure 1). The SAR quantizer features a dynamic comparator so that its power automatically scales with the clock frequency. Its operation is asynchronous, so that it does not need an additional highfrequency clock. The programmable OTAs and the multi-bit SC DAC are described with more detail in the next sections.

### A. Modular first-integrator $C_s(C_{s,l})$ implementation

The 4-bit feedback DAC is implemented as a capacitive array of 15 unit elements ( $C_{s,lj}$  in Figure 1). The overall capacitance of  $C_{s,l}$  is thus equal to the sum of the individual capacitances  $C_{s,lj}$ . Each  $C_{s,lj}$  is programmed via two configuration bits,  $C_{SEL} < 0.1 >$ . The largest value of  $C_{s,lj}$  (for the HRLB mode) is implemented by an array of 30 unit elements. Lower resolution modes reuse a subset of units, with no area overhead.

Three techniques are used to improve the linearity of the 4-bit DAC to a level enabling the maximum targeted SNDR. First, a data-weighted averaging (DWA) block is employed to provide a first-order shaping of the mismatch errors in the DAC capacitors [16]. The power of these errors is thus pushed to high frequencies and filtered out by the decimator filter. Second, boosting circuits [17] are used for the switches driven by  $f_1$ ,  $f_2$ ,  $L_{p,i}$  and  $L_{n,i}$  (Figure 1). Indeed, the non-linearity of the switches is mainly due to their input-voltage dependent ON-resistances ( $r_{ON}$ ). An overdrive voltage as

Figure 1. Implementation of the proposed reconfigurable  $\Delta \Sigma M$ .

constant as possible is thus needed to minimize the switch  $r_{ON}$  variation. Finally, transmission gates and a driving voltage larger than  $V_{DD}$  (provided by a separate 1.2-V supply,  $V_{DD,SW}$ ) are used for the static configuration switches driven by  $C_{SEL}$ <0:1> in the programmable sampling capacitors.

#### B. Programmable OTA for power- and speed-scalability

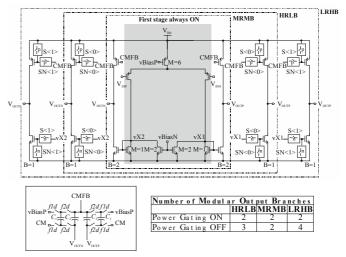

A programmable OTA capable of adapting its static power consumption and GBW to the sampling speed and capacitive load required by each operation mode is used in the first integrator. The most common approach to achieve this in literature consists in choosing a fixed circuit topology, with the input stage biased in weak inversion, and tuning the bias current to scale the GBW [5]. This approach, however, is not suitable for GBWs varying more than 10 times, as required by our specifications (see Table I). Another common approach is to use identical switchable amplifier cells in parallel [8]. In our architecture, we have implemented a new power-efficient gain-enhanced current-mirror OTA in which the input pair is biased with a fixed tail current and is always kept on. The total OTA GBW, which is proportional to the number of modular output branches, is adjusted by switching on/off these branches (Figure 2). A gain-enhanced currentmirror architecture has been chosen, as this arrangement offers high power-efficiency in terms of GBW per unit of current and capacitive load [18]. The gain enhancement technique is used to increase the gain by about 10-20 dB without compromising the BW and with no extra power consumption.

Figure 2. Proposed programmable gain-enhanced current mirror OTA.

The current-mirror OTA is also suitable for a low-voltage design thanks to its wide output swing. The DC gain of this OTA is limited as the amplifier employs a single stage with no cascoding. However, this is not an issue in our  $\Delta \Sigma M$ , as our FF architecture requires only ~40-dB of DC gain. The output branches are sized considering the targeted GBW and the equivalent load specification of each mode. This results in reduced power and smaller area when compared to using identical switchable amplifier cells in parallel [8], since the first stage is here shared among all the configurations. The trade-off between stability and GBW requires however careful design (the nodes associated to the second pole, vX1 and vX2, are loaded by the multiplexers S<0:1> and SN<0:1>). The worst-case phase margin is 70 degrees (in LRHB mode). The first OTA is power-gated during the sampling phase *f1*, to further reduce the static power of the modulator. During the power-gating operation, all switchable output stages of the first OTA are powered down. This results in a power reduction of up to 40% (in LRHB mode) with negligible circuit overhead and without affecting the modulator stability as the common-mode feedback (CMFB) loop is never interrupted.

### IV. MEASUREMENTS RESULTS

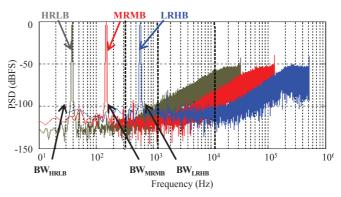

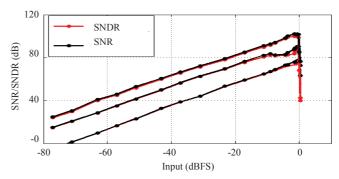

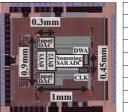

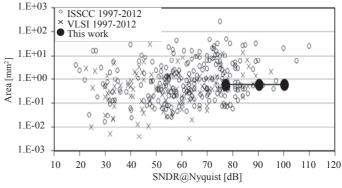

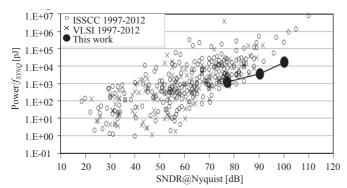

The presented  $\Delta\Sigma M$  is implemented in a standard 0.18µm CMOS process, operates from a 1-V supply and occupies a net area of 0.59mm<sup>2</sup> (Figure 5). Figure 3 shows the measured output spectra in HRLB, MRMB and LRHB modes at the corresponding overload levels. This figure clearly shows a reconfiguration of the noise floor thanks to the adjustment of the sampling capacitors in the first integrator. The power consumption is only 8.6, 15 and 39µW for the HRLB, MRMB and LRHB modes, respectively. The power required from  $V_{DD SW}$  is negligible as this supply only drives static switches  $C_{SEL} < 0.1 >$  in the input SC DAC (see Figure 1). Table II summarizes the achieved performance. Figure 4 depicts the measured SNR/SNDR curves, showing peak SNDRs of 99dB, 87dB, and 75dB in the different modes. Figure 6 and Figure 7 respectively display the area- and power-efficiency benchmarking against state-of-the-art ADCs from [19]. Note that the area occupied by this chip is similar to those achieving similar maximum SNDR (99dB) and optimized for one mode of operation only. This demonstrates the high area efficiency of the proposed strategies for reconfigurability. Figure 7 demonstrates that the implemented  $\Delta \Sigma M$  achieves best-inclass power efficiency in both HRLB and MRMB mode, even when compared to point-optimized solutions. This confirms the effectiveness of the proposed power-reconfiguration and optimization techniques.

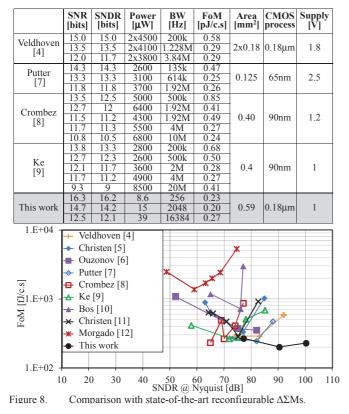

Table III and Figure 8 summarize the overall experimental performance and compares it with state-of-the-art reconfigurable  $\Delta\Sigma$ Ms [4]-[12]. It is important to note here the improved power efficiency and the almost constant FoM (between 0.20 and 0.27pJ/c.s.) achieved while varying the resolution by 4 bits, the signal bandwidth by 64 times and the power consumption by 4.5 times.

Figure 4. Measured SNR/SNDR vs. input amplitude.

TABLE II. SUMMARY OF THE MEASURED PERFORMANCE

0.18µm

1

|                         | HRLB | MRMB | LRHB |

|-------------------------|------|------|------|

| SNR [dB]                | 100  | 90   | 77   |

| SNDR [dB]               | 99   | 87   | 75   |

| Power [µW]              | 8.6  | 15   | 39   |

| BW [Hz]                 | 256  | 2048 | 16k  |

| FoM [pJ/c.s.]           | 0.23 | 0.20 | 0.27 |

| Area [mm <sup>2</sup> ] | 0.59 |      |      |

Figure 5. Chip photograph

CMOS process

Supply [V]

Figure 7. Power-efficiency benchmarking of state-of-the-art  $\Delta\Sigma Ms$  [19].

TABLE III. Summary of performance and comparison with state-of-the-art  $\Delta\Sigma Ms$

#### V. CONCLUSIONS

A 1-V reconfigurable SC  $\Delta\Sigma M$  for autonomous biomedical applications which features several strategies to achieve best in-class power and area efficiency has been presented. The OSR and the capacitance of the first-integrator sampling capacitors are changed to satisfy the specific thermal noise requirements of each operation mode. Power efficiency is guaranteed by using a 2<sup>nd</sup>-order SC architecture with a 4-bit quantizer, together with configurable sampling capacitances (Figure 1) and programmable OTAs, whose GBW and power scale with the required OSR (Figure 2). Power-efficient and power-scalable quantization is achieved using a summing SAR quantizer [15]. As shown in Figure 6, there is no area overhead despite the achieved reconfigurability. The chip achieves best-in-class FoMs both in HRLB and MRMB modes, while the FoM is kept almost constant (between 0.20 and 0.27pJ/c.s.) over the different operation modes (see Figure 7).

### References

- N.Verma, and A. P. Chandrakasan, "An Ultra Low Energy 12-bit Rate-Resolution Scalable SAR ADC for Wireless Sensor Nodes," IEEE J. of Solid-State Circuits, Vol. 42, pp. 1196 - 1205, Jun. 2007.

- [2] H. Zhang, J. Tan, C. Zhang, H. Chen, E. Sanchez-Sinencio, "A 0.6-to-200MSPS speed reconfigurable and 1.9-to-27mW power scalable 10bit ADC," IEEE ESSCIRC Dig. Tech. Papers, pp. 367-370, 2011.

- [3] P. Harpe, Y. Zhang, G. Dolmans, K. Philips, H. de Groot, "A 7-to-10b 0-to-4MS/s flexible SAR ADC with 6.5-to-16fJ/conversion-step," IEEE ISSCC Dig. Tech. Papers, pp. 472-474, 2012.

- [4] R.H. Veldhoven, "A Triple-Mode Continuous-Time ΣΔ Modulator With Switched-Capacitor Feedback DAC for a GSM-EDGE/CDMA2000/UMTS Receiver." IEEE J. of Solid-State Circuits, Vol. 38, pp.2069-2076, Dec. 2003.

- [5] T. Christen, T. Burger, H. Qiuting, "A 0.13μm CMOS EDGE/UMTS/WLAN tri-Mode ΔΣ ADC with -92dB THD," IEEE ISSCC Dig. Tech. Papers, pp. 240-241, 2007.

- [6] S. Ouzounov, R. van Veldhoven, C. Bastiaansen, K. Vongehr, R. van Wegberg, G. Geelen, L. Breems, A. Van Roermund, "A 1.2V 121-Mode CT Delta-Sigma Modulator for Wireless Receivers in 90nm CMOS," IEEE ISSCC Dig. Tech. Papers, pp. 242-243, 2007.

- [7] B. Putter, "A 5th order CT/DT Multi-Mode  $\Sigma\Delta$  Modulator," IEEE ISSCC Dig. Tech. Papers, pp. 244-245, 2007.

- [8] P. Crombez, G. Van der Plas, M. Steyaert, J. Craninckx, "A 500kHz-10MHz multimode power- performance scalable 83-to-67dB DR CT ΔΣM in 90 nm digital CMOS with flexible analog core circuitry," IEEE VLSIC Symp., pp.70-71, 2009.

- [9] Yi Ke, Peng Gao, J. Craninckx, G. Van der Plas, G. Gielen, "A 2.8-to-8.5mW GSM/bluetooth/UMTS/DVB-H/WLAN fully reconfigurable CT $\Delta\Sigma$  with 200kHz to 20MHz BW for 4G radios in 90nm digital CMOS," IEEE VLSIC Symp, pp. 153-154, 2010.

- [10] L. Bos, G. Vandersteen, P. Rombouts, A. Geis, A. Morgado, Y. Rolain, G. Van der Plas, J. Ryckaert, "Multirate Cascaded Discrete-Time Low-Pass  $\Delta\Sigma$  Modulator for GSM/Bluetooth/UMTS," IEEE J. of Solid-State Circuits, Vol. 45, pp. 1198 1208, Jun. 2010.

- [11] T. Christen, H. Qiuting, "A 0.13µm CMOS 0.1–20MHz bandwidth 86– 70dB DR multi-mode DT ΔΣ ADC for IMT-Advanced," IEEE ESSCIRC Dig. Tech. Papers, pp. 414-417, 2010.

- [12] A. Morgado, R. del Rio, J.M. de la Rosa, L. Bos, J. Ryckaert, G. Van der Plas, "A 100kHz–10MHz BW, 78-to-52dB DR, 4.6-to-11mW flexible SC ΣΔ modulator in 1.2-V 90-nm CMOS," IEEE ESSCIRC Dig. Tech. Papers, pp. 418-421, 2010.

- [13] S. Porrazzo, F. Cannillo, C. Van Hoof, E. Cantatore, A.H.M. van Roermund, "A power-optimal design methodology for high-resolution low-bandwidth SC ΔΣ Modulators," IEEE Trans. Instrum. Meas., vol. 61, pp. 2896-2904, Nov. 2012.

- [14] P. Malcovati, "SD Toolbox 2," 2009, http://www.mathworks.de/matlabcentral/fileexchange/25811.

- [15] S. Porrazzo, A. Morgado, D. San Segundo Bello, F. Cannillo, C. Van Hoof, A.H.M van Roermund, E. Cantatore, "A 155 $\mu$ W 88-dB DR discrete-time  $\Delta\Sigma$  Modulator for digital hearing aid applications," IEEE BioCAS Dig. Tech. Papers, pp. 248-251, 2012.

- [16] R. K. Henderson, O. Nys, "Dynamic element matching techniques with arbitrary noise shaping function," IEEE International Symposium on Circuits and Systems, pp. 293-296, 1996.

- [17] A. M. Abo, P. R. Gray, "A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter," IEEE J. of Solid-State Circuits, vol. 34, n. 5, p. 599–606, 1999.

- [18] L. Yao, M. Steyaert, W. Sansen, "A 0.8-V, 8-μW, CMOS OTA with 50-dB gain and 1.2-MHz GBW in 18-pF load," in IEEE ISSCC Dig. Tech. Papers, pp. 297-300, 2003.

- [19] B. Murmann, "ADC Performance Survey 1997-2012," [Online]. Available: http://www.stanford.edu/~murmann/adcsurvey.html.