# A 107 μW MedRadio Injection-Locked Clock Multiplier with a CTAT-biased 126 ppm/°C Ring Oscillator

Somok Mondal and Drew A. Hall University of California, San Diego La Jolla, CA, USA

Abstract—This paper presents a 400 MHz open-loop injection-locked clock multiplier (ILCM) with low-power and fast settling time. A one-time DCO calibration and novel temperature compensation scheme guarantees PVT-robustness without the use of a power-hungry conventional frequency tracking loop (FTL). The compensated ring oscillator exhibits a frequency stability of 126 ppm/°C over the 0 to 55 °C temperature range. This suffices to maintain lock and meet MedRadio specifications as indicated from measurements taken from 20 test chips. The chip was fabricated in 180 nm CMOS and consumes 107 µW from a 0.7 V supply achieving state-of-the-art performance for PVT robust ILCMs operating at a comparable frequency range.

### I. Introduction

Interest in Internet of Things (IoTs) sensor nodes for connected health applications has grown rapidly over the past few years owing to their potential to automate health-monitoring and increase healthcare engagement. A short-range transmitter is a key building block for such sensor nodes that are in constant communication with nearby data-aggressors (e.g., smartphones, smartwatches, etc.). Due to the low output transmission power requirement, the frequency synthesizer used to generate the RF carrier is a power-hungry component in these transmitters rather than the power amplifier as in conventional radios. Low power ring oscillator-based injection-locked clock multipliers (ILCMs) without dedicated frequency tracking loops (FTLs) or phase locked loops (PLLs) have therefore been widely accepted as the state-of-the-art [1–3]. Such open-loop ILCMs also offer fast settling/lock to permit aggressive transmitter duty-cycling [1].

Ideally, an oscillator can be locked to a directly injected reference provided that the free-running frequency is close to the desired harmonic (i.e. within the locking range). In the locked state, the frequency stability and the close-in phase noise are greatly improved. However, in practice, a low-power ring oscillator is very sensitive to PVT variation. Deviations of the nominal frequency from the center of the locking range can degrade the phase noise, increase the reference spur, and even lead to a loss of lock. While earlier work achieved excellent power-efficiency consuming <90 µW for a 400 MHz carrier generation [1], it relied on the oscillator's nominal frequency drift considering PVT variation and layout parasitics to be minimal. As a result, most of the latter works [2–3] perform a one-time calibration of a digitally controlled oscillator (DCO). However, these still rely on the temperature being held constant assuming close proximity to the body. According to the Medical Device Radiocommunications Service (MedRadio) band specifications at ~400 MHz, one needs to maintain a frequency

This work was supported in part by equipment purchased through a DURIP award from the Office of Naval Research (award no. N00014-18-1-2350).

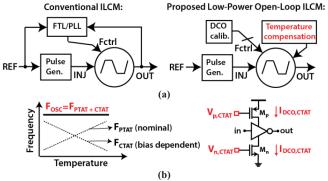

Fig. 1. (a) Conventional and proposed ILCM architectures and (b) proposed temperature compensation principle.

stability of  $\pm 100$  ppm over 0 to 55 °C for body-worn devices and attenuate out-of-band/spurious emissions by 20 dB [4]. Meeting the frequency accuracy and spectral mask regulations across temperature is quite challenging and often not addressed or reported in prior work. Dedicated FTLs are one way to ensure robustness but are power-hungry (e.g., a 200 MHz ILCM in [5] consumes 130  $\mu$ W). While static PV variation can be dealt with by DCO calibration and/or using voltage regulators, it is still important to address the dynamic temperature sensitivity of ring oscillators via alternate means that introduce minimal power overhead for the FTL/PLL-free ILCM, as shown in Fig. 1(a).

This work uses a complementary to absolute temperature (CTAT) biasing technique to compensate the temperature sensitivity of a ring DCO. Measurements taken from test chips (n=20) demonstrate the performance of the proposed technique for ILCMs. All chips remained in the locked state while meeting the MedRadio specifications over the 0 to 55 °C temperature range. The proposed technique is described in Section II and the implementation is presented in Section III. Section IV shows measurement results and a conclusion is drawn in Section V.

# II. TEMPERATURE COMPENSATION PRINCIPLE

Since, nominally a ring oscillator's free running frequency exhibits a positive to absolute temperature (PTAT) characteristic (as explained later), introducing a CTAT characteristic for the frequency control knob (e.g., the bias current in a current-starved delay cell) can be used to counter the temperature dependence. This proposed temperature compensation principle is illustrated in Fig. 1(b). This general concept is fundamental to several temperature insensitive circuits like bandgap references where a PTAT and CTAT quantity are summed to realize temperature independent operation. Temperature compensation techniques for ring oscillators have been explored in several prior works [6–

Fig. 2. Schematic of the injection-locked clock multiplier (ILCM) circuit.

Fig. 3. Schematics of ring DCO's (a) CTAT current generator and (b) pseudo-differential current-starved delay cell.

9]. A low temperature coefficient (TC) in [6] was realized by generating a VCO control voltage to balance out the temperature dependence and process variation of the delay element devices. While similar in concept to this work, the inclusion of a BTJbased circuit to counter the temperature dependence and assist a replica delay cell to generate the compensation voltage requires a higher supply voltage and power. A feedback loop improves the TC in [9] but again has a larger expected power overhead. Alternative low power approaches identify the dominant contributor specific to the design and make it variation insensitive (e.g., using a constant- $g_m$  bias circuit [8] or a constant current bias [7]). However, there can be significant influence of other parameters like load capacitance (especially with the use of minimum channel length devices), thus limiting the applicability of such approaches. Furthermore, all prior work lacks frequency tunability (although some are also process compensated) and are designed for above threshold operation. Frequency tunability is necessary since, in practice, irrespective of process variation, owing to high sensitivity to layout parasitics in low power designs, it is difficult to ensure an absolute frequency of operation. The ring oscillator in this work is compensated to the first-order with corresponding devices operating in low voltage sub-threshold. This first-order compensation suffices for operation over the MedRadio temperature range considering the wide locking ranges associated with ILCMs. The additional circuitry introduced consumes <5% power overhead.

# III. CIRCUIT DESCRIPTION

The circuit implementation and relevant design considerations are discussed below.

## A. ILCM

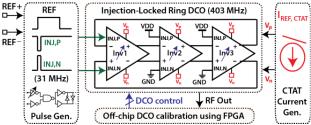

The sub-harmonically injection-locked clock multiplier circuit is shown in Fig. 2. A standard pulsed injection technique

Fig. 4. Simulated free-running ring oscillator's (a) nominal TC with different topologies and (b) TC at corners with proposed topology

has been adopted. The 8-bit DCO is designed to have a  $\pm 25\%$  tuning range and realized by a 3-stage ring with temperature compensation. The DCO is controlled using an off-chip FPGA for the initial calibration similar to [2] to bring the oscillator within the locking range.

# B. CTAT current generation

The circuit to generate a CTAT current is shown in Fig. 3(a). Diode-connected PMOS transistors operating in sub-threshold are stacked to generate a CTAT reference voltage  $V_{\rm b,CTAT}$  [10]. Depending on N, the relative sizing between adjacent stacked transistors, it can be shown that

$$V_{\rm b,CTAT} = -\frac{\eta V_{\rm T} \ln(N)}{2} + \frac{V_{\rm DD}}{4},$$

(1)

where  $\eta$  is the sub-threshold slope factor,  $V_{\rm DD}$  is the supply voltage and  $V_{\rm T}$  is the thermal voltage (directly proportional to the temperature). This voltage is thereafter used to generate a CTAT reference current  $I_{\rm REF,CTAT} = V_{\rm b,CTAT} / R_{\rm b}$ , using an opamp-based feedback circuit with  $R_{\rm b}$  setting the current.  $R_{\rm b}$  is implemented with a 1 M $\Omega$  poly-resistor that also exhibits a PTAT TC which adds to the overall CTAT TC of the reference current. With N=24, the TC of  $V_{\rm b,CTAT}$  dominates and  $R_{\rm b}$  contributes negligibly. Due to the low bandwidth requirement, the opamp is implemented with a two-stage miller compensated topology and consumes only 2  $\mu$ W while the reference ladder consumes  $0.4~\mu$ W.

# C. Delay Cell

The delay cell for the ring oscillator is realized with a current-starved topology as shown in Fig. 3(b). A standard pseudo-differential implementation with an output cross-coupled latch immune to common-mode noise (e.g., from the low power CTAT bias) was chosen. Arrays of switchable tail sources drive each delay cell with a CTAT current  $I_{\text{DCO},\text{CTAT}} = I_{\text{DCO}}[k](1 - \alpha_{\text{I}}\Delta T)$  where  $I_{\text{DCO}}[k]$  is the DCO nominal current at the  $k^{\text{th}}$  mode and  $\alpha_{\text{I}}$  is the associated CTAT TC. Additional inverters (using  $M_{\text{ip,in}}$  in Fig. 3(b)) realize the injection devices.

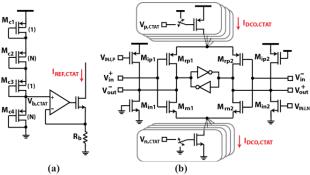

# D. Temperature Sensitivity

The oscillation frequency  $f_{\rm osc}$  of the current-starved ring DCO is mostly determined by the bias current  $I_{\rm DCO,CTAT}$  and the effective load capacitance  $C_{\rm L}$  of each stage. The bias current, if implemented as transistors with a constant voltage bias such as the supply voltage in [2], exhibits a poor TC. This can be further exacerbated in sub-threshold operation with the current  $I_{\rm D}$

Fig. 5. Measured ring oscillator temperature sensitivity (a) across multiple chips and (b) across multiple DCO modes.

20 Temperature (°C)

-20

Fig. 6. Distributions across 20 chips of (a) oscillation frequencies and (b) maximum frequency deviation over temperature.

being  $I_S \cdot \exp(V_{GS}/V_T)$  where  $V_{GS}$  is the transistor gate-source voltages and  $I_S$  is the reverse saturation current which is proportional to  $V_T^2$  resulting in a strong PTAT characteristic. The simulation results shown in Fig. 4(a) indicate that using a constant ideal current as the reference reduces the TC from 3,700 to 740 ppm/°C compared to the constant voltage bias. This is however still poor due to  $C_L$ . Both the junction and the MOSFET oxide capacitance exhibit a negative TC [6], [11] such that  $C_L = C_{L0}(1 - \alpha_C \Delta T)$  where  $\alpha_C$  is the capacitor's CTAT TC and thus contributes to a PTAT behavior for  $f_{osc}$ . Junction capacitances typically have worse TC compared to their oxide counterparts and are significant here due to drain connections to the injection devices and the cross-coupled latch at the delay cell output. With the proposed compensation, the overall  $f_{osc}$  is

$$f_{\rm osc} \propto \frac{I_{\rm DCO,CTAT}}{C_{\rm L}} = \frac{I_{\rm DCO}[k](1 - \alpha_{\rm I}\Delta T)}{C_{\rm L0}(1 - \alpha_{\rm C}\Delta T)}.$$

(2)

A temperature insensitive  $f_{osc}$  is attained when there is a cancellation of the TCs. This cancellation occurs irrespective of  $I_{DCO}[k]$  implying that the temperature compensation is valid over multiple DCO modes. The compensation functionality also holds over process corners, as shown in Fig. 4(b).

Fig. 7. Annotated chip micrograph.

TABLE I - RING OSCILLATOR SUMMARY AND COMPARISON

|             | [7]     | [9]        | [8]        | This Work               |

|-------------|---------|------------|------------|-------------------------|

| Technology  | 90 nm   | 180 nm     | 130 nm     | 180 nm                  |

| Supply (V)  | 1       | 1.2        | 3.3        | 0.7                     |

| Frequency   | 1.8 GHz | 10 MHz     | 1.25 GHz   | 400 MHz                 |

| Fosc Tuning | ×       | ×          | ×          | ✓ via DCO               |

| TC (ppm/°C) | 85      | 67         | 340        | 198 <sup>1</sup>        |

|             |         |            |            | 126 <sup>2</sup>        |

| Temp Range  | 7 to 62 | -20 to 100 | -40 to 120 | -40 to 100 <sup>1</sup> |

| (°C)        | / 10 62 | -20 to 100 | -40 to 120 | 0 to 55 <sup>2</sup>    |

| Power       | 87 μW   | 80 μW      | 11 mW      | 93 μW                   |

1 - Full temperature range; 2- MedRadio temperature range

### IV. MEASUREMENT RESULTS

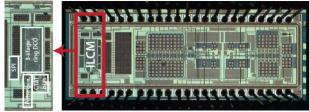

Measurement results from the clock multiplier fabricated in a 180 nm CMOS process occupying 100  $\mu$ m  $\times$  300  $\mu$ m active area are presented below. Operated at  $V_{\rm DD} = 0.7$  V, the ILCM realizes a 13× frequency multiplication to generate a MedRadio-band carrier at 403 MHz from a 31 MHz reference.

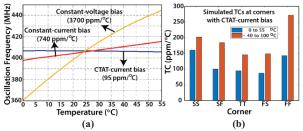

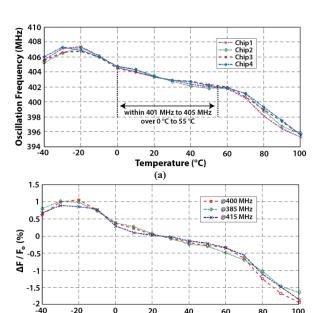

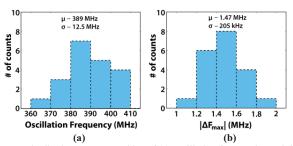

The measured free-running frequency of the ring oscillator (tuned initially to  $F_0 = 403$  MHz, where  $F_0$  is the frequency at 25 °C) versus temperature are shown in Fig. 5(a) for multiple chips (n=4). These measurements correspond to an average TC of 198 ppm/°C across the -40 to 100 °C range. Notably, the plots also indicate that the oscillation frequency always remains within 401-405 MHz across  $\Delta T_{\rm Med}$  (0 to 55 °C range) with an average TC of 126 ppm/°C. The consistency of the temperature compensation at different DCO modes is illustrated in Fig. 5(b). Typical normalized frequency deviations  $\Delta F/F_0$  ( $\Delta F$  is the deviation from  $F_0$ ) for the same DCO tuned to different values of  $F_0$  (385, 400, and 415 MHz) exhibit similar characteristics versus temperature. Statistics of measurements taken over 20 chips are shown in the histogram plots for the free-running oscillation frequency in Fig. 6(a) and the maximum frequency deviation  $\Delta F_{\text{max}}$  occurring over  $\Delta T_{\text{Med}}$  with  $F_0$  as 403 MHz in Fig. 6(b). The former indicates the need for an initial calibration of the DCO frequency and the  $\pm 2$  MHz frequency bound across  $\Delta T_{\rm Med}$  indicated in the latter ensures robust operation of the ILCM. Finally, the standalone performance of the oscillator is summarized along with prior temperature compensated ring oscillators in Table I. Compared to prior art, the proposed oscillator has additional features for digital frequency control, supports injection signals, and operates at a low supply voltage. An annotated die photo is shown in Fig. 7.

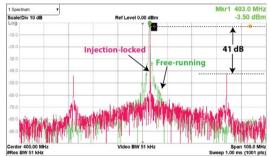

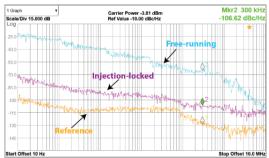

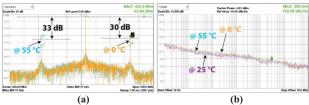

The measured output spectrum of the injection-locked ring oscillator (ILRO) corresponding to a 403 MHz carrier wave generation is shown in Fig. 8. The carrier-to-spur ratio (CSR) is 41 dB meeting the MedRadio spectral mask regulation of 20 dB. Also shown is an overlaid plot of the free-running spectrum for comparison. The measured phase noise plots for the injected reference, the frequency multiplier output at both the locked

Fig. 8. Measured oscillator output spectrum in locked and unlocked states.

Fig. 9. Measured phase noise of the injected reference and oscillator output in locked and unlocked states.

Fig. 10. Measured (a) spectrum and (b) phase noise for the worst cases over 0 to 55  $^{\circ}\mathrm{C}$  temperature variation.

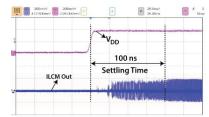

and unlocked states are shown in Fig. 9. As illustrated, injection locking significantly improves the close-in phase noise of the frequency multiplier output (-106.6 dBc/Hz at a 300 kHz offset). Furthermore, to establish the robustness of the ILCM over temperature variation, spectra corresponding to the worst cases in terms of the CSR at either 0 or 55 °C endpoints measured among all 20 chips are shown in Fig. 10(a) and the corresponding phase noise plots in Fig. 10(b). The worst-case CSR was observed to be 30 dB and meets the spectral mask with enough margin. The phase noise remains good with only a degradation to -103.6 dBc/Hz. Additionally, corresponding to these worst-case chips, the measured frequency range over which CSR remains larger than 20 dB extends from 399.6 to 406.5 MHz while the locking range spans 395.9 to 409.6 MHz. Fast settling, typically <100 ns across  $\Delta T_{\rm Med}$  (crucial to duty-cycling), was also measured as shown in Fig. 11. Table II provides a performance summary of the proposed work with a comparison to relevant ILCMs. This work achieves state-of-the-art performance consuming 107 μW with PVT-robust RF carrier generation at such frequencies.

# V. CONCLUSION

An ILCM intended for a low-power, duty-cycled transmitter is presented. Robustness with open-loop operation is enabled with the aid of a temperature compensated 126 ppm/°C ring

Fig. 11. Measured ILCM settling time with a step voltage on the supply.

TABLE II – ILCM SUMMARY AND COMPARISON

|                         | [5]            | [2]              | [1]                          | [12]            | This Work           |

|-------------------------|----------------|------------------|------------------------------|-----------------|---------------------|

| Tech.                   | 65 nm          | 65 nm            | 90 nm                        | 65 nm           | 180 nm              |

| Supply (V)              | 1.1            | 0.8              | 0.7                          | 1               | 0.7                 |

| Topology                | ILRO<br>+ FTL  | ILRO<br>+ calib. | ILRO<br>+EC                  | PLL             | TC-ILRO<br>+ calib. |

| Freq. (MHz)             | 200            | 900              | 400                          | 402             | 403                 |

| Multiplier              | 20 ×           | 9 ×              | 9 ×                          | 1340 ×          | 13 ×                |

| Phase noise<br>(dBc/Hz) | -95**<br>@300k | -100.8<br>@1M    | -105.2<br>@300k              | -102.1<br>@200k | -106.6<br>@300k     |

| CSR (dB)                | 43             | 56#              | 44#                          | 45              | 41# 30*             |

| Settling time           | -              | 88 ns            | 250 ns                       | 350 μs          | 100 ns              |

| Power (µW)              | 130            | 538              | <90                          | 430             | 107                 |

| PVT-robust?             | P✓ V✓ T✓       | P✓ V✓ T×         | $P \times V \times T \times$ | P✓ V✓ T✓        | P✓ V✓ T✓            |

TC-ILRO: Temperature compensated injection-locked ring oscillator; EC: Edge combiner;

\*\*From reported PN plot; \*Nominal value at room/single temperature;

\*Across MedRadio temperature range (meeting 20 dB regulation)

DCO. The technique based on a CTAT biased delay cell can also assist ILCMs with FTLs by relaxing the frequency tracking requirements. This ILCM satisfies all MedRadio specifications while consuming just 107  $\mu W$  and has 100 ns start-up time.

# REFERENCES

- J. Pandey et al., "A Sub-100 W MICS/ISM Band Transmitter Based on Injection-Locking and Frequency Multiplication," *IEEE JSSC*, vol. 46, no. 5, pp. 1049–1058, May 2011.

- [2] X. Liu et al., "A 13 pJ/bit 900 MHz QPSK/16-QAM Band Shaped Transmitter Based on Injection Locking and Digital PA for Biomedical Applications," *IEEE JSSC*, vol. 49, no. 11, pp. 2408–2421, Nov. 2014.

- 3] C. Ma et al., "A Near-Threshold, 0.16 nJ/b OOK-Transmitter With 0.18 nJ/b Noise-Cancelling Super-Regenerative Receiver for the Medical Implant Communications Service," *IEEE TBioCAS*., vol. 7, no. 6, pp. 841–850. Dec. 2013.

- [4] "Medical Device Radio Communications Service," in *Electronic Code of Federal Regulations (e-CFR)*, vol. Title 47, Chapter I, Subchapter D, Part 95, Oct. 2018.

- [5] W. Li et al., "A 200Mb/s inductively coupled wireless transcranial transceiver achieving 5e-11 BER and 1.5pJ/b transmit energy efficiency," in *IEEE ISSCC Digest*, 2018, pp. 290–292.

- [6] K. Sundaresan et al., "Process and Temperature Compensation in a 7-MHz CMOS Clock Oscillator," *IEEE JSSC*, vol. 41, no. 2, pp. 433– 442. Feb. 2006.

- [7] X. Zhang et al., "A Low-Power, Process-and- Temperature-Compensated Ring Oscillator With Addition-Based Current Source," IEEE TCAS-I., vol. 58, no. 5, pp. 868–878, May 2011.

- [8] K. R. Lakshmikumar et al., "A Process and Temperature Compensated Two-Stage Ring Oscillator," in 2007 IEEE CICC, 2007, pp. 691–694.

- J. Lee et al., "A 10MHz 80μW 67 ppm/°C CMOS reference clock oscillator with a temperature compensated feedback loop in 0.18μm CMOS," Symposium on VLSI Circuits, 2009, pp. 226–227.

- [10] M. Choi et al., "A 23pW, 780ppm/°C resistor-less current reference using subthreshold MOSFETs," ESSCIRC, 2014, pp. 119–122.

- [11] W. Liu et al., "BSIM3v3.2 MOSFET model user's manual," The Regents of the University of California, 1998

- [12] J. Yang et al., "A Low Power MICS Band Phase-Locked Loop for High Resolution Retinal Prosthesis," IEEE TBioCAS, vol. 7, no. 4, pp. 513-525, Aug. 2013.