### ISSCC 2012 / SESSION 18 / INNOVATIVE CIRCUITS IN EMERGING TECHNOLOGIES / 18.1

# 18.1 Insole Pedometer with Piezoelectric Energy Harvester and 2V Organic Digital and Analog Circuits

Koichi Ishida<sup>1</sup>, Tsung-Ching Huang<sup>1</sup>, Kentaro Honda<sup>1</sup>, Yasuhiro Shinozuka<sup>1</sup>, Hiroshi Fuketa<sup>1</sup>, Tomoyuki Yokota<sup>1</sup>, Ute Zschieschang<sup>2</sup>, Hagen Klauk<sup>2</sup>, Gregory Tortissier<sup>1</sup>, Tsuyoshi Sekitani<sup>1,3</sup>, Makoto Takamiya<sup>1</sup>, Hiroshi Toshiyoshi<sup>1</sup>, Takao Someya<sup>1,3</sup>, Takayasu Sakurai<sup>1</sup>

<sup>1</sup>University of Tokyo, Tokyo, Japan <sup>2</sup>Max Planck Institute for Solid-State Research, Stuttgart, Germany <sup>3</sup>JST/ERATO, Tokyo, Japan

Energy harvesting is an enabling technology for realizing an ambient power supply for wireless sensor nodes and mobile devices. By using flexible photovoltaic cells and piezoelectric films, we can readily harvest ambient energy if flexible energy harvesters can be realized. Conventional silicon circuits, however, are not best suited to realizing flexible large-area energy harvesters because they are not mechanically conformable to uneven surfaces such as shoes. To address this challenge, we propose an organic insole pedometer with a piezoelectric energy harvester in this paper as the first step toward ambient energy harvesting using organic flexible electronics.

The main challenge in the design of organic circuits for piezoelectric energy harvesting is the robust operation of PMOS-only circuits at a low supply voltage. In energy-harvesting applications, the harvested power is small and the rectified voltage is low (e.g., 2V). In organic circuit design, PMOS-only circuits are often used, because the mobility of PMOS transistors is much higher than that of NMOS transistors in our process. The operation of PMOS-only circuits is not robust and the noise margin is small because of their rationed-logic nature. A Pseudo-CMOS inverter that consists of four PMOS transistors [1] has high gain, but it requires a negative voltage bias. In energy-harvesting applications, however, a single power supply is typical. Therefore, in this work, to increase the noise margin of PMOS-only logic circuits, a negative voltage is generated by a charge pump and is applied as the bias of Pseudo-CMOS inverters. We use a 2V PMOS process with self-aligned monolayer (SAM) technology [2] and DNTT [3] for PMOS transistors.

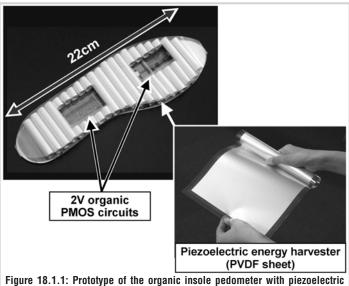

Figure 18.1.1 shows a photograph of the proposed insole pedometer including the piezoelectric energy harvester and the 2V organic PMOS rectifier and counter. A polyvinylidene difluoride (PVDF) sheet is used as the piezoelectric energy harvester. Twenty-one rolls of PVDF film are embedded in the insole. Each time the insole is pressed by the foot during walking, the harvested energy is rectified by the organic rectifier and the number of the steps is counted by the organic counter.

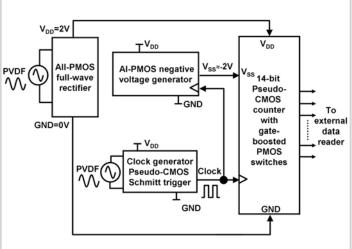

Figure 18.1.2 shows a block diagram of the proposed organic insole pedometer. It consists of four circuit blocks. The all-PMOS full-wave rectifier supplies a voltage  $V_{DD}$  of approximately 2V to all circuit blocks. In the clock generator, the output of the PVDF harvester is half-wave-rectified and a Schmitt trigger inverter converts the half-wave-rectified signal into a clock signal. The generated clock signal is sent to both the PMOS negative voltage generator and a 14-bit Pseudo-CMOS counter with gate-boosted PMOS switches. The negative voltage generator supplies a voltage  $V_{SS}$  (e.g., -2V) to the counter.

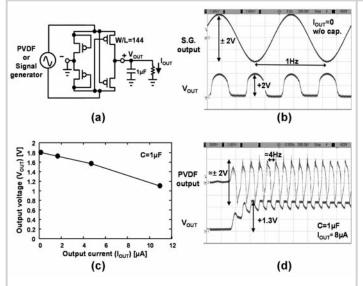

Figure 18.1.3(a) shows a schematic of the all-PMOS full-wave rectifier [4]. A 100V sinusoidal wave was rectified in [4], while a 2V sinusoidal wave is rectified in this work. Figure 18.1.3(b) shows the measured waveform of the 2V full-wave rectifier without a smoothing capacitor. The output is open and the output amplitude of the rectifier is approximately 2V with 1Hz, 4V peak-to-peak sinusoidal input signals. Figure 18.1.3(c) shows the measured output voltage versus the output current of the rectifier with a 1 $\mu$ F smoothing capacitor. The proposed PMOS rectifier (W/L of each transistor is 144) can provide a power of at least 10 $\mu$ W to the circuit. Figure 18.1.3(d) shows the measured waveforms for a 20×28cm² sheet of PVDF energy harvester and the rectified output. The 1 $\mu$ F smoothing capacitor can be charged by providing a mechanical force to the PVDF energy harvester.

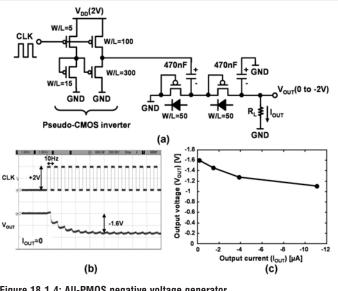

Figure 18.1.4(a) shows a schematic of the proposed all-PMOS negative voltage generator, which consists of a Pseudo-CMOS inverter [1], two diode-connected

PMOS transistors, and two MIM capacitors. To charge the left capacitor, the output buffer of the Pseudo-CMOS inverter consists of transistors with width of 2mm (W/L=100) and 6mm (W/L=300). The performance of the negative voltage generator strongly depends on the threshold voltage of the PMOS diode-connected transistors. To reduce the reverse leakage current, the gate width of each diode-connected transistor is smaller (W/L=50) than that of the inverter. The measured waveforms and output voltage versus the output current are shown in Figs. 18.1.4(b) and 18.1.4(c), respectively. The output voltage ( $V_{OUT}$ ) of the negative voltage generator is -1.6V in the case of 10Hz clock pulses and can provide a power of at least  $10\mu W$  power to the load circuit.

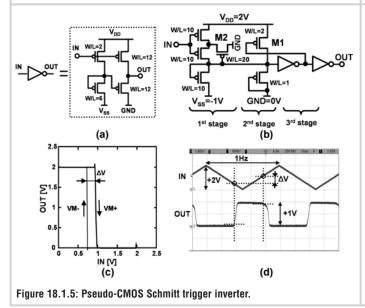

To generate clean clock signals from noisy input signals using the PVDF energy harvester, a PMOS-only Schmitt trigger inverter based on pseudo-CMOS logic is proposed. Figure 18.1.5 shows the schematics and output waveforms of the proposed Schmitt trigger inverter. Unlike conventional CMOS Schmitt trigger inverters that can use both PMOS and NMOS transistors to generate hysteresis. in the proposed PMOS-only Schmitt trigger inverter, the first stage is used to adjust the lower bound (VM-) of the hysteresis, while the second stage is for adjusting the upper bound (VM+). When the input signal is swept from low to high, the top PMOS transistor of the second stage (M<sub>1</sub>), which is controlled by the third-stage Pseudo-CMOS inverter output, pushes the high-to-low switching point toward the right, as can be seen in Fig. 18.1.5(c); on the other hand, when the input is swept from high to low, the ground-connected PMOS transistor (M<sub>2</sub>) of the first stage weakens the pull-up force of the top two PMOS transistors, which forces the low-to-high switching point to move toward the left and widen the hysteresis, as shown in Fig. 18.1.5(c). On the basis of the measured waveform in Fig. 18.1.5(d), we can find that the switching points for the high-to-low and low-to-high transients have approximately 0.3V difference, and this characteristic plays a key role in supplying clean clock signals for the counter.

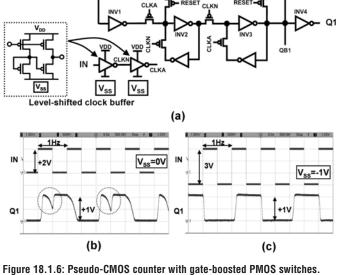

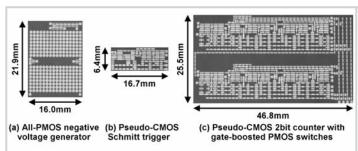

Figure 18.1.6 shows the schematics and measured waveforms of a single-stage 2V Pseudo-CMOS binary counter with asynchronous reset. By connecting fourteen such stages, we can build a 14-bit binary counter for the proposed pedometer. On the basis of a divide-by-two frequency divider, a new gate-boosting technique is applied in this counter to compensate for the poor conductivity of PMOS-only transmission gates. By employing a level-shifted clock buffer, as shown in Fig. 18.1.6(a), we can effectively overdrive PMOS transmission gates by applying negative voltages though the V<sub>SS</sub> terminal in the clock buffer. Compared with Fig. 18.1.6(b), where the gate-boosting technique is not applied and the PMOS transmission gates suffered from poor conductivity, the output waveform of the gate-boosted counter in Fig. 18.1.6(c) is clean owing to the larger clock signal swing from  $\rm V_{DD}$  to  $\rm V_{SS}.$  Note that Fig. 18.1.6 only shows the signals from output Q1, while QB1 is used for connecting to the next stage of the binary counter. Figure 18.1.7 shows photographs of the organic circuits and summarizes their key features. The organic insole pedometer consists of 462 transistors and its size is 22×7cm2.

#### Acknowledgement:

This study was partially supported by JST/CREST and Special Coordination Funds for Promoting and Technology. We also thank Prof. K. Takimiya of Hiroshima Univ. and Drs. H. Kuwabara and M. Ikeda of Nippon Kayaku Co., Ltd., for high-purity DNTT.

#### References:

[1] T.-C. Huang, et al., "Pseudo-CMOS: A Design Style for Low-Cost and Robust Flexible Electronics," *IEEE Transactions on Electron Devices*, vol. 58, no. 1, pp. 141-150, Jan. 2011.

[2] H. Klauk, et al., "Ultralow-power organic complementary circuits," *Nature*, vol. 445, pp. 745-748, Feb. 2007.

[3] T. Yamamoto and K. Takimiya, "Facile Synthesis of Highly  $\pi$ -Extended Heteroarenes,

Dinaphtho[2,3-b:2',3'-f]chalcogenopheno[3,2-b]chalcogenophenes, and Their Application to Field-Effect Transistors," *Journal of American Chemical Society*, vol. 129, no. 8, pp. 2224-2225, Aug. 2007.

[4] Koichi Ishida, et al., "100V AC Power Meter System-on-a-Film (SoF) Integrating 20V Organic CMOS Digital and Analog Circuits with Floating Gate for Process Variation Compensation and 100V Organic PMOS Rectifier," *ISSCC Dig. Tech. Papers*, pp. 218-219, Feb. 2011.

energy harvester and 2V digital and analog circuits.

Figure 18.1.2: System block diagram of the organic insole pedometer.

Figure 18.1.3: 2V organic all-PMOS rectifier.

Figure 18.1.4: All-PMOS negative voltage generator.

DIGEST OF TECHNICAL PAPERS •

## **ISSCC 2012 PAPER CONTINUATIONS**

| Organic                        | transistors                           |

|--------------------------------|---------------------------------------|

| Semiconductor material         | DNTT(1.0 cm <sup>2</sup> /Vs)         |

| Gate oxide material, thickness | SAM* 2nm + AlOx 4nm = 6nm             |

| Minimum gate length            | 20μm (analog), 50μm (digital)         |

| Energy harves                  | ter and pedometer                     |

| Harvester                      | Piezoelectric energy harvester (PDFV) |

| Number of transistors          | 462Tr.                                |

| Pedometer size                 | 22x7cm <sup>2</sup>                   |

\*SAM: Self assembled monolayer

Figure 18.1.7: Photographs and key features.