挑战Hard模式丨摩尔精英“封装半日课”在这里等你

点开可查看大图

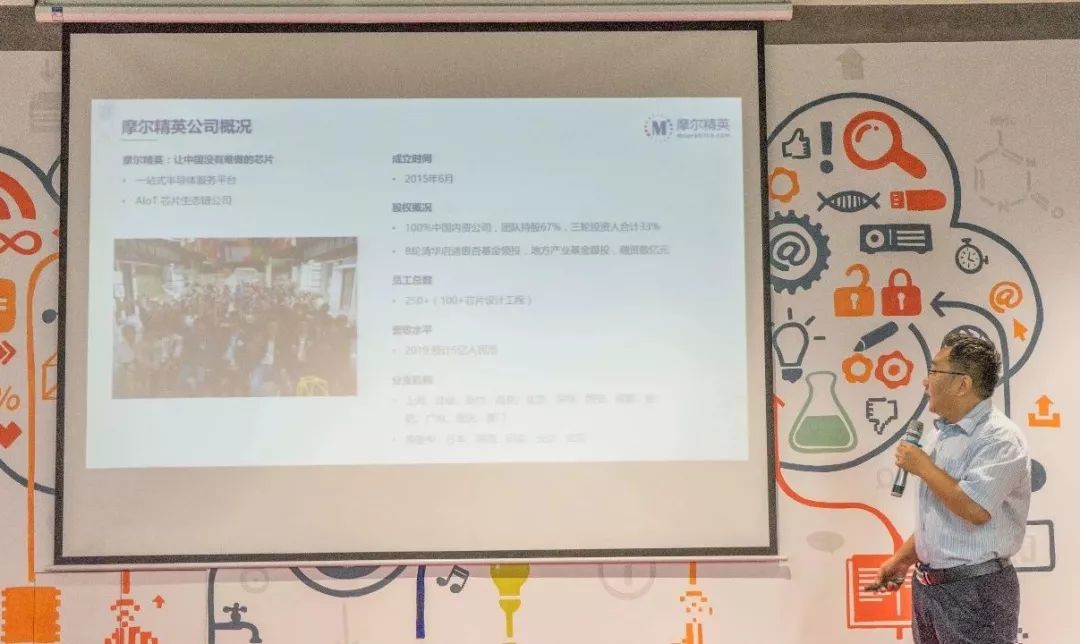

摩尔精英封装事业部负责人唐伟炜

摩尔精英封装事业部负责人唐伟炜

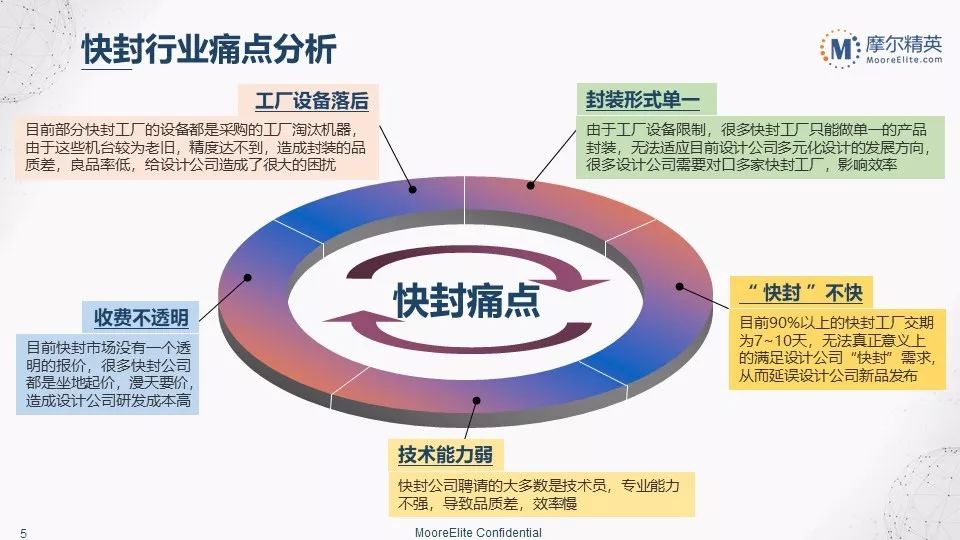

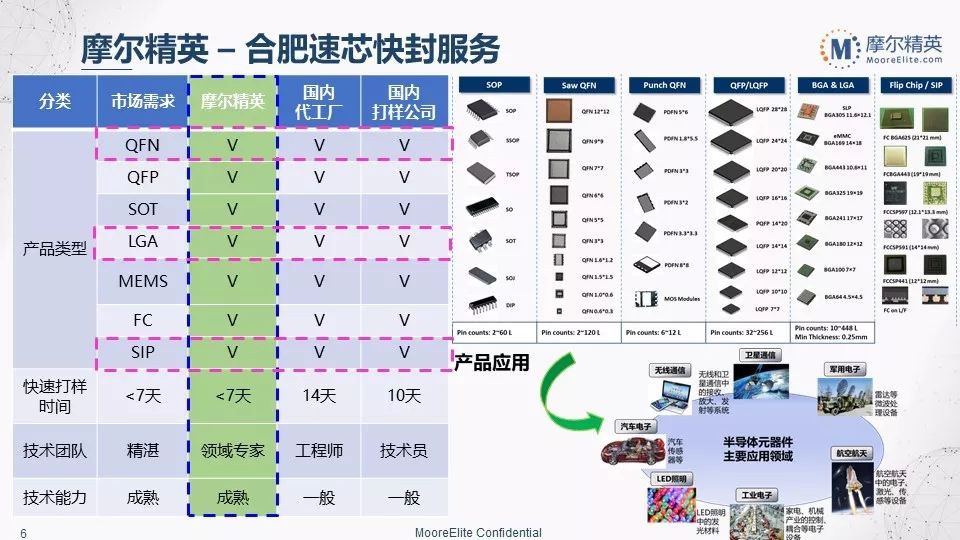

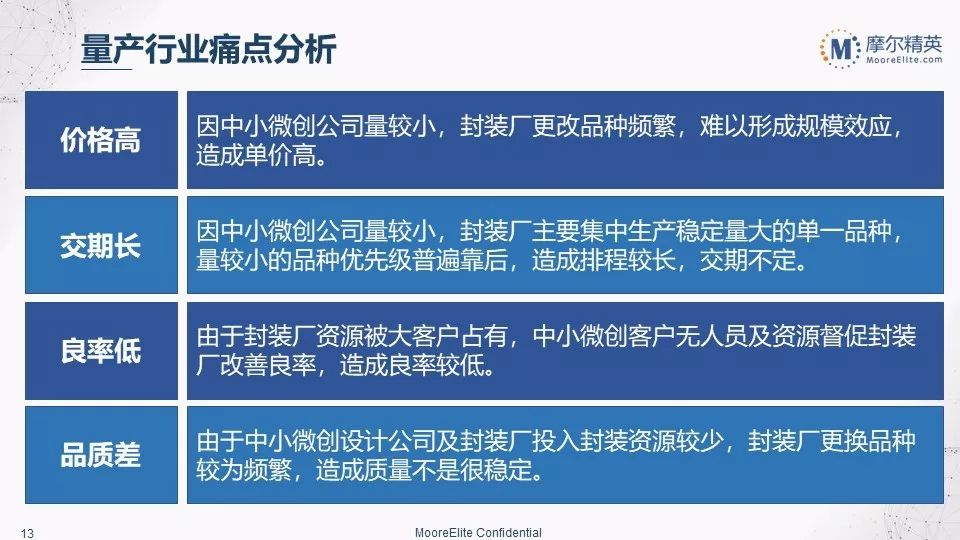

此次摩尔精英举办的“封装半日课”,正是从芯片封装的专业角度,针对中国大部分中小型芯片设计公司所共同面临的四个痛点,提出了相应的解决方案:

一是如何在芯片设计初期考虑后期封装可行性,实现成本收益最大化;

快封痛点与解决方案

突破SIP发展瓶颈

在封装课的互动交流环节,不少芯片设计公司的听众朋友谈到本企业面临的一些发展困惑, 中小型芯片设计企业的发展现状如何?在今年2月份芯片超人邀请摩尔精英创始人兼CEO张竞扬分享他对行业的观察以及对贸易商转型看法的文章里,我们或许可以找到部分参考的答案。(分销商,你也可以成为芯片公司)

“2018年,中国进口3120亿美金的芯片,而全球的市场总额也就是4700亿美金,中国进口了大概2/3。中国连续六年进口半导体超过2000亿美金,这是一个巨大的市场机会,这就是为什么各种投资都在往中国涌入的原因。中国芯片自主提供的比例非常低,但国内的芯片设计行业也在不断地追赶,从过去的二十年来看,成长的速度是非常快的,年复合增长速度超过40%。

目前中国有约2000家芯片设计公司,但从芯片企业的销售数据上看,中国超过1亿人民币销售额的芯片公司其实只有208家,也就是说90%公司的销售额其实连1亿人民币都不到。所以大部分国内芯片公司都处在成长初级阶段。”

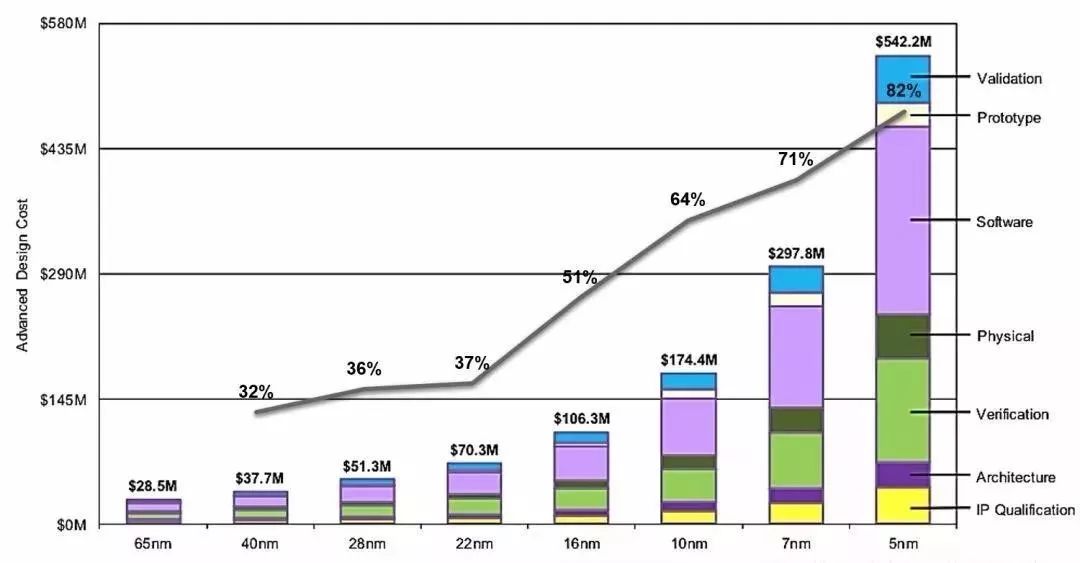

开发一颗芯片的难度很高。第一,需要一次性投入比较大;第二,从设计到投片成功需要等一年半时间,周期长。一般芯片公司设计会花费半年到一年,再加上投片花费半年到一年的时间,基本上整个周期需要18个月到24个月。IBS数据显示,22nm制程之后每代技术设计成本增加均超过50%。设计一颗28nm芯片成本约为5000万美金,而7nm芯片则需要3亿美金,3nm的设计成本可能达到15亿美金。

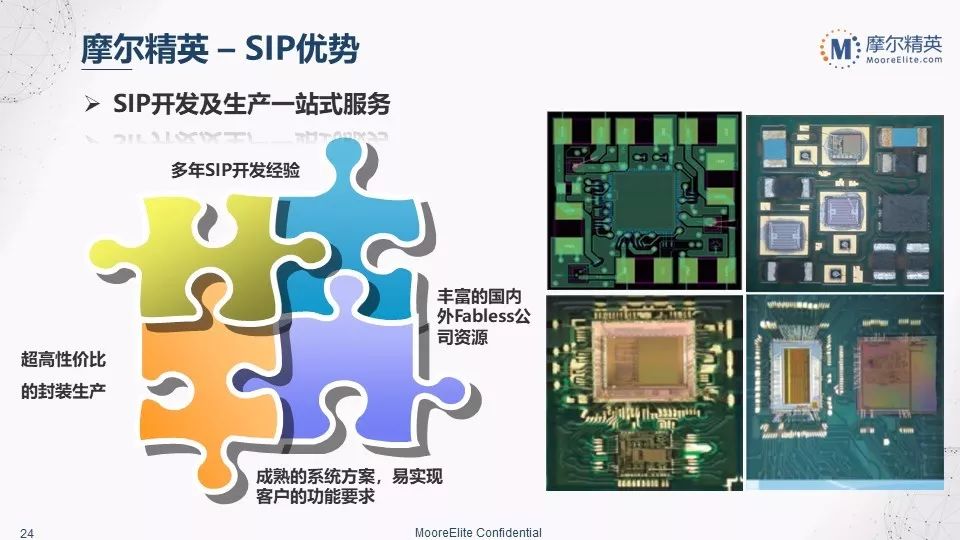

芯片行业在过去几年里出现了一些概念,有一个很重要的概念是SIP封装(System In a Package系统级封装),将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。

与传统制造流程不同的是,集成商不再是购买IP,而是采购满足整体芯片架构的、即插即用的die(裸片),这样的die在工艺上不受其他模块的约束,工艺选择灵活,可以是逻辑的芯片,也可以是模拟芯片。理论上讲,这种技术是一种短周期、低成本的集成第三方芯片(例如I/O、存储芯片、NPU等)的技术。摩尔精英封装事业部,致力于在SIP设计、SIP内部裸Die资源、SIP模块生产等多方面,为客户提供完整的SIP解决方案。

SIP封装基板/框架设计 芯片/封装/基板协同仿真 系統封裝SIP lSIP系统方案、原理图、布局、布线的设计及系统方案开发 WLP/Fan out设计、特种框架设计、陶瓷基板/模块设计 SIP封装内部芯片最优选择及内部芯片晶圆/裸片资源对接

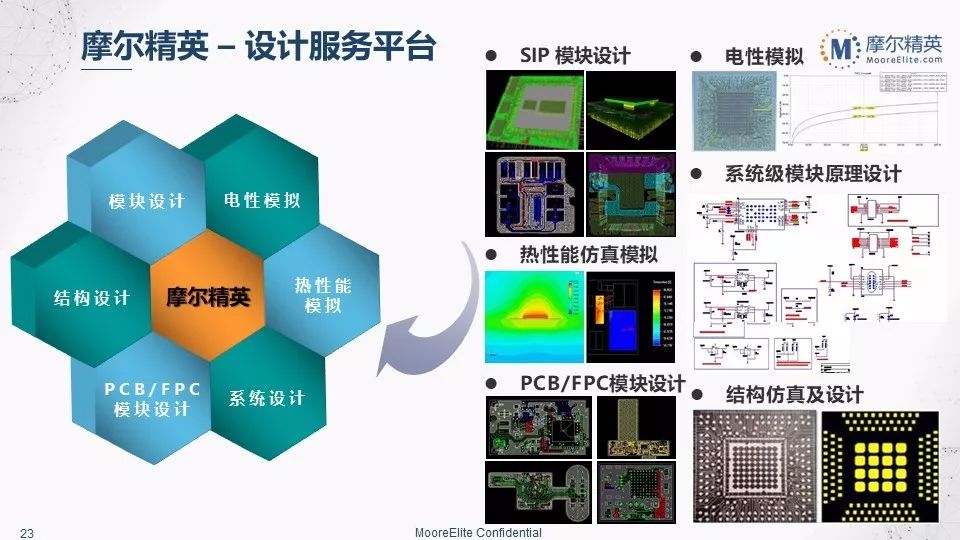

摩尔精英 – 设计服务平台:

SIP模块设计 电性模拟 热性能模拟 系统级模块原理设计 PCB/FPC模块设计 结构仿真及设计

多年SIP开发经验 丰富的国内外Fabless公司资源 超高性价比的封装生产 成熟的系统方案,易实现客户的功能要求

为量产痛点提供解决方案

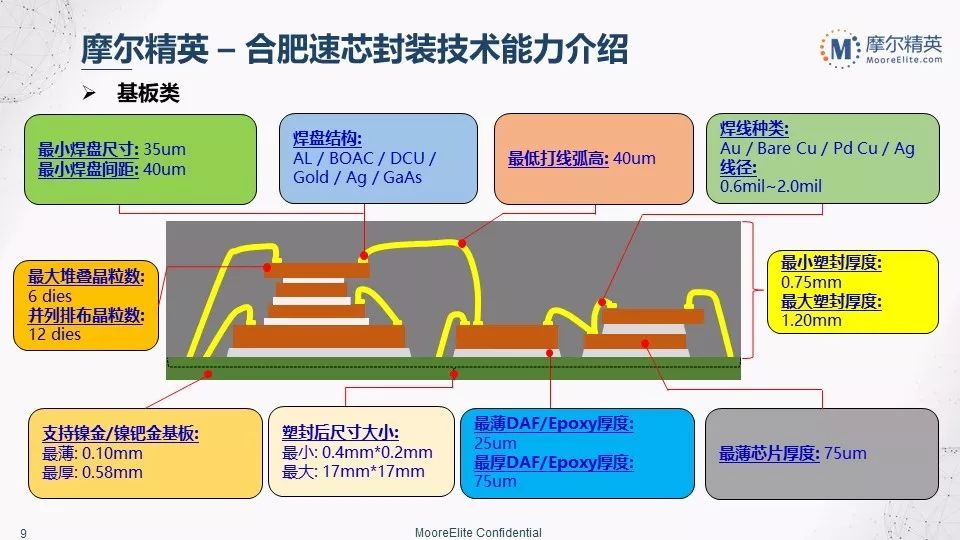

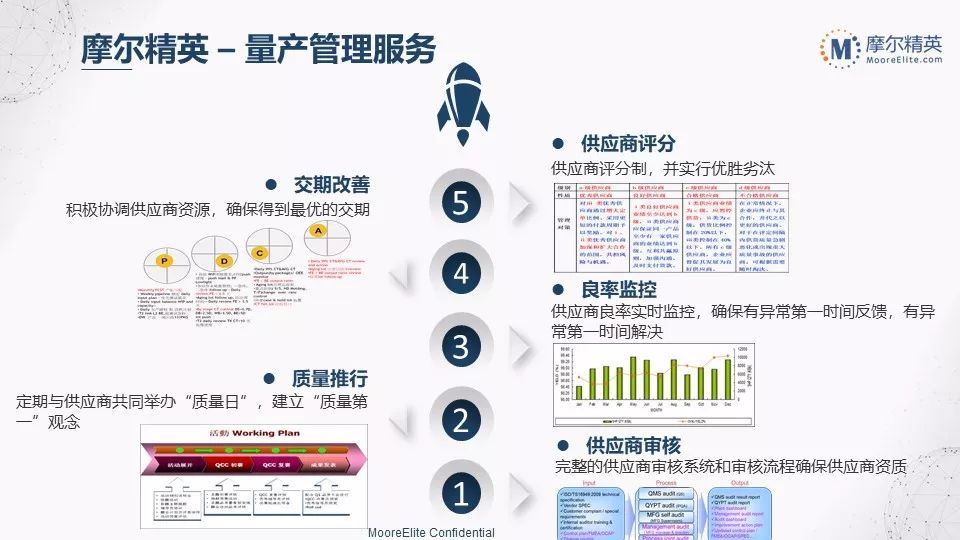

针对芯片量产的行业痛点,速芯微坚持与行业知名封装大厂合作,坚持为客户提供极具性价比的量产解决方案。

摩尔封装代工供应商资格审核

初期量产质量 & 良率监控

客户交期时时监控

良率监控及改善

“ 摩尔质量日 ”推进

季度可靠性监控

摩尔质量团队每月审核

年度供应商评分制

最优质量·最优交期·最优性价比

交期改善

质量推行

供应商评分

良率监控

供应商审核

封装设计规范专题讨论

封装课介绍了芯片封装的可靠性理论、分析和实践,有助于客户准确把握芯片可靠性的方法和时间。在“封装设计规范”的议题中,大家充分了解到如何在芯片设计前期考虑后期的封装可行性,为未来产品量产提高良率和质量稳定性,降低成本提供了有效保证。

现场客户中有一位来自芯片设计公司的高级工程师,对叠die 封装总会出现失效的问题提出了他的困惑 ,主讲师以他曾经历过的成功案例为客户提出了切实可行的参考解决方案。

封装技术与成本两全其美

如果您有封装业务的需求

请扫码留下您的需求信息

将会有专业顾问和您联系

封装半日课资料二维码

扫码立即获取本次封装半日课的视频及演讲资料~

福利

点击阅读原文,了解摩尔精英

扫一扫下载订阅号助手,用手机发文章

扫一扫下载订阅号助手,用手机发文章

朋友会在“发现-看一看”看到你“在看”的内容