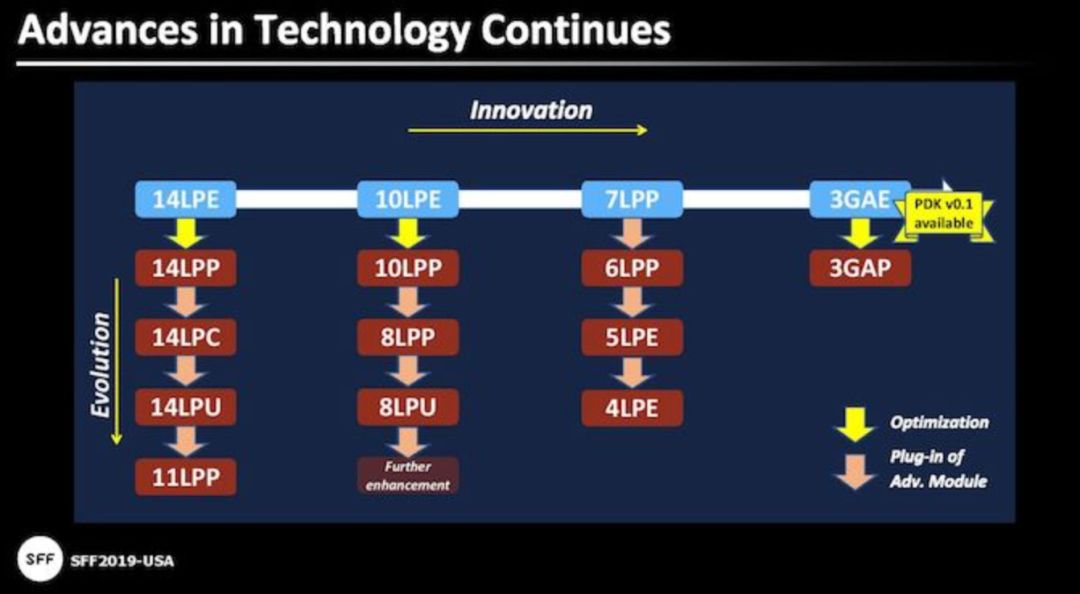

尽管日本严格管制半导体材料多少都会影响三星的芯片、面板研发、生产,但是上周三星依然在日本举行了“三星晶圆代工论坛”SFF会议,公布了旗下新一代工艺的进展,其中3nm工艺明年就完成开发了。

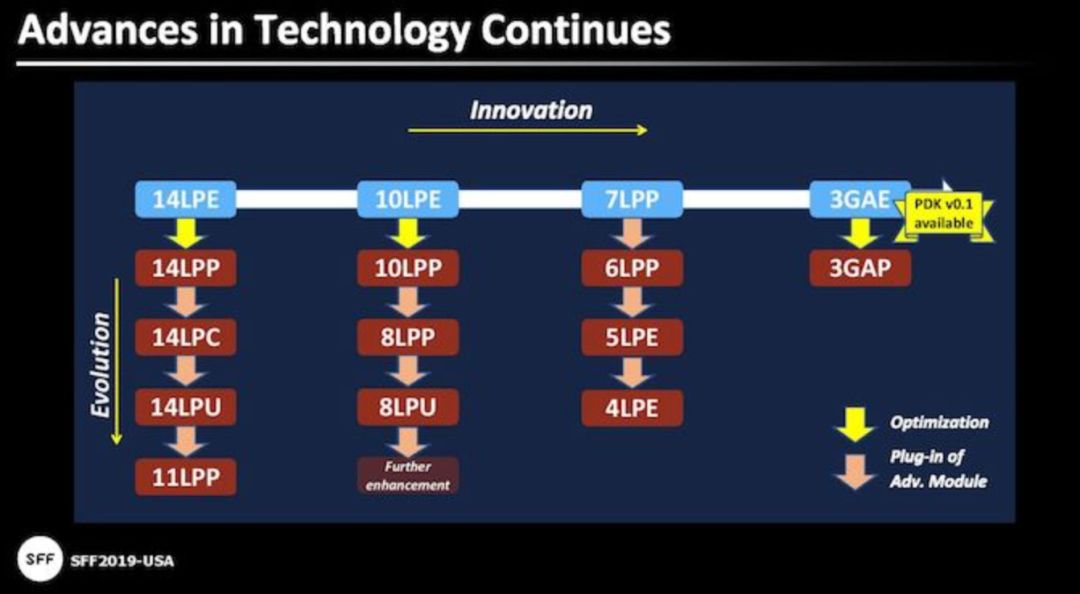

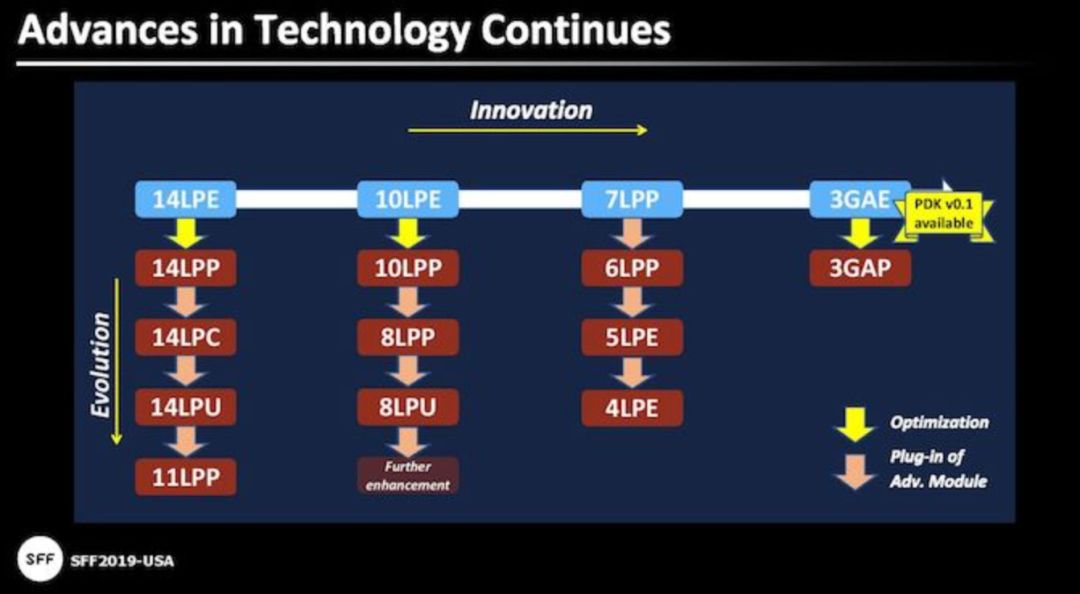

三星在10nm、7nm及5nm节点的进度都会比台积电要晚一些,导致台积电几乎包揽了目前的7nm芯片订单,三星只抢到IBM、NVIDIA及高通部分订单。不过三星已经把目标放在了未来的3nm工艺上,预计2021年量产。

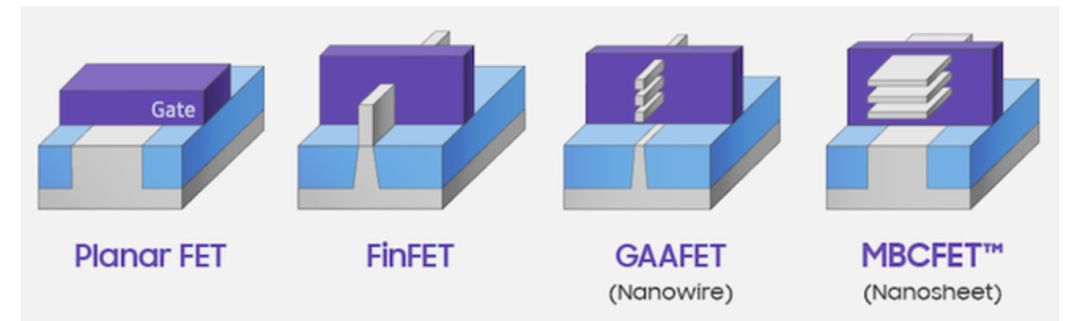

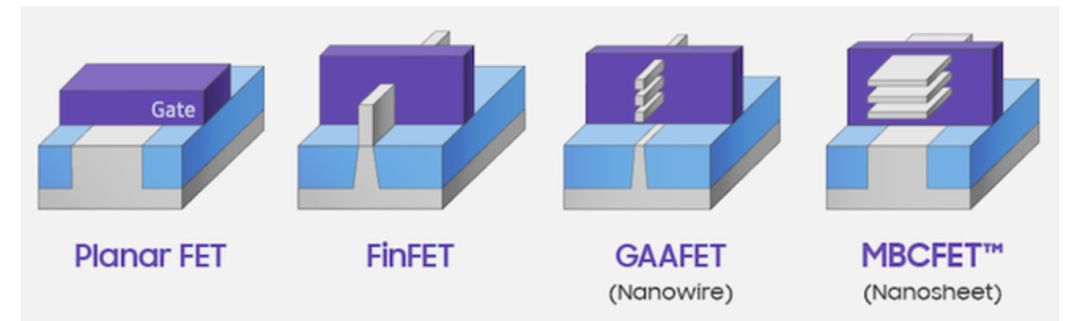

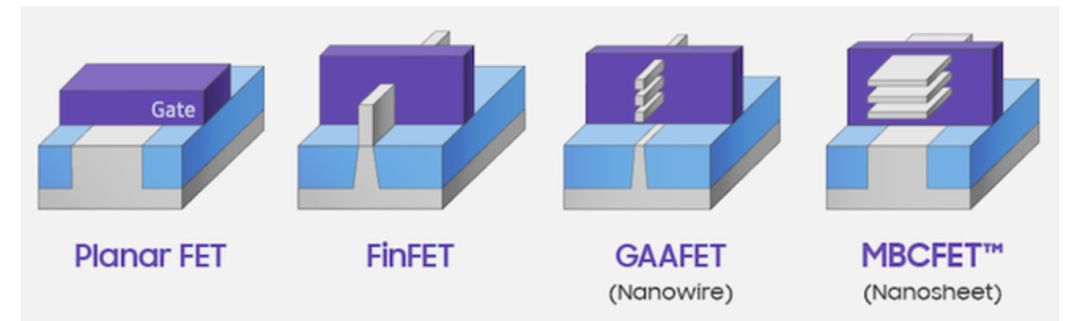

在3nm节点,三星将从FinFET晶体管转向GAA环绕栅极晶体管工艺,其中3nm工艺使用的是第一代GAA晶体管,官方称之为3GAE工艺。根据官方所说,基于全新的GAA晶体管结构,三星通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。此外,MBCFET技术还能兼容现有的FinFET制造工艺的技术及设备,从而加速工艺开发及生产。在这次的日本SFF会议上,三星还公布了3nm工艺的具体指标,与现在的7nm工艺相比,3nm工艺可将核心面积减少45%,功耗降低50%,性能提升35%。在工艺进度上,三星今年4月份已经在韩国华城的S3 Line工厂生产7nm芯片,今年内完成4nm工艺开发,2020年完成3nm工艺开发。Gate-All-Around ,也就是环绕式栅极技术,简称为 GAA 横向晶体管技术,也可以被称为 GAAFET。这项技术的特点是实现了栅极对沟道的四面包裹,源极和漏极不再和基底接触,而是利用线状(可以理解为棍状)或者平板状、片状等多个源极和漏极横向垂直于栅极分布后,实现 MOSFET 的基本结构和功能。这样设计在很大程度上解决了栅极间距尺寸减小后带来的各种问题,包括电容效应等,再加上沟道被栅极四面包裹,因此沟道电流也比 FinFET 的三面包裹更为顺畅。在应用了 GAA 技术后,业内估计基本上可以解决 3nm 乃至以下尺寸的半导体制造问题。

作为一款新技术,各家厂商都有自己的方案。目前已知的几种不同形态的 GAA 鳍片结构分别包括:● 比较常见的纳米线技术,也就是穿透栅极的鳍片采用圆柱或者方形截面;● 板片状结构多路桥接鳍片,穿透栅极的鳍片被设计成水平板状或者水平椭圆柱状(长轴和基地平行)截面;● 六角形截面纳米线技术,顾名思义,纳米线的截面是六边形;而三星对外宣称的 GAA 技术英文名为 Multi-Bridge ChannelFET,缩写为 MBCFET,实际上就是板片状结构多路桥接鳍片。三星对此作出的解释是,目前主流的纳米线 GAA 技术,沟道宽度较小,因此往往只能用于低功率设计,并且制造难度比较高,因此三星没有采用这种方案。并且三星认为 FinFET 在 5nm 和 4nm 工艺节点上都依旧有效,因此在 3nm 时代三星才开始使用新的 MBCFET 技术。根据外媒报导,三星今年年中于美国加州所举办的晶圆制造论坛(Samsung Foundry Forum)宣布,目前三星正在开发一项名为「环绕闸极」(gate all around,GAA)的技术,这个被称为当前FinFET 技术进化版的生产技术,能够对晶片核心的电晶体进行重新设计和改造,使其更小更快。三星指出,预计2021 年透过这项技术所推出的3 奈米制程技术,将能使得三星在先进制程方面与台积电及英特尔进行抗衡,甚至超越。而且,能够解决晶片制造缩小过程中所带来的工程难题,以延续摩尔定律的持续发展。

按照国际商业战略咨询公司(International Business Strategies)执行长Handel Jones 表示,目前三星正透过强大的材料研究让晶圆制造技术获得发展。而在GAA 的技术发展,三星大约领先台积电一年,英特尔封面则落后三星2~3 年。三星也强调,GAA 技术的发展能够期待未来有更好的图形技术,人工智慧及其他运算的进步,以确保未来包括智慧型手机、手表、汽车、以及智慧家庭产品都能够有更好的效能。而从三星的介绍来看,GAA 技术有可能根据鳍片尺寸和形态的不同,面向不同的客户。三星指出,垂直于栅极的纳米线或者纳米片的形态将是影响最终产品功率和性能特征的关键指标,纳米片和纳米线的宽度越宽,那么沟道尺寸和面积就越大,相应的性能越好,功率表现就越出色。三星在其 PDK 设计中提供了四种不同的方案,可以在一个芯片中不同地区使用,也可以直接使用于制造整个芯片。

看完有什么感想?

请留言参与讨论!

转自:快科技

如侵权请联系:litho_world@163.com

【欢迎留言,欢迎转发】

朋友会在“发现-看一看”看到你“在看”的内容