纽扣虽小,搭配却至关重要——Pin Assignment

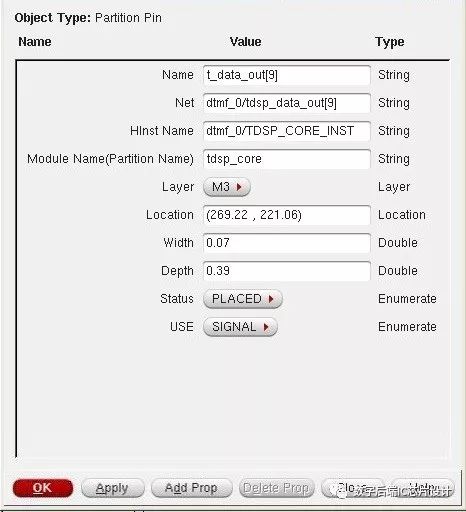

今天介绍一下Physical budget中Pin Assignment步骤。首先,关于pin的定义,器件的pin,一般指器件外部的引脚,与各种wire相连。而这里所讲的pin是指partition pin。一般来说,top层上的IO端口,我们称之为Port。而top下面,各个hierarchy module的端口,我们一般称之为Partition Pin。当这个partition被push down下去,成为block后,被单独load之后,这些pin又会变成IO pin。如下图所示:这些长条状的阴影小条就是pin了。从attribute editor中也可以看出他的type是partition pin.

别看这些pin小,但它在整个hierarchy flow中起着至关重要的作用。类似一件衣服上的纽扣一样,是各个block能顺利拼接合并的关键。那pin assignment的功能就是给纽扣排位置。位置排的不好,再好看的布料做出来的衣服都没人愿意穿。

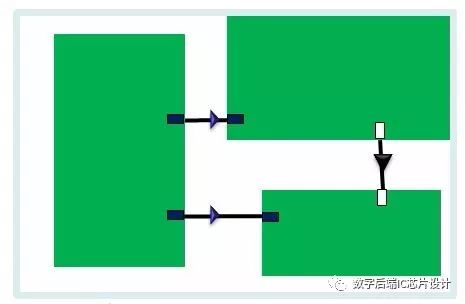

我们知道,在chip中,定义好每个partition,并切割下去,每个block分别各自完成布局布线的操作,然后再在顶层top level中实现合并。你可能会奇怪,在block level中,我们看不到外面的情况,那拼接时,其中的net是如何顺利找到对应的顶层中的net?其实靠得就是这些小小的partition pin。它是physical上,guide各个block连接的关键。看下面的简单的示意图:

上图中,绿色部分是各个partition。当做完pin assignment之后,在每个partition的各自边界上会长出不同layer的partition pin。有了这些pin,就定义好了每个block的input和output pin,图中蓝色部分。在block level中,我们不能改变pin的位置,否则就无法完成顶层收回的操作。

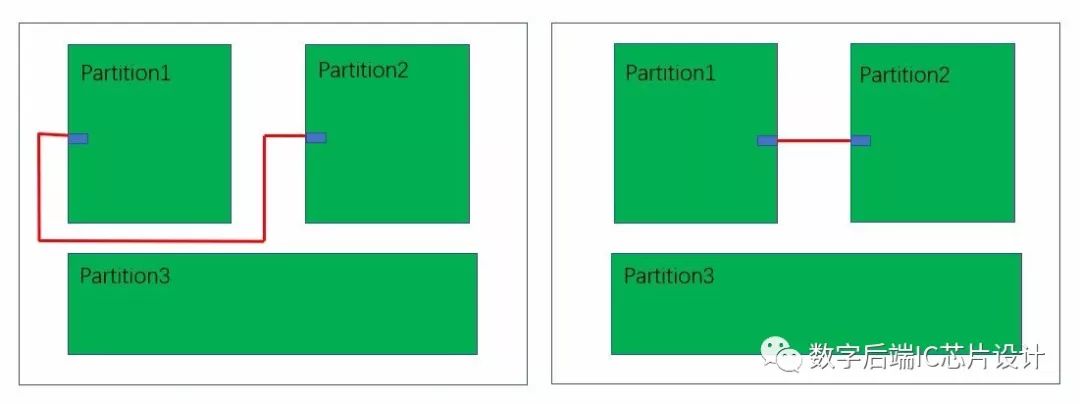

那pin的位置可以随便定义吗?答案显示然是不能的,合理的pin的位置,不仅能guide block的connection,而且会对时序的结果产生重要影响。看下面的对比示意图:

上左图的两个pin的位置assign的相距较远,这样会在顶层得到一条走线很长的timing path,造成严重的detour,给工具绕线带来严重的阻碍。如果我们能把partition 1的pin assign的更加合理些,如上右图所示,这样两个partition之间的path走向会得到明显的改善。所以chip level的pin assignment很重要。很多时候,你在top level费了半天劲,始终修不好的path,其实可能原因就是pin的位置不合理。

讲到这,那我们怎么去做pin assignment呢?在Innovus中,其实只需要通过一个assignPtnPin命令就可以。这个命令可以自动帮你摆放好各个partition的pin。当然,通常你必须要手动的设置一些摆放的规则,因为默认的摆放规则一般都比较差。我们来看一下正常的一个pin assign的flow:

第一步:在运行assignPtnPin之前,我们可以先设置一些pin constraint。主要包括Pin Group,Pin Guide,Pin Blockage,Spacing,Size,Layer等。下面我分别讲一下这一些constraint:

Pin Group:设置一个group,把需要的pin加在这个group中,assignPtnPin会尽量把这个group中的pin摆在一起。使用命令createPinGroup完成。

Pin Guide:通常和pin group一起使用,可以指定一个区域,guide这个pin group的放置位置。使用命令createPinGuide完成。图中白色部分就是pin guide

Pin Blockage:可以指定一个阻碍区域,assignPtnPin不会在这个区域摆放pin。使用命令createPinBlkg完成。图中红色部分就是pin blockage

Spacing,Size,Layer:可以指定pin之间的spacing,width,depth,Layer.采用命令setPinConstraint完成。

第二步:我们可以使用assignPtnPin去完成pin assignment了。可以看以下log:

第三步:摆放好pin以后,我们需要去检查下摆放的结果是否正确:

一般我们会通过以下两种方式检查pin assignment的结果。首先,我们可以使用checkPinAssignment检查pin assign的结果是否符合规则。它可以检查以下内容:

1. pin有没有遵循设置的pin constraint

2. pin有没有assign到route track上

3. master和clone partition的design上, pin的位置有没有一致。

我们可以看一下一个design的pin assign结果:

对于pin assign的结果,我们当然希望越多的net能做到相互align。因为这样可以得到更好的route 结果。我们可以使用reportUnalignedNets来检查pin的align情况。这个会检测ptnToPtn,topToPtn,2-pin net的align情况。我们可以看以下log:

第四步,Pin assign以后,我们可以先让工具快速地做一把trialRoute,记住是要在-honorPin的模式下,用trialRoute的结果可以检查实际full chip的congestion情况。

好啦,pin assign的介绍就这么多啦,还有具体一些命令的用法,大家可以去查阅doc.

简历请戳邮箱:taozhang3260@163.com

觉得有用的话,给我点个好看吧

朋友会在“发现-看一看”看到你“在看”的内容