如何使用FPGA来设计智能网卡(SmartNIC)以提高服务器的计算能力(第二章下)

在本文的上一篇中,我们介绍了如何用FPGA来一步一步地构建智能网卡,并介绍了八种设计示例;今天我们将继续介绍剩下的五种设计示例,以帮助读者根据自己的实际需求快速地开发所需的智能网卡。

示例9添加一个TCP卸载引擎来处理TCP堆栈的全部/部分工作,这样可以在不消耗更多CPU周期的情况下提高智能网卡性能。

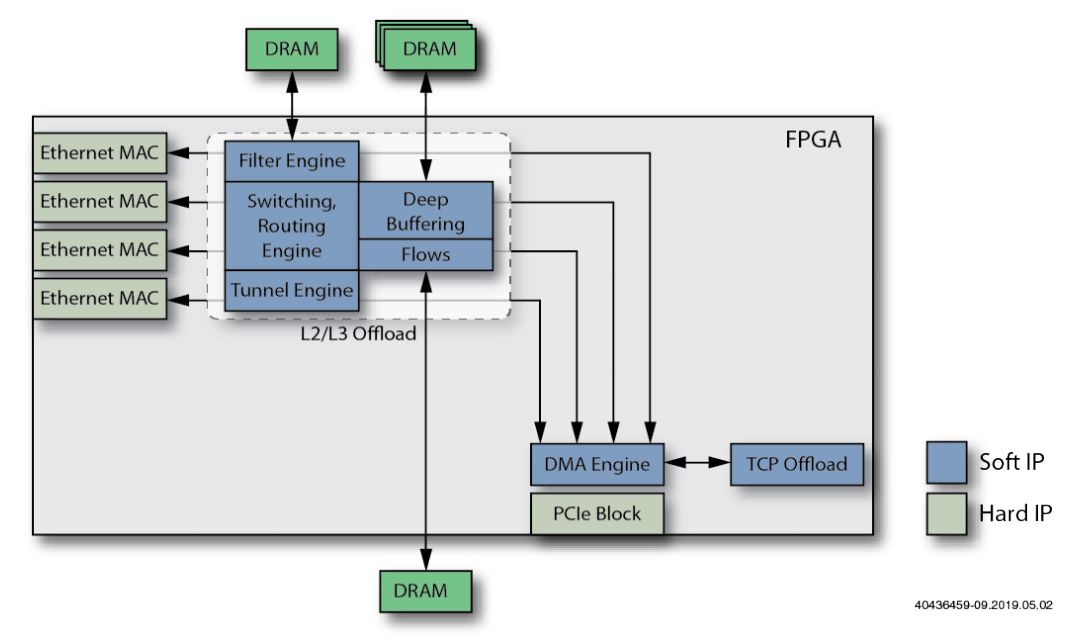

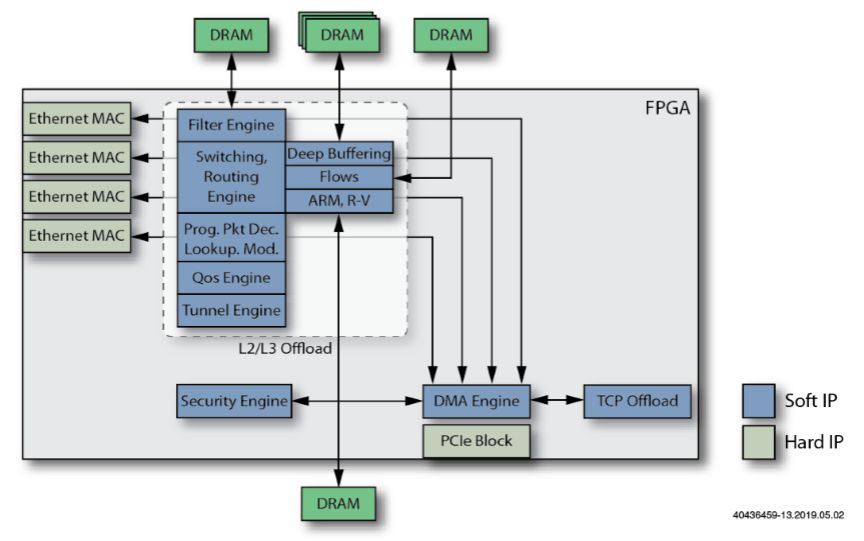

图10:示例9 – TCP卸载引擎

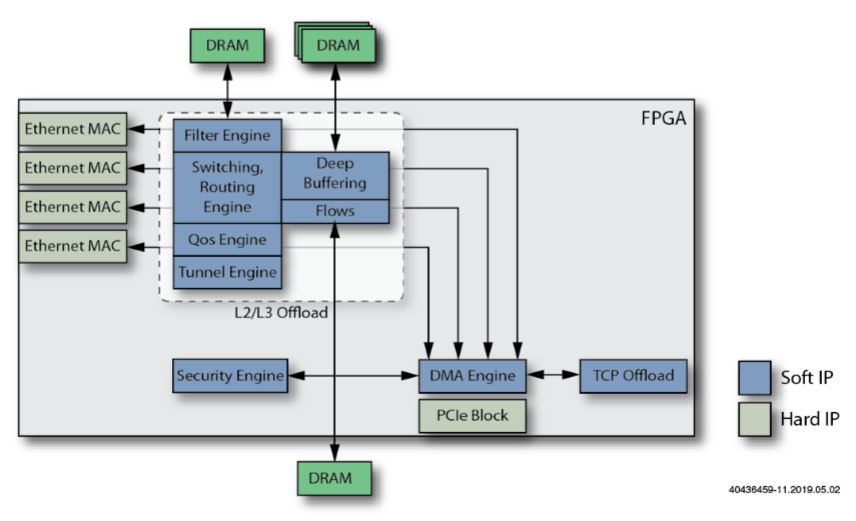

示例11添加了一个单独的QoS引擎,以允许智能网卡管理服务等级协议(SLA),而无需服务器CPU的干预。

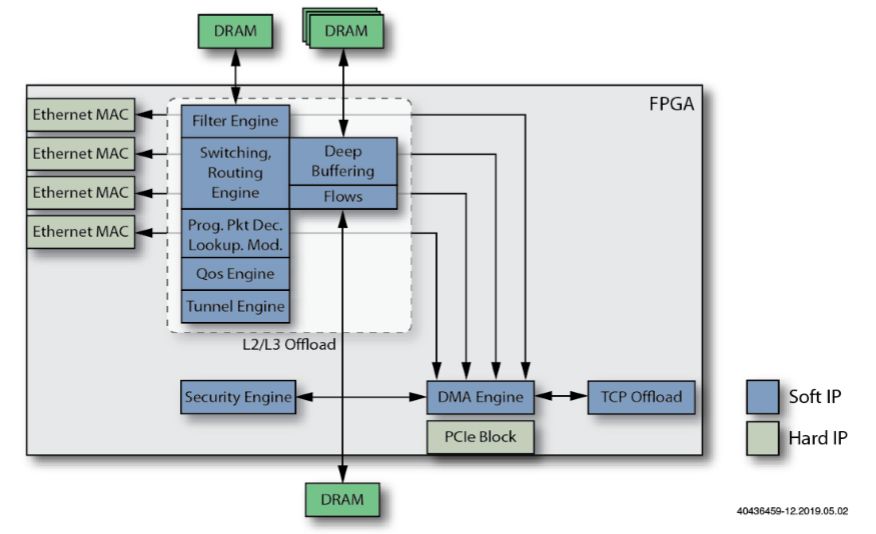

示例12添加一个可编程的数据包解码器,该解码器将类似P4的可编程性集成到智能网卡中。P4是一种标准的网络编程语言,专门用于描述和编程分组数据包转发面的操作。

示例13添加一个或多个板载处理器,它们为智能网卡提供了完整的软件可编程性(用于诸如OAM等任务),进一步实现服务器处理器的任务卸载。

在数据中心引入带有FPGA的智能网卡设计的最大障碍之一是基于软件的多核智能网卡在10G时代获得的巨大成功所带来的工程惯性。网络卸载和加速技术已经在API和接口协议采用并标准化,这些API和接口协议允许服务器任务与某些多核智能网卡交互。每个服务器软件栈都以几个特定的网卡和智能网卡为目标。为现有网卡和智能网卡开发的API和驱动程序被硬编码到在服务器CPU上运行的软件栈中。除非使用FPGA设计的智能网卡可以支持这些现有API并模拟现有接口协议,否则将这些智能网卡在投入使用时需要修改软件栈。

点击“阅读原文”,以了解前面已经介绍的八种智能网卡设计示例。

长按识别二维码,欢迎您关注“Achronix”微信公众号:

扫一扫下载订阅号助手,用手机发文章

扫一扫下载订阅号助手,用手机发文章

朋友会在“发现-看一看”看到你“在看”的内容