设计 MCM/SIP 封装并集成到系统 PCB 中

系统级封装的异构集成

传统上,MCM(多芯片模块)是一种将多个 ASIC(或 ASIC 和存储器)集成到一个成本更低、外形更小且更强大的模块的方式,这种模块可以替代单个大型 SoC。您可以设计并制造体积更小的高良率 ASIC(图 1), 使其表现出与单个大型 SOC 相似的行为,而不是将所有或大部分系统需求集成到一个庞大而复杂的 SOC 上。这在国防和航空航天市场被证明极具吸引力,因为这些市场的容量小于消费者商业市场,尝试创建混合技术 SoC 既不现实,成本也过高。

图 1:约 2009 年的 Intel® Clarkdale 模块

随着移动无线产品市场的爆炸式增长,在可装入比人手更小的产品 且具有高成本效益的系统中,对于信号处理、闪存存储器和无线通信的新需求也接踵而至。这一挑战推动了一种不同的封装方法,并引领行业向针对裸片的 3D 芯片堆叠方向发展。

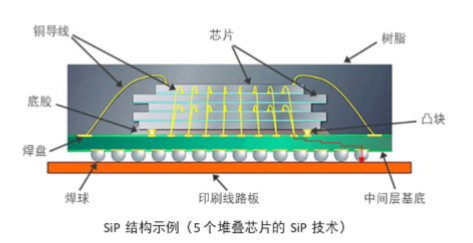

这种方法被称为系统级封装 (SiP),它需要芯片到芯片互连,从而使封装成为一项关键的技术元素。一些人认为,与高性能计算应用中广泛使用的水平 MCM 相比,SiP 是一种垂直 MCM (图 2)。SiP 的优势包括用户 IP 集成、IP 复用、混合模拟/数 字设计、设计风险低、集成大型存储器、降低工艺复杂性、 降低开发成本和缩短上市时间。

图 2:SiP 结构示例(五个堆叠芯片的 SiP 技术)

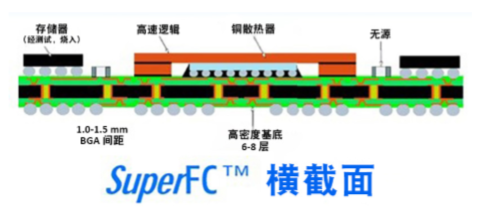

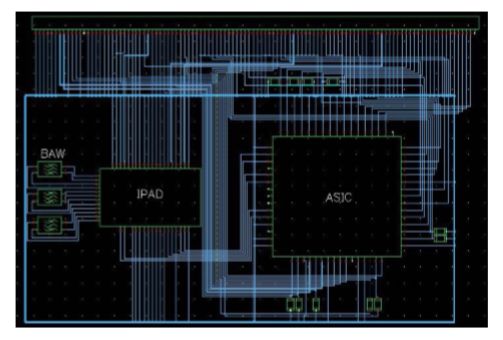

这种构造块方法非常适合异构应用,对于那些希望将 ASIC 集成到高性能子系统中的人来说极具吸引力,其性能与定制 SoC 的性能接近,而成本和上市时间仅为定制 SoC 的一小部分。简而 言之,SiP 采用横向或纵向集成技术将包括 SoC 和分立元器件在内的 IC 结合到一起(图 3)。在本文中,我们将重点介绍一个 已知 PCB 系统中包含的 SiP 的设计,这在系统公司中很常见。这类情况下,SiP 不仅需要作为一组集成的异构 IC 满足集成和性能目标,还必须针对其目标系统的 PCB 甚至多个 PCB 进行优化。

图 3:典型的异构 SiP 封装示例

了解系统全景

1

在牢记基本和关键设计要求的同时,还要直观显示和理解整个多基底设计(多芯片 SiP 和系统 PCB),这很容易让设计人员和设计团队感到不堪重负。创建新的多芯片异构 SiP 及其相应系统板的任务往往涉及两到三个具有不同视角的不同工程团队。虽然可以在协调会议中将不同设计学科聚集到一起,但成功的联合计划确实需要方法、流程,而且通常还需要一些技术和自动化来将这些学科整合到一起。

SiP 设计人员通常是一个多学科团队,必须合作解决几个优化问题,包括系统的 I/O 要求、散热和信号完整性约束、芯片布局和方向、堆叠配置、封装基底和中介层设计、IC 和封装级别的互连设计,同时还要考虑有关系统 PCB 的约束。

要获得最佳结果,第一个要求是 SiP 连接环境的可用性。它必须能够读取和写入所有异构组件(数字和模拟 IC、封装、电路板)的顶层层次化网表,并将它们全部合并,即使它们来自不 同的设计环境。

它还必须能够构成原理图并生成完整的模型(图 4)。

图 4.简单的异构 SiP 设计的原理图视图

然后,必须实现所有异构 SiP 元素的完整叠层规划。

必须提供一类能够在 3D 空间工作的新算法,以便正确地堆叠所需的元器件,将它们与其余的 SiP 元器件布置在一起,并正确地规划所有元素(包括封装焊盘)之间的接口。

必须对涉及的所有 ASIC 应用智能 I/O 规划策略,以便并行验证和/或优化初始 I/O 外围配置,遵守不同的规则集,从而满足硅片工艺以及电气和装配规则。

后续内容关于如何设计针对目标 PCB 优化过的 SiP,

可点击“阅读原文”下载全文。

END

扫一扫下载订阅号助手,用手机发文章

扫一扫下载订阅号助手,用手机发文章