【技术】IMEC:迈向1nm技术节点

以下文章来源于半导体百科 ,作者服部毅

半导体集成电路视频与博文分享,共同学习,共同成长。

作者:服部毅

转载自半导体百科

IMEC于10月11日在东京举办了年度研究结果介绍会“ IMEC Technology ForumJapan 2019(ITF Japan 2019)”。

原先负责并领导IMEC的半导体微缩化工艺/器件部门的安·斯蒂根(An Steegen)于2018年秋季突然退休,留下重要职位空缺。会议当天,新到任的Myung-Hee Na博士作了题为“通往CMOS微型化极限的道路”的演讲,并介绍了更新至1nm节点的IMEC半导体技术路线图。在2001年加入IBM之后,她从事尖端半导体工艺和器件的研发工作已有18年,并于2019年加入IMEC。前任Steegen也来自IBM,因此Myung-Hee算是其后辈。

改进晶体管的结构和材料以延续摩尔定律

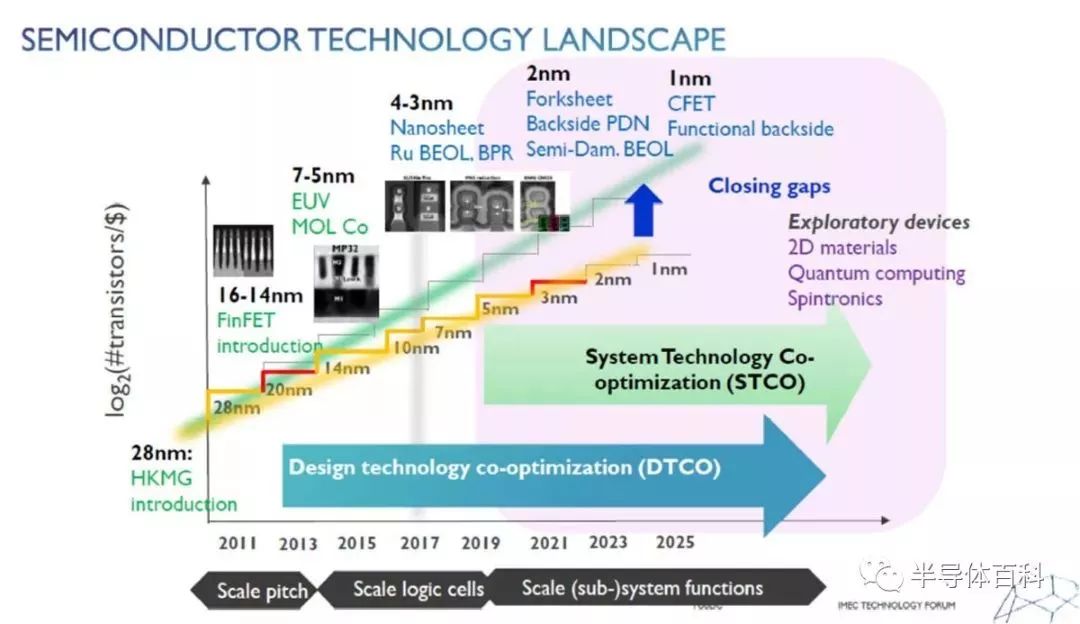

让我们看一下IMEC发布的半导体技术路线图。横轴表示时间,纵轴表示每单价的晶体管数(晶体管数/美元)。随着微型化和集成化的发展,由于工艺复杂性,制造成本正在迅速上升,因此,无法按摩尔定律降低单位晶体管的制造成本。

迈向1nm节点的技术路线图(来源:IMEC)

长期以来,摩尔定律已经失效,但IMEC并没有放弃,持续改进晶体管结构和材料,并且对工艺进行优化以呈现1nm节点的技术路线图。

从28nm技术节点采用HKMG(High-K/ Metal Gate),并在16 / 14nm之后从传统的平面结构转向FinFET结构。从7 /5nm开始,开始采用Co作为MOL布线材料以及EUV光刻,以进一步改进FinFET结构。

从4 / 3nm节点开始,FinFET将被GAA结构取代,第一代GAA将采用硅纳米片。独创的埋入式电源线(将Vcc和地线埋入前层以压缩标准单元面积)将采用Ru作为布线材料。

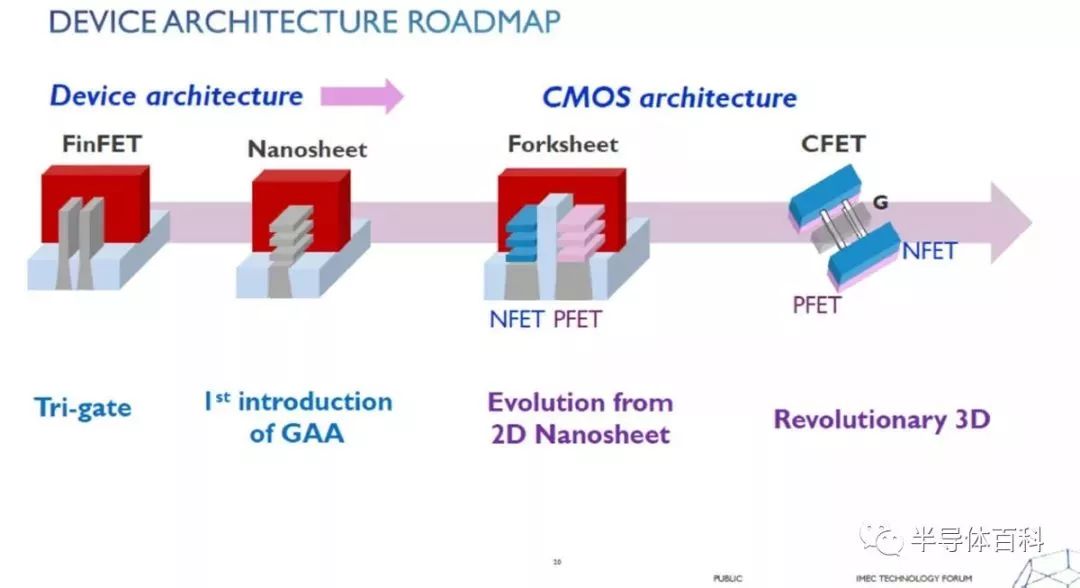

半导体器件结构路线图(来源:IMEC)

2nm 采用 Forksheet,1nm 采用 CFET

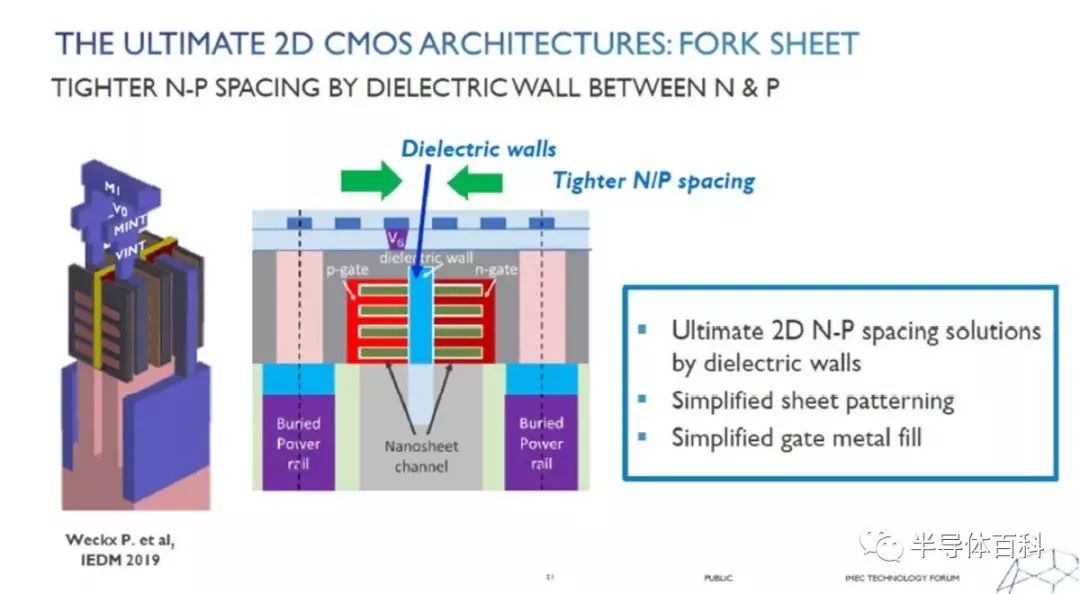

对于高性能和低功耗应用,IMEC计划采用FinFET的改进版本。换句话说,2nm技术节点将采用Forksheet结构,其中n型和p型纳米片紧密地靠在一起,并且其间有一层“绝缘墙”。之所以命名为forksheet,是因为其截面类似于餐叉。与此同时,在芯片背面提供配电网络(PDN)从而向BPR提供有效的电能供应。

当达到1nm节点时,IMEC会采用CMOS结构的Complementary FET(CFET)。在此,通过在p型FET上堆叠n型FET,即通过三维堆叠具有不同导电类型的晶体管,从而标准单元面积被大大减小。据说芯片的背面可以提供更多功能,但未公开细节。从这里开始,将采用high-NA EUV光刻以进一步微缩晶体管结构。

IMEC还希望采用二维材料,自旋电子学和量子计算。为了将来进一步微缩,除了设计和工艺协同优化(DTCO)之外,系统和工艺协同优化(STCO)也很重要。

最终的二维CMOS结构“Forksheet FET”(来源:IMEC)

到目前为止,SRAM必须在每个存储单元的平面上构建6个晶体管。IMEC表示,通过改进晶体管结构和电源线,即通过采用GAA和BPR,顶视图中SRAM晶体管的等效数量可以减少到每个存储单元4.4个晶体管,即SRAM单元面积大约减小到原来的2/3。

延续摩尔定律的另一种技术是3D封装。在2019年5月于比利时举行的IMEC技术论坛2019上对此进行了详细介绍。从芯片堆叠开始的3D封装最终将出现在晶体管本身的3D堆叠中。IMEC正在同时研究垂直堆叠以及横向微缩,并正在尝试提高系统集成度。为此,IMEC同时专注于优化工艺技术,设计技术和系统技术。

本文由Jason Jin翻译自マイナビニュース,阅读原文请点左下角。

免责声明:本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将立即删除内容!本文内容为原作者观点,并不代表本公众号赞同其观点和对其真实性负责。

END