【技术】一篇牛叉硕士论文——《继电器与开关电路的符号分析》

以下文章来源于中科院半导体所 ,作者娇娇的越王楼

半导体领域的行业动态、科技突破、权威发布、学术会议,同时也包括行业权威部门的招生、招聘信息等。

作者:娇娇的越王楼

转载自中科院半导体所

你很好引

我一引就能把你引进去

1938年香农在MIT获得电气工程硕士学位,硕士论文题目是《A Symbolic Analysis of Relay and Switching Circuits》(继电器与开关电路的符号分析)。当时他已经注意到电话交换电路与布尔代数之间的类似性,即把布尔代数的“真”与“假”和电路系统的“开”与“关”对应起来,并用1和0表示。于是他用布尔代数分析并优化开关电路,这就奠定了数字电路的理论基础。哈佛大学的Howard Gardner教授说,“这可能是本世纪最重要、最著名的一篇硕士论文。”

之前我们用继电器讲过逻辑电路:

继电器工作原理的动画

card from wiki

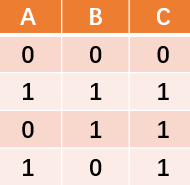

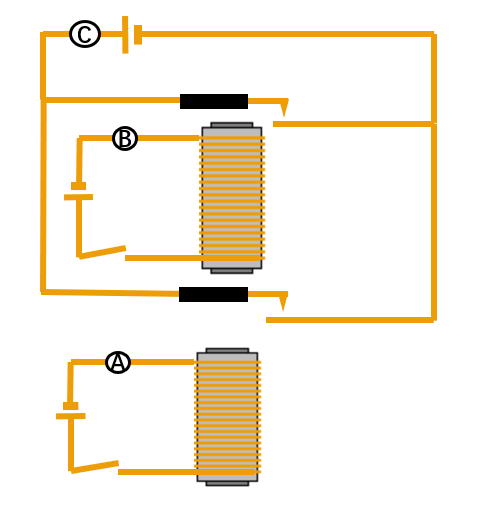

如把两个继电器并联或串联起来,可以实现更复杂的逻辑关系,下图是两支并联的常开继电器,只要A或B回路之一接通,C回路就导通。写成真值表是:

两支常开继电器并联组成“或”门

逻辑代数与逻辑门

在数学和数理逻辑中,逻辑代数(有时也称开关代数、布尔代数)是变量的值仅为真和假两种真值(通常记作1和0)的代数的子领域。初等代数中变量的值是数字,而且主要的运算是加法、乘法和乘方(以及它们的逆运算),而逻辑代数的主要运算有合取与,记为∧;析取或 ,记为∨;否定非 ,记为¬ 。

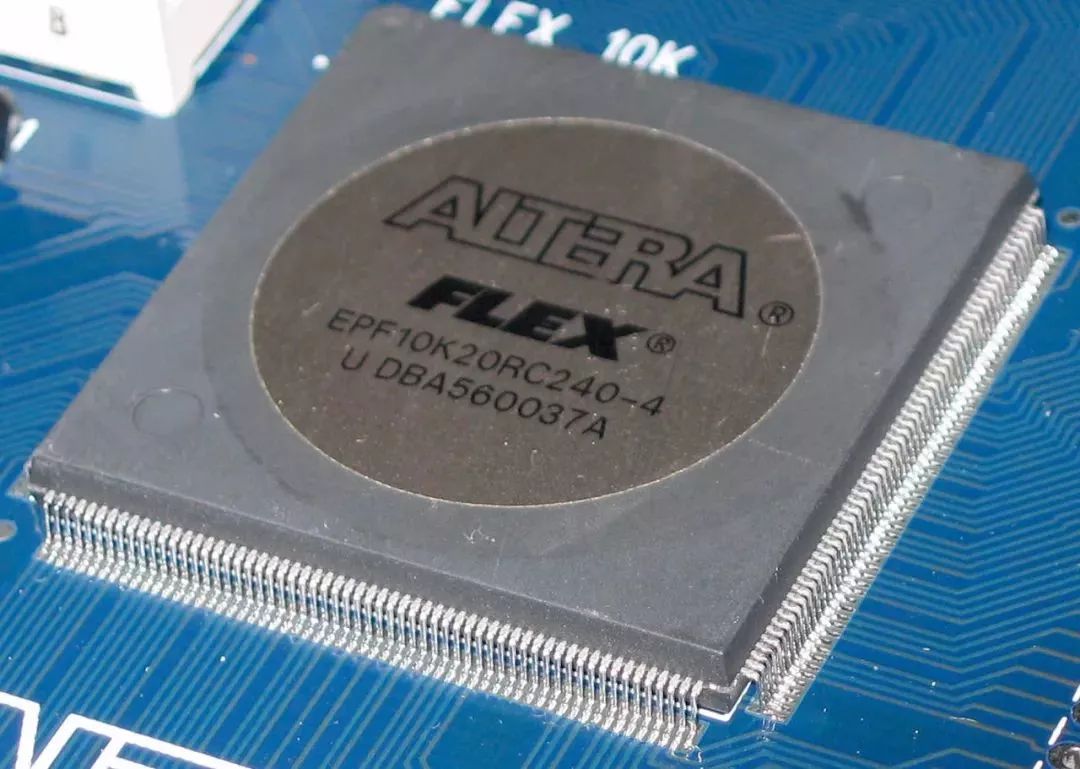

逻辑门是在集成电路上的基本组件。简单的逻辑门可由晶体管组成。这些晶体管的组合可以使代表两种信号的高低电平在通过它们之后产生高电平或者低电平的信号。高、低电平可以分别代表逻辑上的“真”与“假”或二进制当中的1和0,从而实现逻辑运算。通常组合使用实现更为复杂的逻辑运算。一些厂商通过逻辑门的组合生产一些实用、小型、集成的产品,例如可编程逻辑器件FPGA等。

Altera公司的Flex系列FPGA:EF10K20RC240-4,

该芯片内有20,000个Cell(逻辑晶格)可供配置配置。

20世纪以来,逻辑代数一直是数字电路设计的基础,并且所有现代编程语言提供支持。几乎所有现代通用计算机都用二值布尔逻辑做运算;也就是说它们的电路是二值布尔逻辑的物理表示。几种表示方式:导线上电压的高低,磁性存储设备中磁畴的方向,打孔卡或纸带上的洞,等等。

应召唤而生的MOS与CMOS逻辑电路

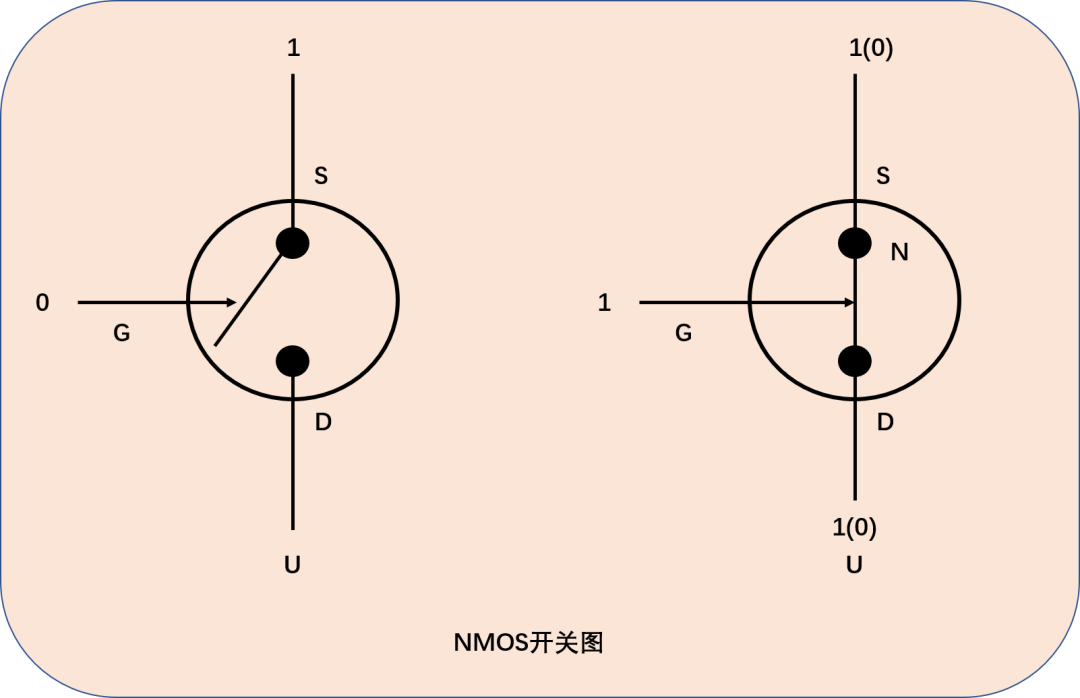

其实几乎同继电器逻辑一样,如果我们把NMOS画成继电器那就是这样的:

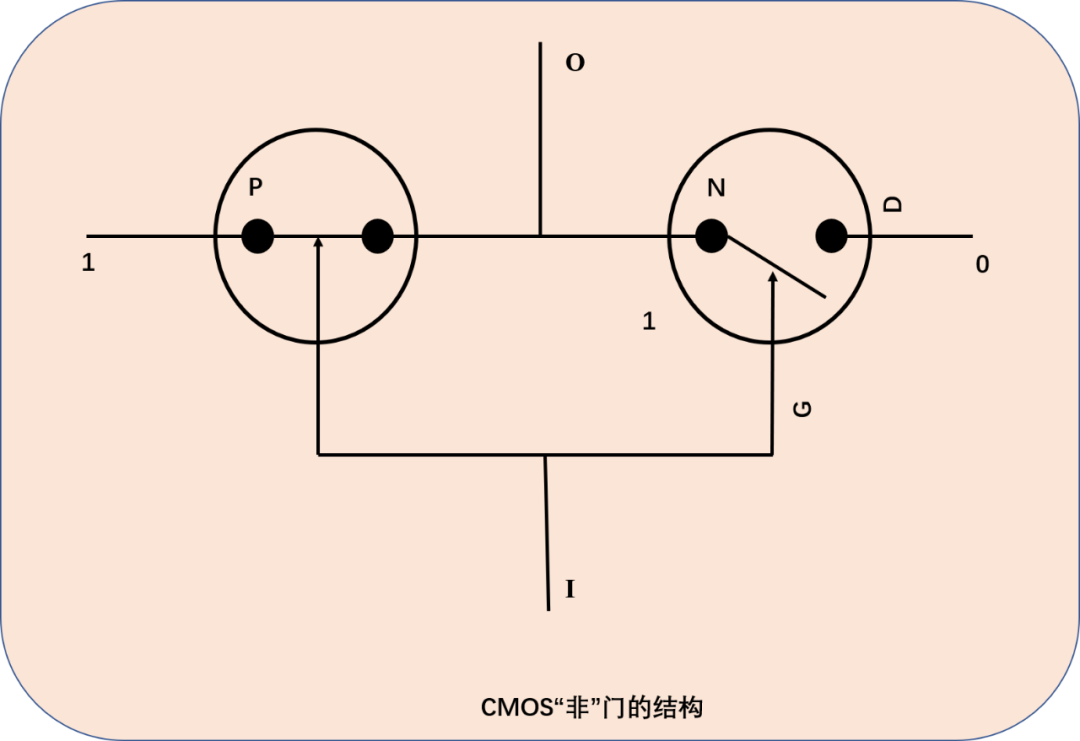

圆圈中的N表明源极S和漏极D都参杂成n型区。栅极处于正电位对应逻辑1(实际电路中使用的电压已经从5伏降到3.3伏或2.7伏或更低)。这时S和D之间靠n型沟道导通,它们同时处于逻辑1或0。当G处于0电位(逻辑0)时,S和D断开,它们的逻辑关系不确定。

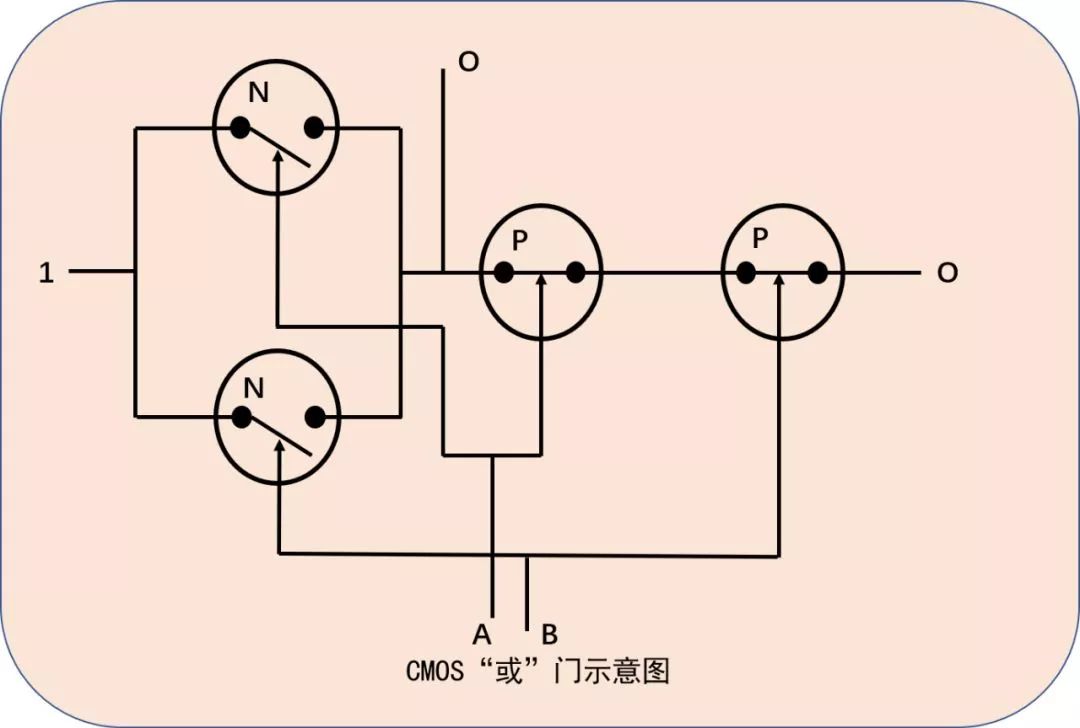

对于PMOS就只要把上面的n和p以及高低电位互换,它就成为栅极处于0电位时导通的开关。把互补的NMOS和PMOS管结合使用,就成为CMOS逻辑电路。

如图,我们令PMOS管的S极总是处于高电位,而NMOS管的漏极处于低电位。当输入I为逻辑0时,PMOS导通,输出O与PMOS的S极处于相同的高电位,即逻辑1。当输入I为逻辑1时,NMOS导通,输出O与NMOS的D极处于相同的低电位,即逻辑0。把两种逻辑关系合并起来,正是逻辑“非”。

比起MOS器件,CMOS耗能甚小。因为CMOS的静态电流约等于0,除非负载不是MOS而是阻性负载,而PMOS在低电平输入、NMOS在高电平输入时有静态电流,功耗会比CMOS大得多。而且在同等工艺、同等器件尺寸下,PMOS比NMOS延时长(简单的说就是空穴导电不如电子导电有效率),而且CMOS可以在1.2V(甚至更低些)到15V电压下工作,集成度也可以做得比其他类型的器件高。

今天,CMOS不仅仅是微处理器和存储器芯片的主导技术,而且已经发展到其他专用集成电路,如,CMOS图像传感器等。

目前集成电路存在的一些限制问题

首先是开关速度和电信号经过每个“门”的时间。这当然是决定整个计算速度的最基本的参数。人们觉得10mg的继电器接触点太大了也太重了,不可能在短时间内达到很高的速度,而采用了质量为9.10956×10^-31kg的电子来代替金属触点。这有点像绿巨人和闪电侠赛跑。

其次是电路的功率消耗,它引起散热问题,限制了元件的密集程度。各种原件的密度化和散热问题也是一直以来大家的一个研究方向。这个问题有点类似于北京地铁的早高峰,空间真不是挤挤就能有的,总是有几个上不去的。

再有就是维持电路工作的电源电压,是3伏还是15伏,需要一种还是两种。表示逻辑1的高电平,和代表逻辑0的低电平相差多少?这个差别如果太小,就容易因为偶然的噪声干扰导致逻辑错误;而相差较大就必然要求较高的电源供应。

做作业的时候,我们画的逻辑原理图,可以任意地把100个条件“或”或者“与”起来,把一个逻辑变量同时送到80个“门”的入口去起控制作用。但是实际做起来,就不这样简单了。一个门电路最多能有几个入口,它的输出信号最多能驱动几个别的电路,都有限制。

各种电路的成本差别,当然也不能忽略。选用逻辑电路时,必须综合多种因素,权衡利弊。

参考资料:

免责声明:本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将立即删除内容!本文内容为原作者观点,并不代表本公众号赞同其观点和对其真实性负责。

END