英特尔未来10年工艺路线图曝光:2029年推出1.4nm工艺!如何实现?

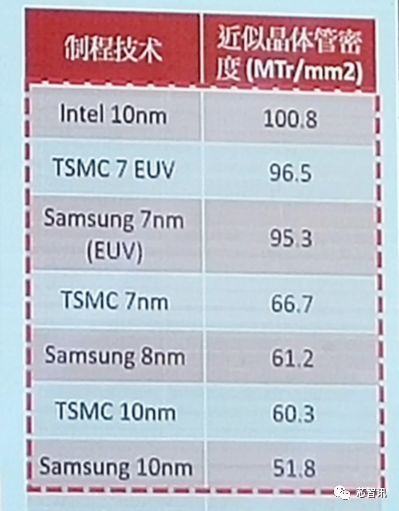

随着英特尔的半导体制程工艺推进速度越来越慢,10nm工艺也是在多次跳票之后才在今年量产,外界关于“摩尔定律已死”、“台积电超越英特尔”的声音也是不绝于耳。但是,实际上,如果我们以晶体管的密度来看,英特尔的10nm工艺实际上是优于台积电7nm EUV工艺的(英特尔10nm工艺的晶体管密度为100.8MTr/mm²,台积电的7nm EUV工艺的晶体管密度为96.5MTr/mm²)。而在接下来的十年内,英特尔仍希望继续推动摩尔定律走下去。

在近日的 IEEE 国际电子设备会议(IEDM)上,ASML CEO披露了英特尔 2019 ~ 2029 年的芯片制造路线图,从 7nm、5nm、3nm、2nm,一直展望到了 1.4nm 。除了单纯的数字目标之外,还曝光了英特尔围绕即将到来的制程节点的一些新技术。

不过,外媒指出,其实在今年9月的光刻会议上,英特尔公司已经展示过此幻灯片,但是此次ASML CEO展示的PPT是基于之前的PPT做了修改,并非英特尔官方正式发布的版本。英特尔官方的原版并未公布各个时间的制程节点数字。

根据曝光的PPT来看,预计英特尔的工艺节点可保持每两年一次升级,首先是从 2019 年的 10nm 工艺、升级到 2021 年的 7nm 极紫外光刻(EUV)工艺。然后是 2023 年 5nm,2025 年的 3nm,2027 年的 2nm,直至 2029 年的 1.4nm —— 这已相当于 12 个硅原子所占的位置。显然,英特尔正计划重回工艺节点每两年一次大升级的节奏。

此外,在两代工艺节点之间,英特尔还会引入“ ” 和“ ”的迭代版本,以充分榨取每代制程的性能。比较例外的是 10nm,它已经处在 10nm 的阶段。因此在 2020 和 2021 年,我们将见到 10nm 和 10nm 。

ASML认为,英特尔能够按照年度节奏来实现这类操作,但也有专门的团队来确保一个完整的制程节点可与另一个制程节点重叠。有趣的是,幻灯片中竟然还提到了反向移植(Back Porting),这是芯片设计时就考虑的一种能力(在较旧的 “ ”节点上重新制作)。

尽管英特尔正在将芯片设计从工艺节点中剥离出来,但由于制程已被锁定,其在具体实施上并不是一件简单的事情。从幻灯片来看,反向移植仍存在着一定的限制,比如第一代 7nm 设计可反向移植到 10nm ,5nm 均支持回退至 7nm ,3nm 可移植到 5nm ,以及 2nm 到 3nm 。

需要指出的是,这并不是英特尔首次提及反向移植硬件设计。由于当前一代 10nm 制程拖了后腿,英特尔已经考虑到了 10nm 和 10nm 的退路。通常随着制程节点的发展,每一次大版本迭代都有不同的团队来负责。但幻灯片指出,英特尔正在开发 10nm 优化和 7nm 系列制程工艺。

展望未来,我们还将见到基于 10nm 芯片设计的 7nm 产品、基于 7nm 设计的 5nm 产品、以及基于 5nm 设计的 3nm 产品。

值得一提的是,2023 年的 5nm 制程节点,刚好也是 ASML 开售其 High NA EUV 光刻机的时间,此外英特尔还一直在考虑新材料和新的晶体管设计。

此外,在今年的 IEDM会议上,英特尔还介绍了可以实现更为先进制程的“2D自组装”材料,尺寸大约为 0.3nm 。当然,要想成功的走向量产还有很多的问题需要解决。

关于自组装材料可以查阅芯智讯此前文章:《芯片制造行业的新方向:“自组装”技术解析》

编辑:芯智讯-浪客剑 资料来源:TechSpot、cnbeta

国产存储产业崛起已成必然:2023年长江存储将赶“英”超“美”!

行业交流、合作请加微信:icsmart01

芯智讯官方交流群:221807116