BGA布线中所需的PCB层数和过孔走线的关系

引 言

BGA封装,球栅阵列封装,简称BGA(Ball Grid Array Package),是采用将圆型或者柱状焊点隐藏在封装体下面一种封装形式,90年代后随着集成技术的进步,BGA技术迅速得到发展,现在高密度、高性能、高频率的IC芯片都已经采用这类型的封装技术。因此处理BGA芯片的布局和走线已经成为工程师的必修功课,本文介绍了PCB层数和过孔之间走线布线。

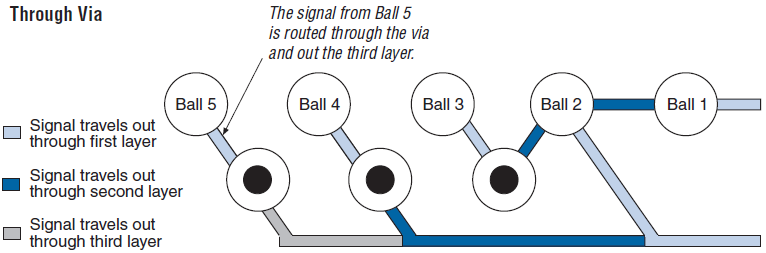

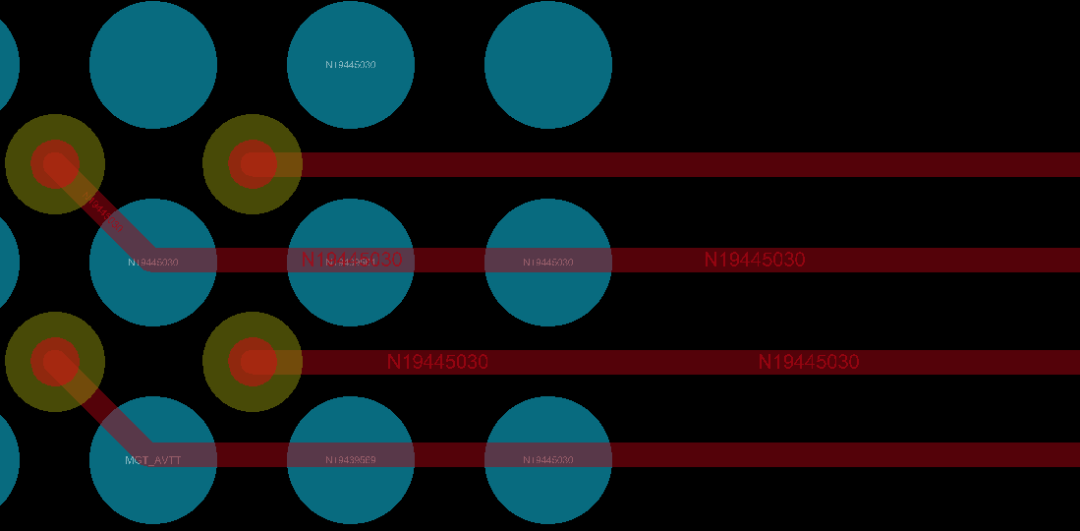

(1)过孔采用通孔设计中,5个BGA焊盘球需要三层进行出线,因布线不能在贯通孔下面通过,第一个和第二个焊盘球可以表层出线,第三个和第四个焊盘球要通过孔换到第二个层中出线,第五个焊盘球必须通过一个过孔换到第三层出线。

5个BGA焊盘球通孔设计出线

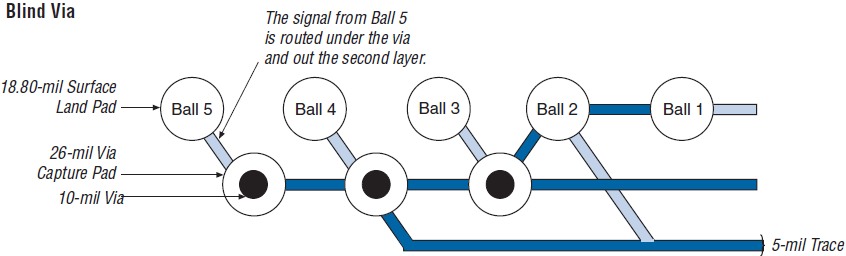

(2)过孔采用盲孔设计中,5个BGA焊盘球需要两层进行出线,因布线能在盲孔下面通过,第一个和第二个焊盘球可以表层拉出线,第三个和第四个焊盘球要通盲孔换到第二个层中出线,第五个焊盘球必须通过一个盲孔换到第二层,从第三个和第四个焊盘球的下面进行出线。

5个BGA焊盘球盲孔设计出线

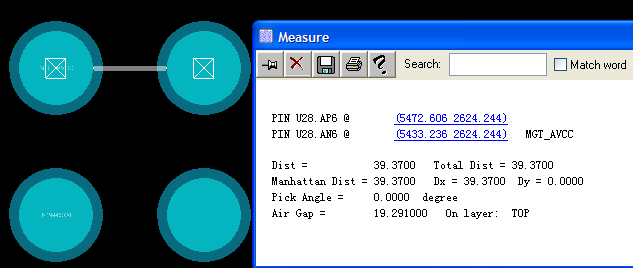

以Xilinx Virtex-6 FPGA,6VLX240TFF1156的1156 Ball Flip-BGA芯片 BGA FF1156为例。

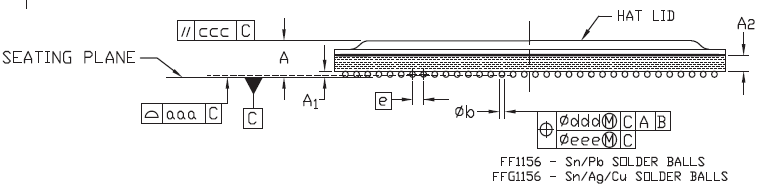

(1)读该芯片手册获取焊盘的间距和焊盘的直径及引脚排列方式引脚的数量等信息。

6VLX240TFF1156平视图

6VLX240TFF1156侧视图

6VLX240TFF1156平视图

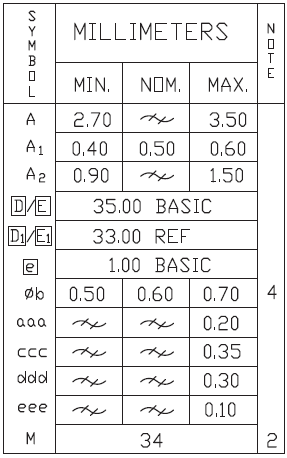

(2)该芯片采用Flip-BGA芯片 BGA封装方式,共计有1156个焊盘球引脚,34行34列,引脚间距1.0mm,焊盘球直径最小0.51mm,标准0.6mm,最大0.7mm。PCB设计中焊盘采用MSMD的焊盘方式,标准直径0.6mm的焊盘,PCB的焊盘设计采用0.6mmX85%为0.51mm,阻焊层采用直径0.70mm。设置完成后焊接制作界面截图如下图所示。

BGA焊盘设计

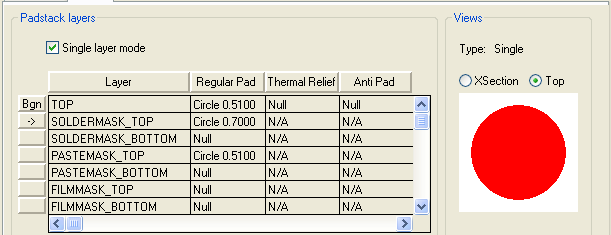

(3)测量BGA引脚之间的间距为39.37mil(1.0mm),两个焊盘之间平行布线区域为19.2910mil。对角线之间的距离为78.74mil,对角线之间两个焊盘内布线区域为35.598588mil。因为BGA的引脚和信号线都较多,为了能够将引脚都引出,应该采用过孔焊盘成对角线出线摆放方式进行。

BGA引脚水平间距是39.37mil

对角线之间的距离为78.74mil

(4)计算线宽、间隙及过孔。若两个焊盘之间走一条线,两个焊盘之间平行布线区域为19.2910mil,考虑到余量计算采用17.2910mil进行。若线宽5mil,间隙6mil,那么总的布线区域为17mil((2X6)+5),17mil小于19.2910所以设置参数符合要求。对角线之间两个焊盘内布线区域为35.598588mil,考虑到余量计算采用33.598588mil进行,33.598588减去两倍间隙12mil(2*6)为21.59598588,也就是说,过孔的最大焊盘直径应该小于21.59598588mil,取个常用的参考值过孔用钻孔10mil,焊盘20mil就很合理。该处为了能让大家更明白计算关系,列图标进行说明。

6VLX240TFF1156 布线参数设置(两个焊盘之间走一条线) | ||||||

BGA焊盘球 | PCB采用MSMD的焊盘 | 平行布线区域 | 对角线区域 | 布线线宽 | 布线间距 | 过孔尺寸 |

0.6mm | 焊盘直径0.51mm,阻焊层直径0.70mm | 19.2910mil | 35.598588mil | 5mil | 6mil | 20/10mil |

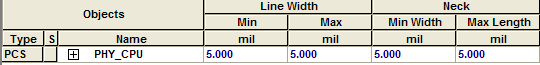

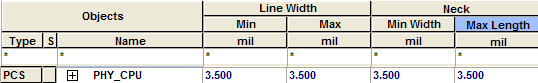

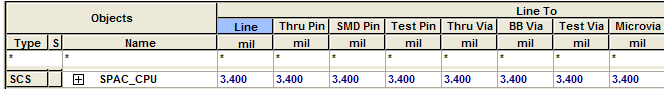

(5)按照计算的线宽、线距、设置约束规则。新建立线宽约束规则5mil,将新建立的线宽规则应用到6VLX240TFF1156芯片的网络中,新建立间距约束规则6mil,将新建立的线宽规则应用到6VLX240TFF1156芯片的网络中。

新建立间距约束规则SPAC_CPU

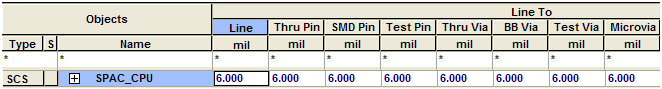

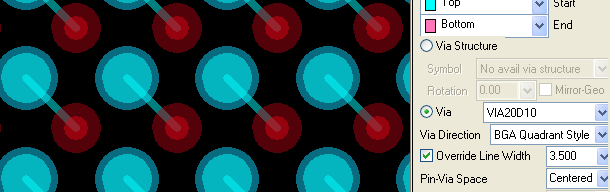

(6)新建立20/10mil过孔,通过Fanout命令对6VLX240TFF1156芯片扇出操作,Override Line width文本框中设置扇出线宽采用5mil。

对6VLX240TFF1156芯片扇出

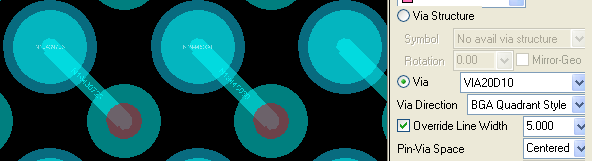

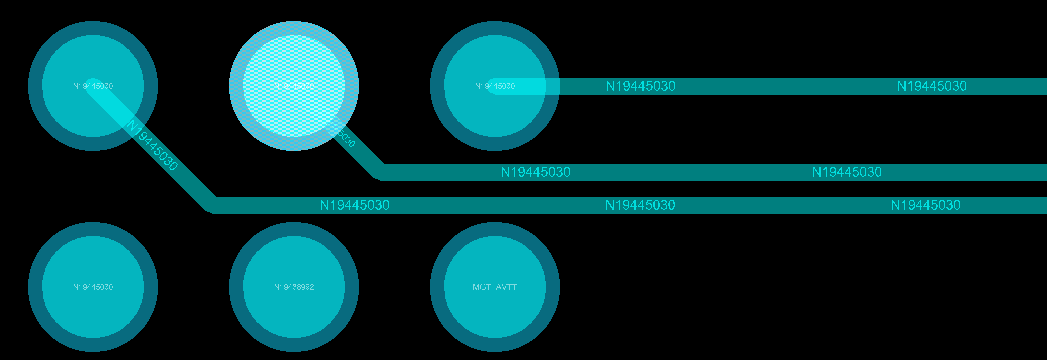

(7)芯片扇出后,进行布线操作,芯片每个边上的最外面的两排焊盘都可以采用表面拉线的方式进行出线操作。

采用表面拉线的方式进行出线

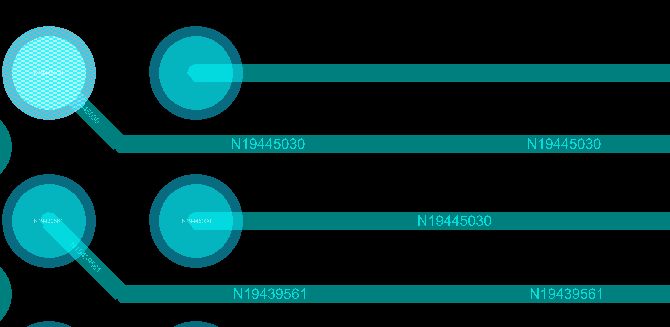

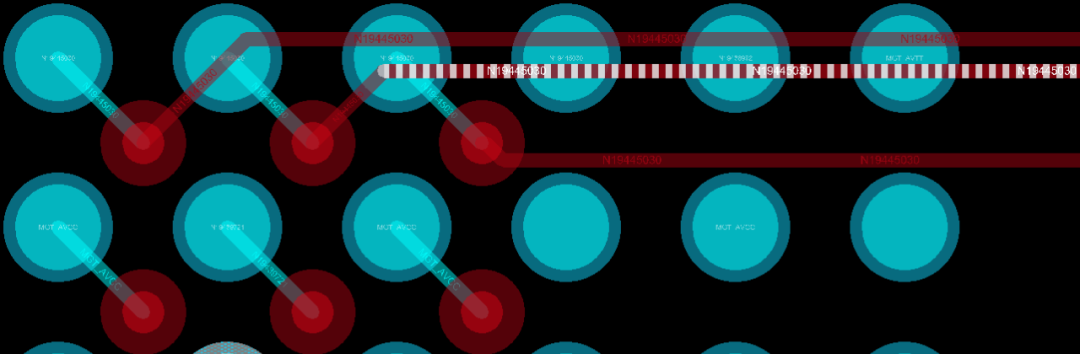

(8)芯片的第三排和第四排,通过孔换到第三层层,在内层第三中拉出走线(内层第二层通常用作参考层GND)。

在内层第三中拉出走线

(9)芯片的第五排,通过孔换到第四层,在内层第四中拉出走线。

在内层第四中拉出走线

(10)计算线宽、间隙及过孔。若两个焊盘之间走两条线,两个焊盘之间平行布线区域为19.2910mil,考虑到余量计算采用17.2910mil进行。若线宽3.5mil,间隙3.4mil,那么总的布线区域为17.2mil((3X3.4)+7)=17.2mil小于19.2910所以设置参数符合要求。对角线之间两个焊盘内布线区域为35.598588mil,考虑到余量计算采用33.598588mil进行,33.598588减去三倍间隙10.2mil(3*3.4)为21.39598588,也就是说,过孔的最大焊盘直径应该小于21.39598588mil,取个常用的参考值过孔用钻孔10mil,焊盘20mil就很合理。该处为了能让大家更明白计算关系,列图标进行说明。

6VLX240TFF1156 布线参数设置(两个焊盘之间走两条线) | ||||||

BGA焊盘球 | PCB采用MSMD的焊盘 | 平行布线区域 | 对角线区域 | 布线线宽 | 布线间距 | 过孔尺寸 |

0.6mm | 焊盘直径0.51mm,阻焊层直径0.70mm | 19.2910mil | 35.598588mil | 3.5mil | 3.4mil | 20/10mil |

(11)按照计算的线宽、线距、设置约束规则。新建立线宽约束规则3.5mil,将新建立的线宽规则应用到6VLX240TFF1156芯片的网络中,新建立间距约束规则3.4mil,将新建立的线宽规则应用到6VLX240TFF1156芯片的网络中。

(12)新建立20/10mil过孔,通过Fanout命令对6VLX240TFF1156芯片扇出操作,Override Line width文本框中设置扇出线宽采用3.5mil。

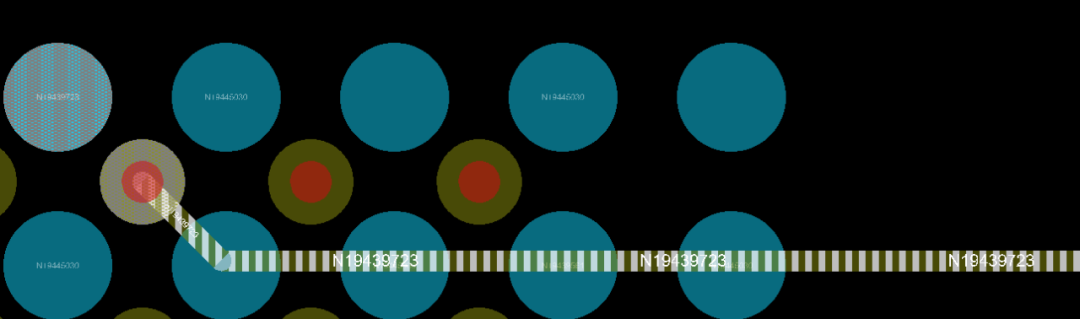

对6VLX240TFF1156芯片扇出操作

(13)芯片扇出后,进行布线操作,芯片每个边上的最外面的三排焊盘都可以采用表面拉线的方式进行出线操作,如下图24.33所示。

采用表面拉线的方式进行出线操作

(14)芯片的第四排、五排、第六排,通过孔换到第三层层,在内层第三中拉出走线(内层第二层通常用作参考层GND)。

在内层第三中拉出走线

北京耀华创芯电子科技有限公司(英文:U-Creative Technology Limited,以下简称耀创科技),是一家专注于从事电子设计自动化(EDA)服务的高科技公司,是Cadence在国内合作时间最长的代理商。

耀创科技公司的管理和服务团队人员均拥有多年的EDA从业经验,公司自成立以来,为来自国内各区域和行业数百家的客户提供了优质的服务。

耀创科技通过十几年的发展,我们积累了丰富的EDA产品市场与服务经验,已经帮助国内多家客户成功地使用EDA产品,极大地提高了这些客户的电子设计水平和生产效率。在引进国外先进的EDA工具的同时,我们针对中国市场的特殊性,与Cadence公司合作,在国内最早提出了电子设计与数据管理平台的概念,开发出具有自主知识产权的电子电气设计集成数据管理平台CMS Suite,成功地在一些研究所及商业公司内进行实施,极大的加速了板级产品的标准化设计流程,覆盖从优选元件选控、协同设计输入、在线检查分析、标准化文档输出及PLM/PDM系统集成,在业界获得一致好评。与此同时,根据国内客户的实际情况,我们还提供除了软件使用培训之外的项目陪同设计服务,以帮助客户在完成实际课题的同时能够熟练掌握软件的使用,这一举措也取得了非常好的效果。

我们一直秉承“与客户共同成长”的服务理念,希望在国内EDA领域内能为更多客户提供支持与服务!

耀创深圳

www.u-c.com.cn

欢迎您的留言长按扫码可关注