台积电公布5nm生产技术平台细节

EETOP专注芯片、微电子,点击上方蓝字关注我们

来源:EETOP翻译自semiwiki

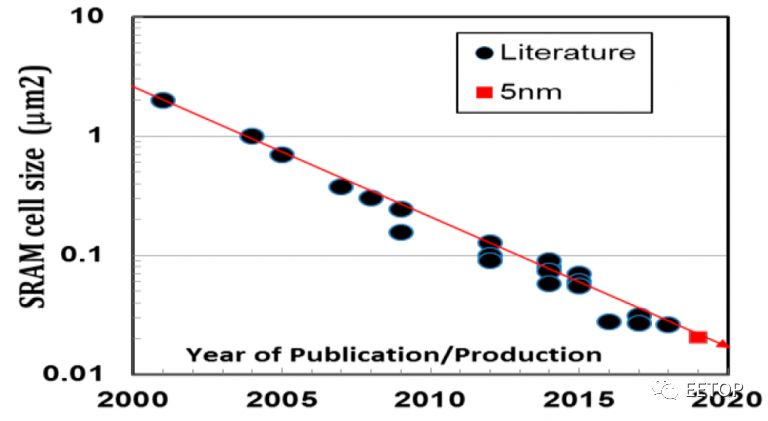

早在2019年4月,台积电宣布将在风险生产中引入其5nm技术,在IEDM 2019上,台积电对经过1000小时HTOL并将于2020年1H投入量产的5nm工艺进行了详细描述。这种5nm技术是一种从7nm节点扩展到全节点的技术,使用主要设计规则(栅极、鳍和Mx/Vx节距)的智能扩展来提高成品率,具有0.021um2 的SRAM单元和领先于计划的下降缺陷密度D0。

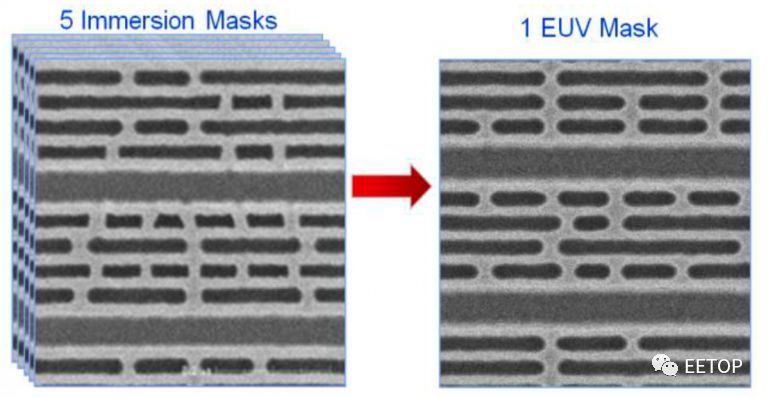

5nm技术平台成功的主要原因是实现了极紫外(EUV)光刻技术。成熟的EUV在切割、接触、通孔和金属线掩蔽步骤上至少替换了至少四倍的浸没层,从而缩短了周期时间,提高了可靠性和良率。

5nm中的总掩模数量比以前的7nm节点少几个。图1显示了一个EUV掩模如何代替五个浸没掩模,又如何产生更好的图案保真度,更短的循环时间和更少的缺陷。

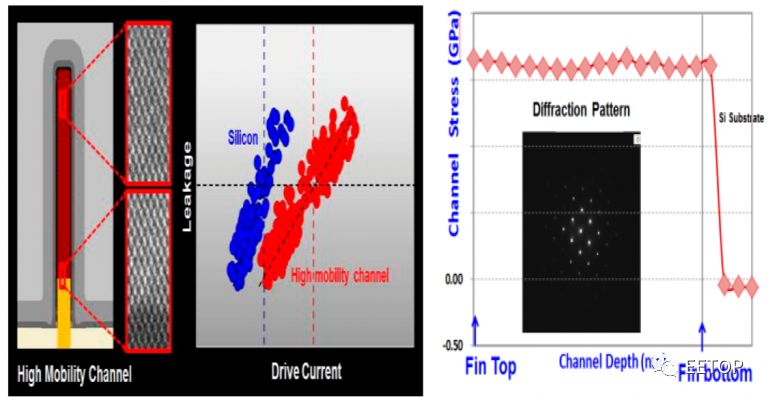

从16nm节点到7nm,FinFET已经使用了四代,但作为沟道迁移的性能一直停滞不前。为了解决这个问题,采用了高移动性信道(HMC)以提高性能。图2中的TEM显示了与Si晶格常数相接的完全应变HMC晶格常数。

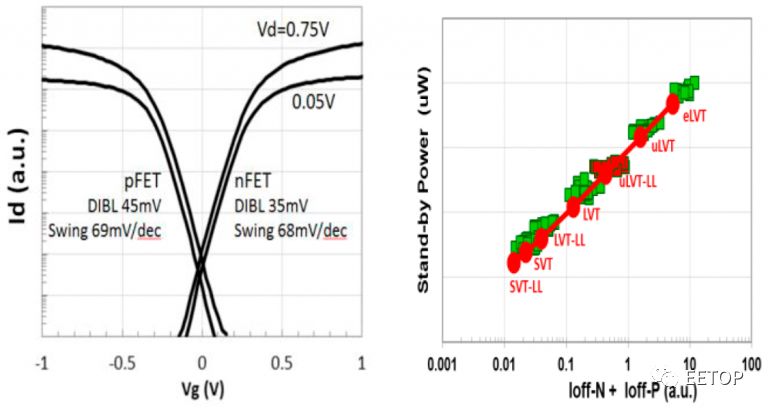

HMC finFET具有出色的Id-Vg特性,如图3所示,并且产生的驱动电流比Si finFET高出约18%。品质因数(FOM)环形振荡器的待机功率也与晶体管泄漏密切相关。

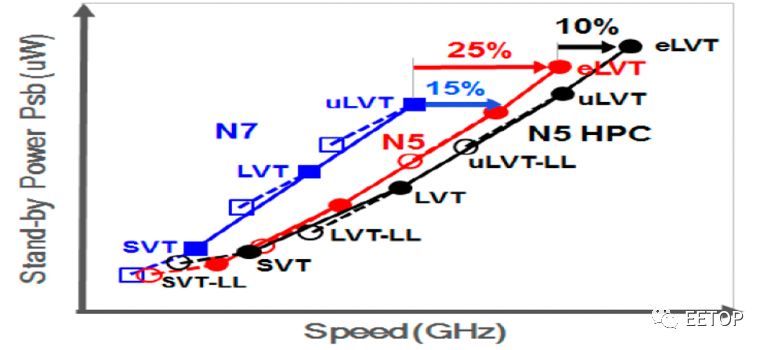

这种5nm CMOS平台技术是IEDM 2016中描述的7nm工艺的完整节点扩展。如图4所示,每个晶体管类型最多可提供7个Vt,这使得产品设计能够满足移动SoC的功率效率需求以及高性能计算的峰值速度需求。

HPC的新功能是极低的VT(eLVT)晶体管,其在7nm处的峰值速度提高了25%,并采用三鳍标准单元,从而使性能进一步提高了10%。该技术可用于使用混合键合的3D芯片堆叠。除了相对于7nm而言令人印象深刻的密度和性能提升之外,该技术还获得了1000小时HTOL认证,相对于7nm技术而言,它具有改善的应力老化特性。超出计划的高良率SRAM和逻辑缺陷密度D0。能够实现这一进展的技术成果包括可以完全实施EUV和高迁移率沟道(HMC)finFET。

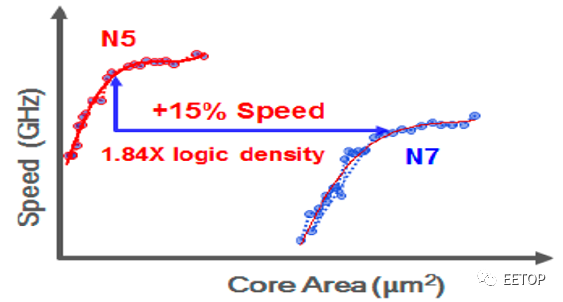

设计和开发此5nm平台技术是为了满足PPACT的目标(功率,性能,面积,成本和上市时间)。设计技术协同优化(DTCO)强调了智能缩放,避免了brute-force 缩放,因为brute-force 缩放会导致工艺成本和产量影响急剧增加。栅极-接触-扩散和独特的扩散终止以及基于EUV的栅极图案等设计功能可降低SRAM的尺寸并提高逻辑密度。5nm技术在7nm节点的逻辑密度为1.84倍的情况下,在相同功率下的速度提高了15%,在相同速度下的功率降低了30%,如图5所示。

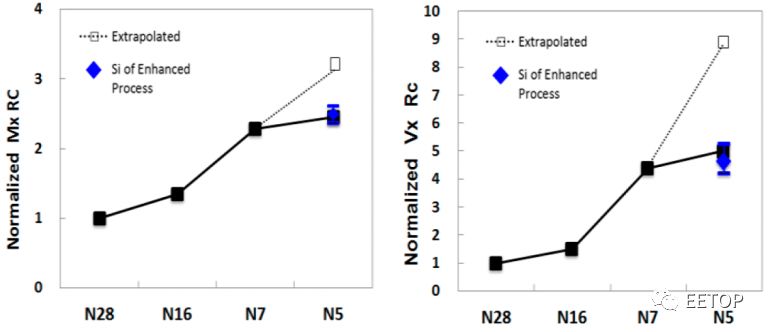

互连延迟会严重影响产品性能,并且每一代互连延迟都会变得越来越差。从N28到N5,后端金属RC和过孔电阻如图6所示。通过EUV图案化,创新的按比例缩放的势垒/衬里ESL / ELK电介质和Cu回流焊,最紧密的间距Mx RC和Vx Rc保持与7nm节点相似。

SRAM密度和性能/泄漏对于移动SoC和HPC AI是至关重要的。在 F2 的特征尺寸方面,具有更高级节点的SRAM单元的缩放变得越来越困难。如图7所示,所提供的高电流(HC)和高密度(HD) SRAM电池的电池面积分别为0.025um2 和0.021um2 ,是业界密度最高的器件。实现了始终如一的256 Mb SRAM高良率,逻辑测试芯片的峰值良率大于90%,平均良率约为80%(无需维修)。

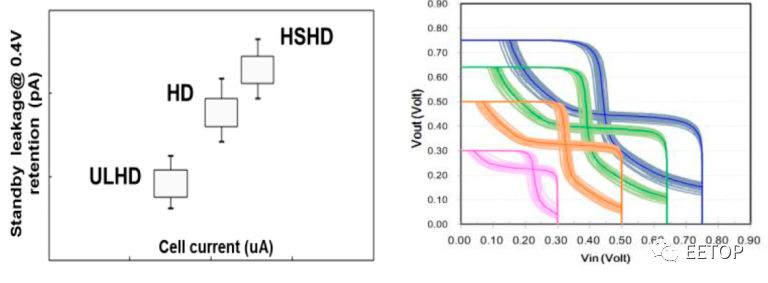

超低泄漏的ULHD可用于降低保留泄漏,提高功率效率,而高速HSHD SRAM可作为HC SRAM单元的替代方案,从而使存储区域减少约22%,如图8所示。

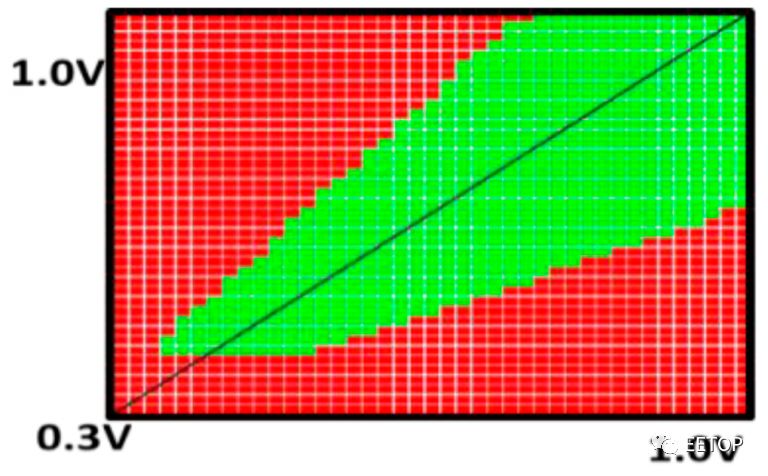

具有完整读/写功能的256Mb 0.021um2 HD SRAM单元的shmoo图在图9中显示为低至0.4V。

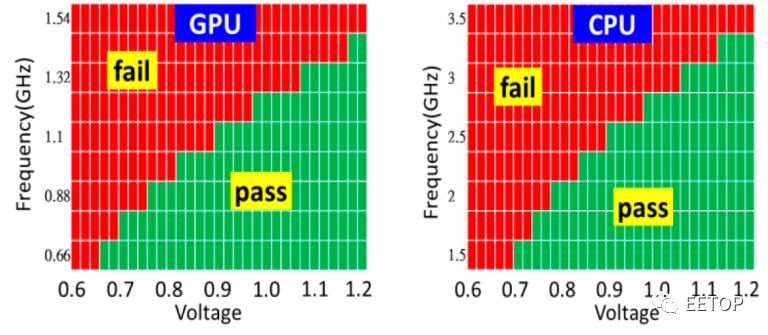

图10显示了高良率逻辑测试芯片中GPU和CPU模块的频率响应shmoo图。

图10. 5nm鉴定工具中高良率逻辑测试芯片中GPU和CPU模块的GHz频率与电压的Shmoo曲线。

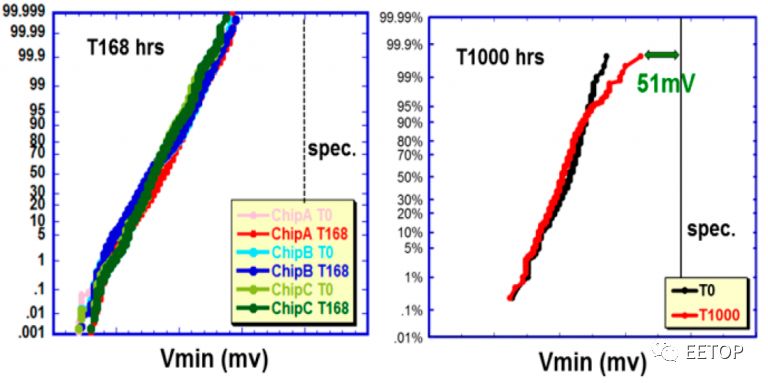

256Mb HD/HC SRAM和逻辑测试芯片通过了1000小时的HTOL认证。SRAM Vmin在168小时时的变化可以忽略不计,并且以约51mV的裕度通过了1000小时的HTOL,如图11所示。

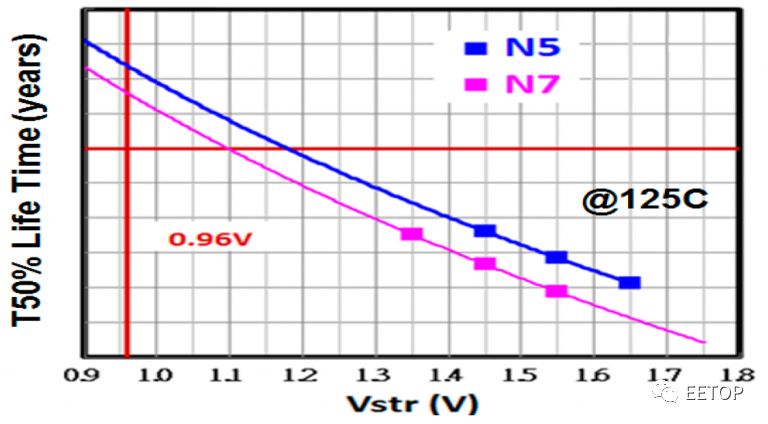

使用图12所示的高迁移率沟道finFET制成的5nm FOM环形振荡器在0.96 V和125C时的应力老化数据,相对于7nm节点具有更好的老化性能。

HPC的另一个重要功能是在BEOL金属化层的上层中形成的金属-绝缘体-金属(MiM)电容器。5nm节点MiM的电容密度是典型HD-MiM的4倍,并通过最小化瞬态下降电压使Fmax快约4.2%,并在CPU测试芯片中将Vmin降低了约20mV。

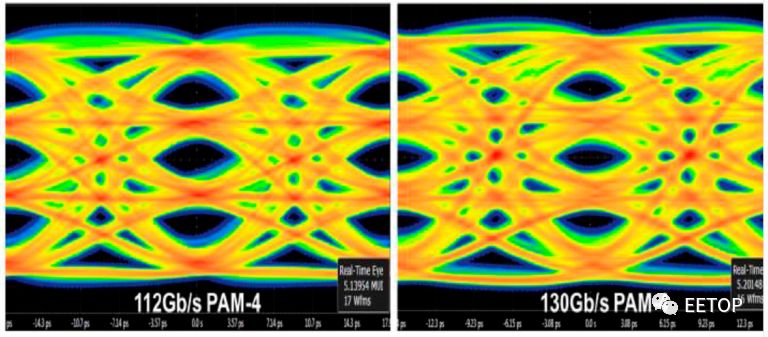

HPC严重依赖于高速IO,尤其是SERDES。通过使用特殊的高速设备成功优化finFET驱动强度和电容/电阻,PAM-4 SERDES发射机速度在0.78 pJ/bit时为112Gb/s,在0.96pJ/b时为130Gb/s,如图13所示。

总而言之,台积电提供了一个极具竞争力的技术平台,确立了其在同类最佳的最高密度逻辑技术领域的领导者地位。2020年上半年的批量生产将使先进的SoC产品在移动设备(尤其是5G)以及用于AI,数据中心和区块链产品的HPC应用中实现领先,这些产品越来越需要高性能和最佳能效。

推荐:创新大讲堂

点击阅读原文看创芯大讲堂更多好课