Cadence 17.4功能更新| OrCAD Capture和Allegro支持约束规则的双向设置及同步

Cadence OrCAD Capture 是一款多功能的PCB原理图输入工具。新发布的OrCAD Capture17.4作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。

OrCAD Capture 17.4有很多新功能更新,我们梳理很多资料后发现,OrCAD Capture和Allegro已经支持约束规则的双向设置及同步,双向的规则设置和同步是困扰很多工程师的大问题。之前很多做原理图的工程师都是将规则手写表格或者做成要求的邮件发送给PCB设计的工程师,导致传递效率低下,且这样的同步方式经常存在遗漏和相互之间的隔阂。为了解决这个问题,在17.4的版本,OrCAD Capture可以直接调用Constraint manager约束管理,在电路设计的过程中就可以直接进行约束规则的设置,直接将设置好的规则同步到Allegro PCB文件中。同时支持在Allegro PCB文件调用Constraint manager约束规则的设置,然后反向同步到原理图中,这样就实现了约束规则的100%同步,让PCB Layout和原理图之间的链接更加紧密,提高规则设计的效率,并督导工程师及时纠正这些设计错误和存在的问题,为电路的原理图设计打下坚实基础。

接下来将重点讲述OrCAD Capture和Allegro的规则设置方法及同步技巧,一起学习双向同步的设置办法和操作细节。

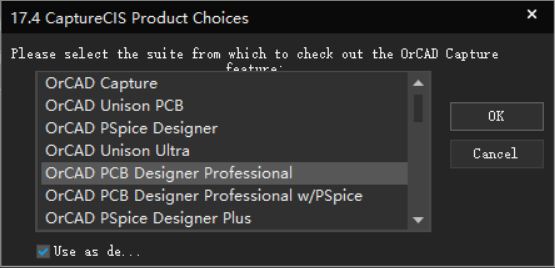

开启OrCAD Caputre软件的时候需要选择PCB Designer Professional的产品包,选择该产品包需要获得License的支持。

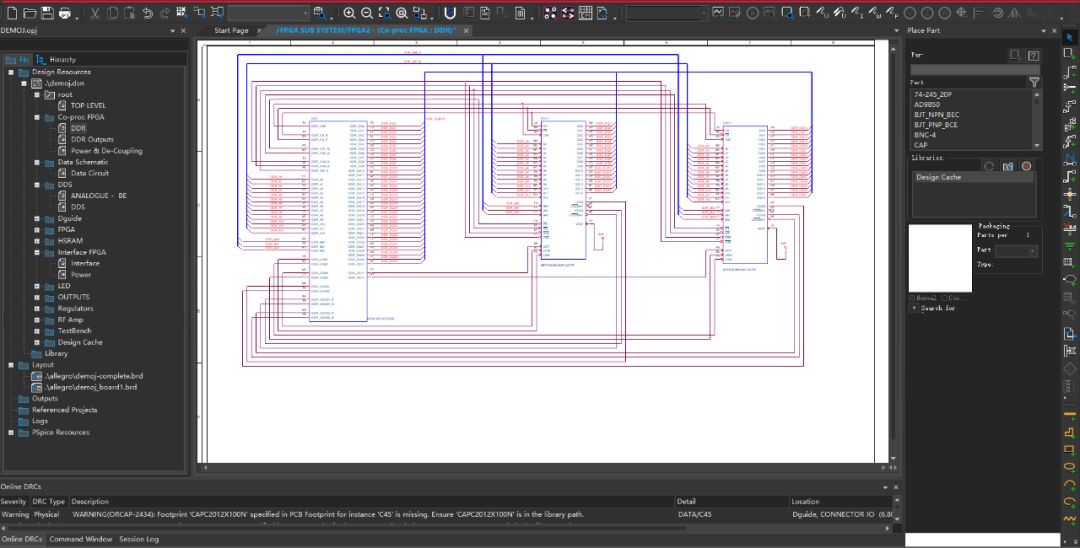

打开DEMO的工程文件,预览工程文件,检查文件。阅读熟悉文件里面的电路互联关系,熟悉电路的模块,比如电源、DDR内存、FPGA等部分的电路模块链接关系。检查GND和电源的全局属性关系,看GND和电源是否有做规律,信号的类型设置是否正确。

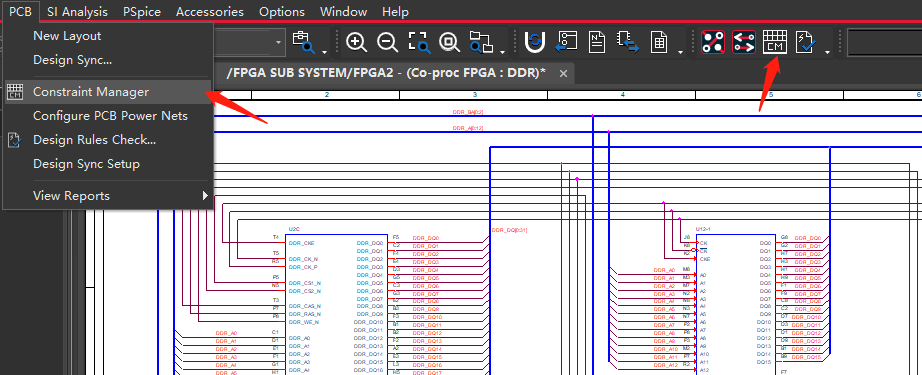

选择PCB--Constraint manager命令或者点击CM的图标,开启约束管理器进行约束规则的设置。

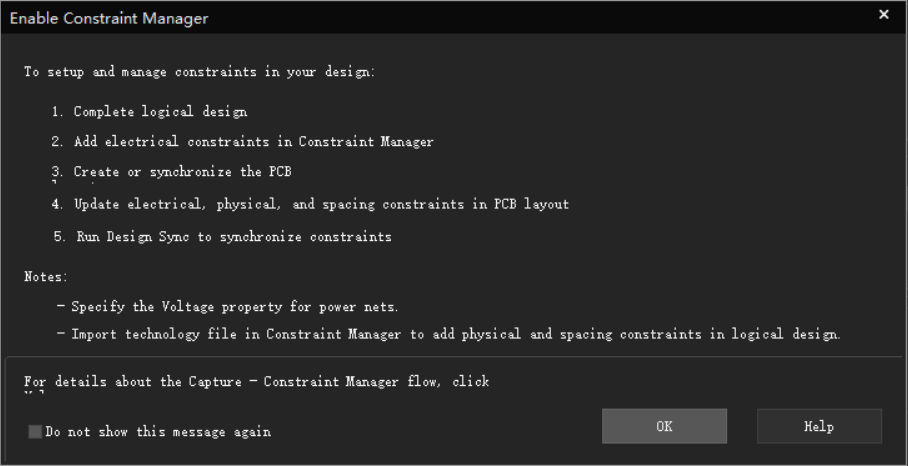

执行Enable Constraint manager启动约束管理器。在这里执行约束管理使用规范,共计有5条。大家可以关注下这5条的说明,需要执行约束规则就要按照该办法来进行操作。启动约束管理器Capute会添加电气约束到规则管理器,创建同步的PCB Layout文件,更新设置的电气规则,物理约束和间距规则同步到PCBLayout文件里面完成规则同步。

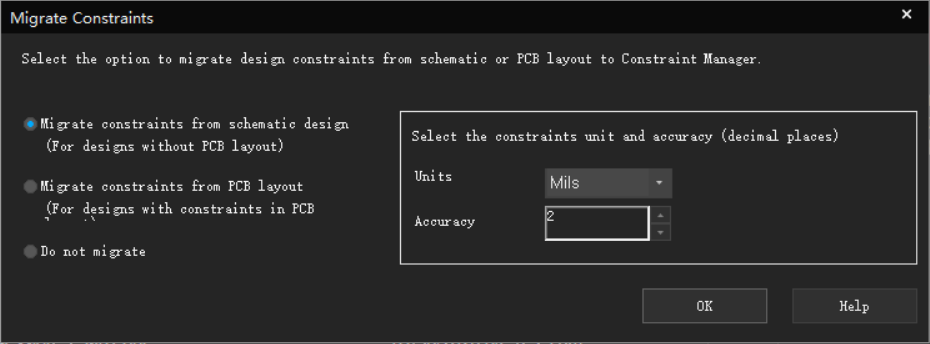

点击OK之后,在弹出的Migrate Constraints进行同步迁移规则的设置,这里我们选择migrate constraints from schematic design,表示执行从原理图迁移设置约束规则。若选择migrate constraints from PCB layout 表示将从PCB layout文件里面读取约束的设计规则,同步到原理图中,相对来说这个正好是反向的同步操作选择。从这里可以看到,从17.4的软件开始执行的是双向同步约束规则的设置。

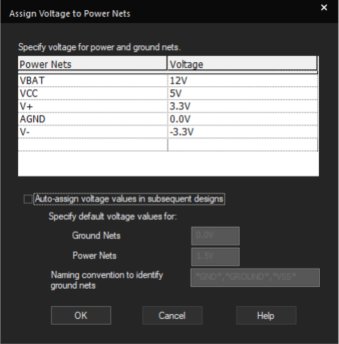

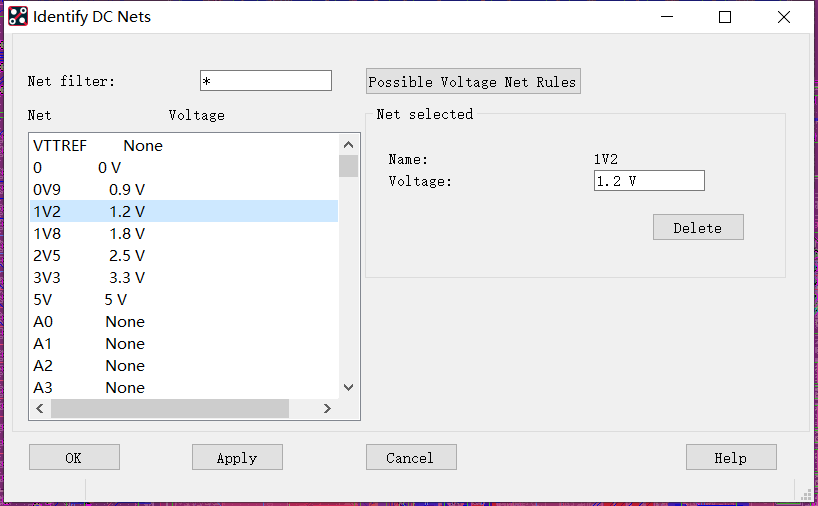

选择OK之后,弹出Assign Voltage to Power Nets的对话框,这个对话框里面主要是用来分配直流和GND的网络,给对应的电源和GND网络都分配成电压,GND分配是0V。软件在这里有个过滤器可以利用过滤器来设置规则检索原理图文件中的电压和GND网络。

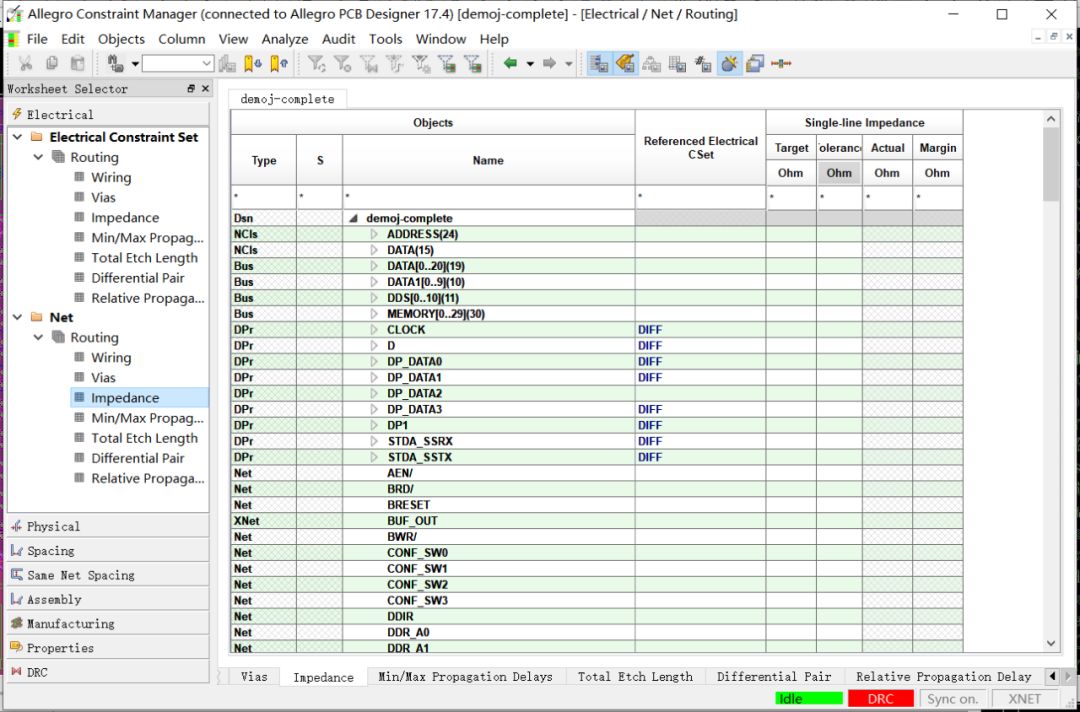

直流电压网络分配完成以后,确认没有错误之后点击OK按钮,软件将执行当前的设置,初始化后开启Constraint manager约束管理器的窗口。

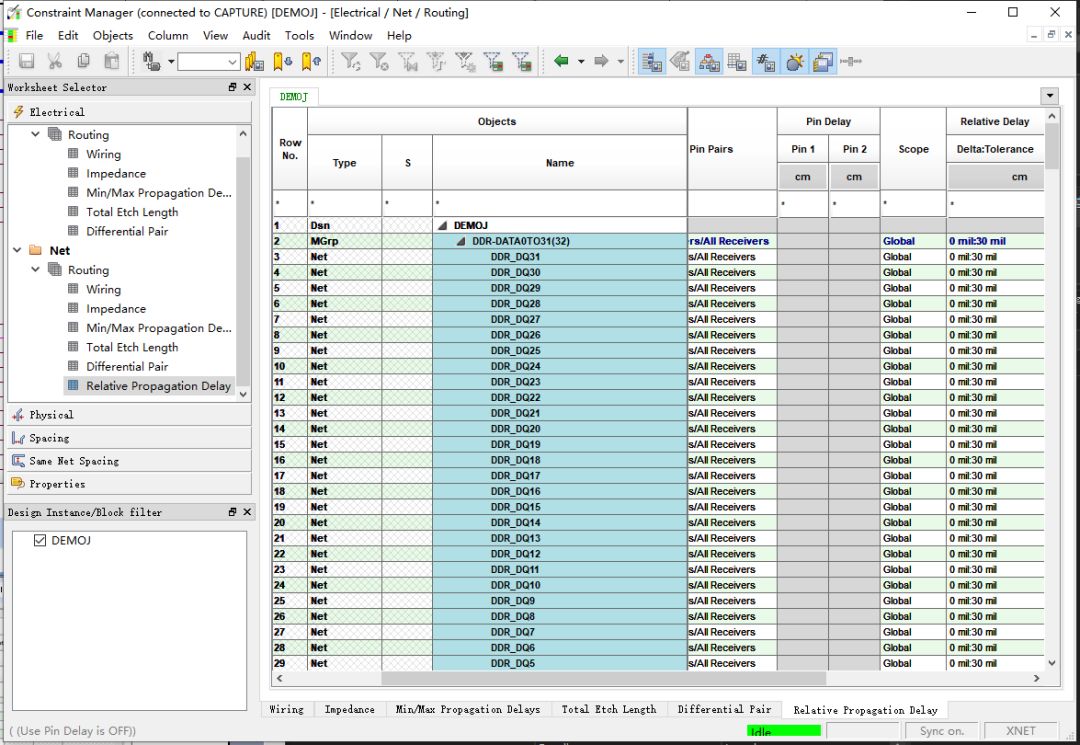

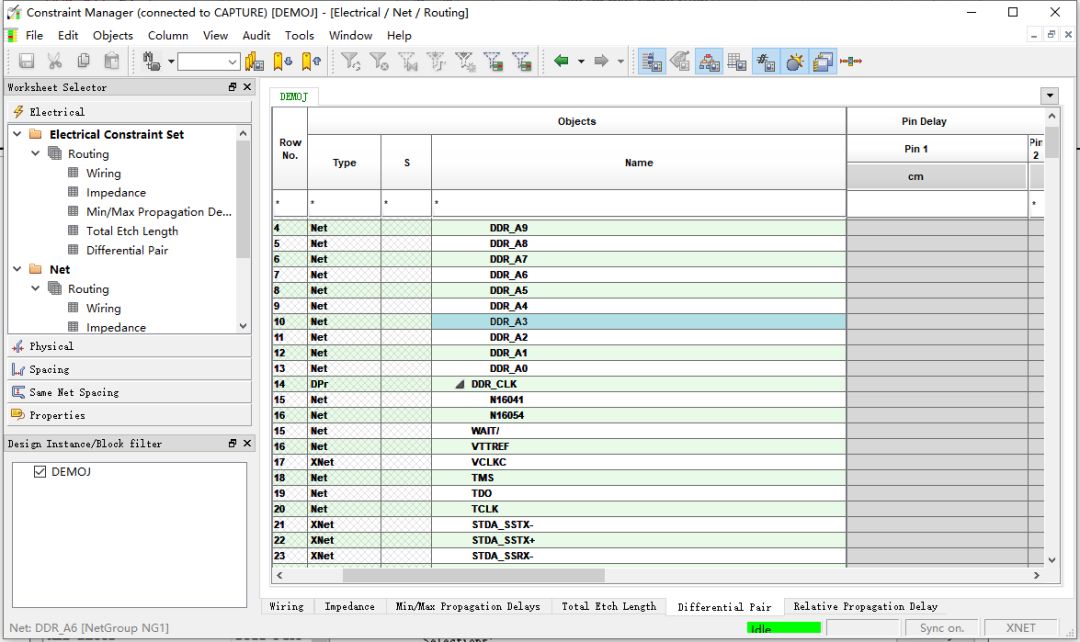

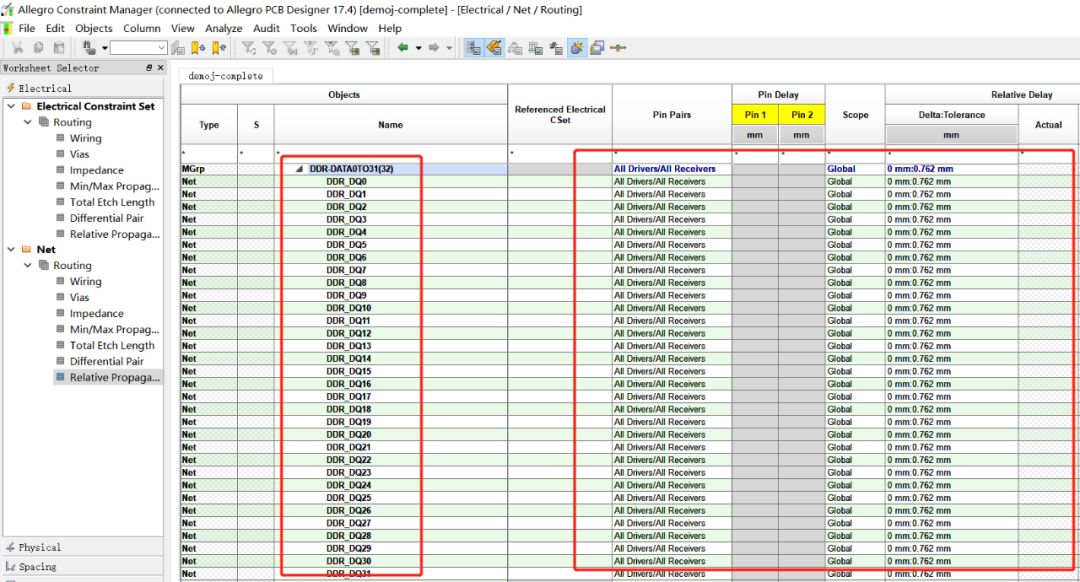

接下来我们约束管理器里面给DDR内存的数据线,DDR_DQ0-31添加一个相对等长的规则。在CM约束管理器里面找到NET-Relative Propagation delay 相对等长的约束页面,选中DDR_DQ0-31的网络,右键添加新建Match Group,新建分组为相对等长分组为DDR-DATA0TO31,约束条件为0mil:30mil。设置完成以后截图如下所示。

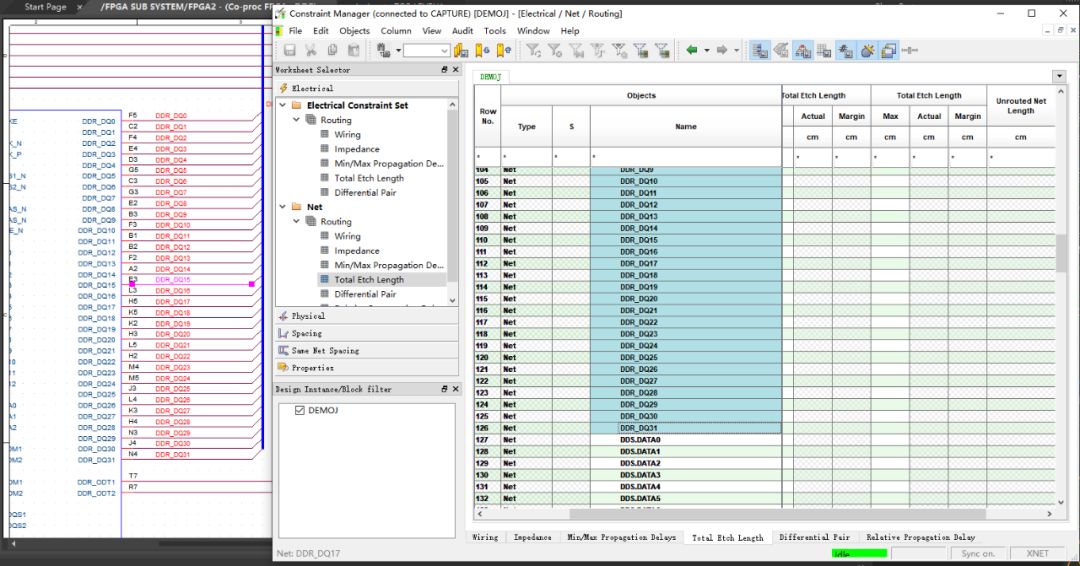

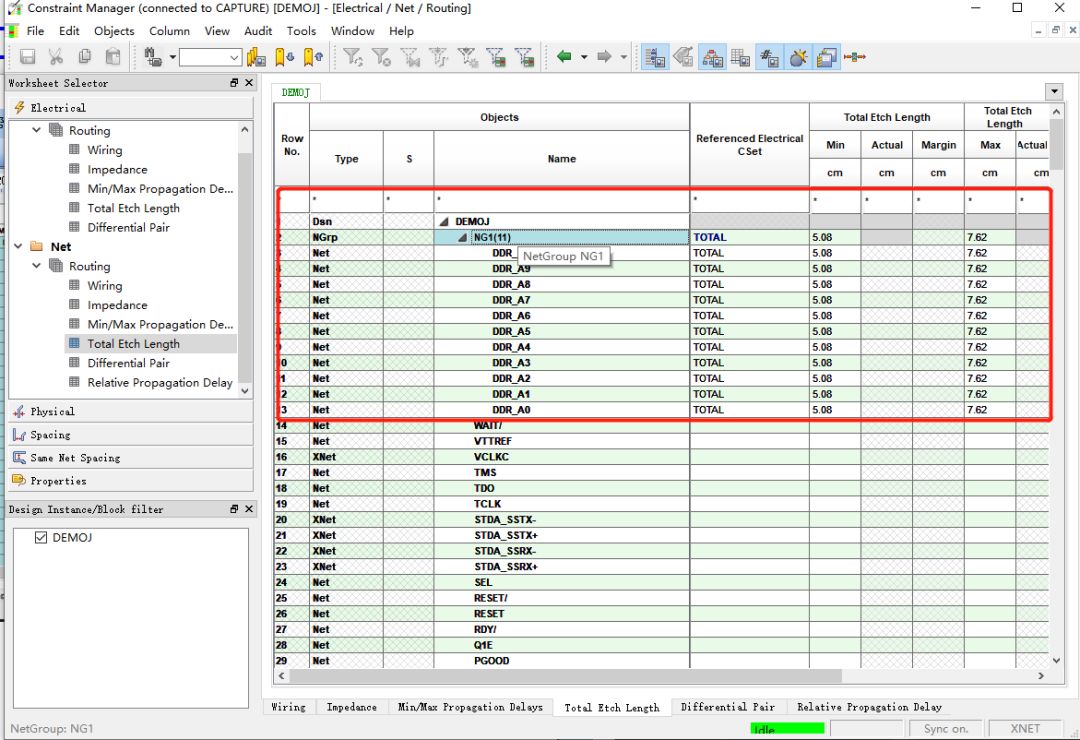

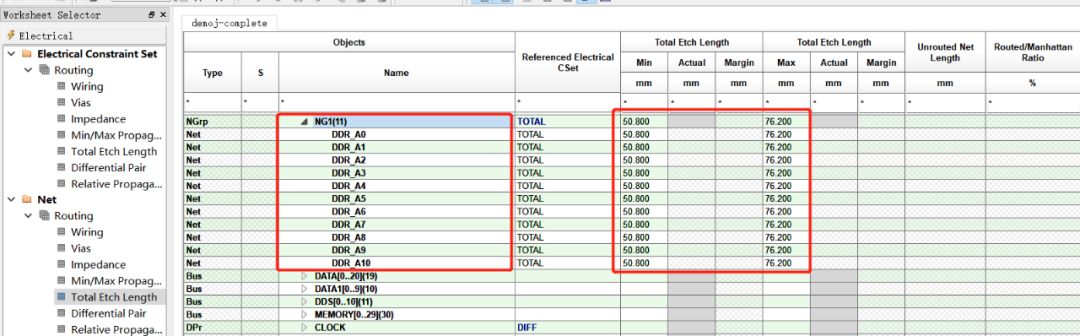

假设再设置一个线长的规则,在CM约束管理器里面找到NET-Total Etch Length的规则页面,找到DDR_A0到A10的网络,创建Group之后,设置该组线的长度为5.08cm到7.62cm。约束该组线的长度在规则设置的范围内才是合格。设置完成以后截图如下所示。

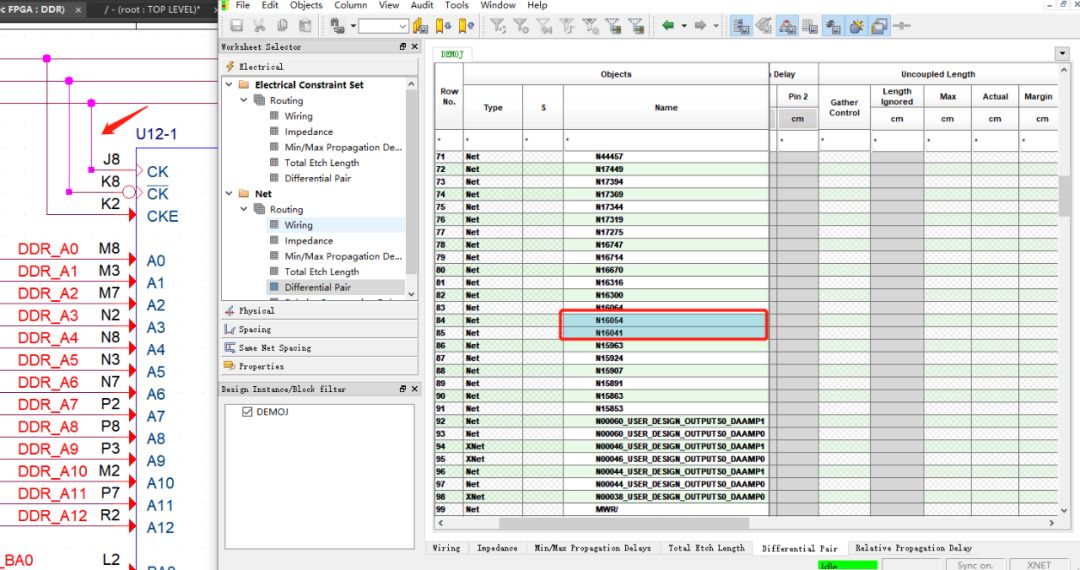

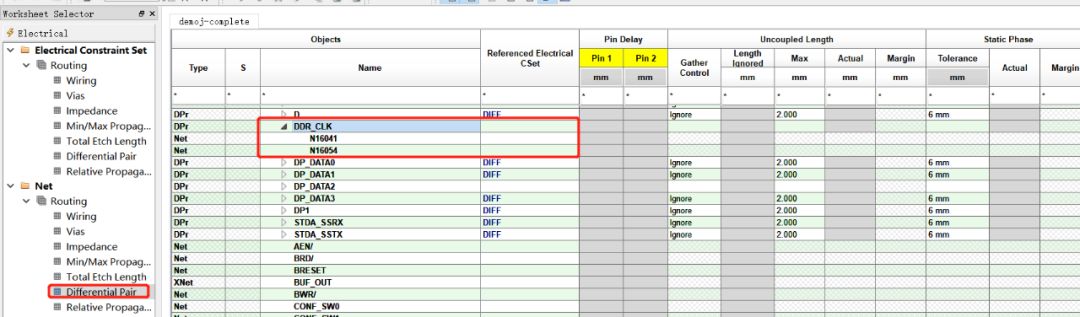

已经能支持同步的网络选择功能。当在原理图里面选择鼠标点击选择N16054和N16041这两个网络之后,在约束管理会跳转同步选中这两个网络。执行后效果如图所示。

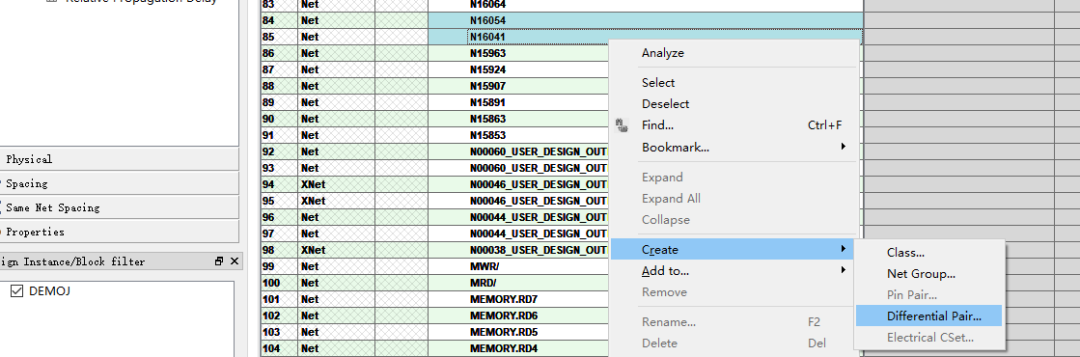

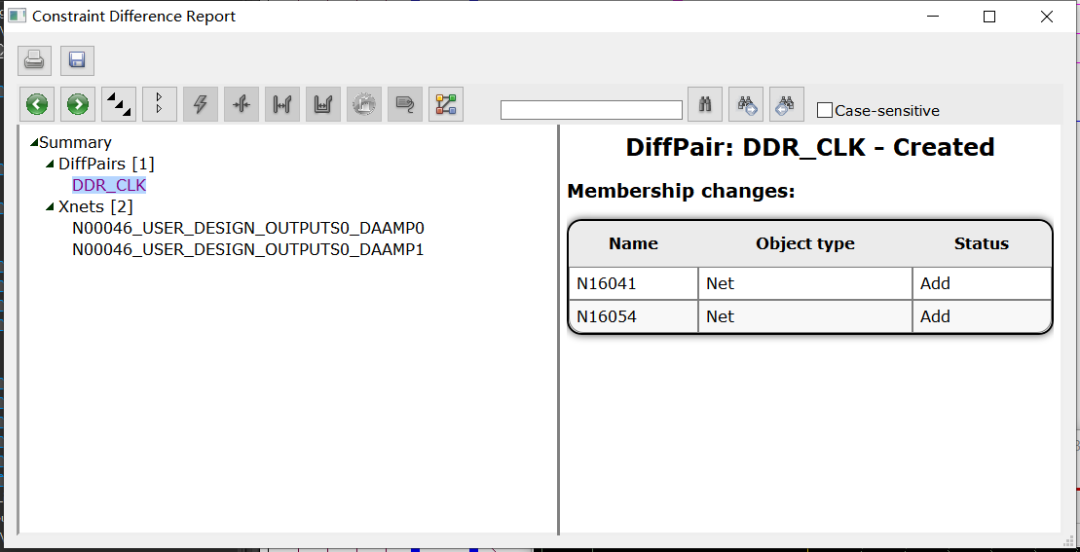

选择N16054和N16041这两个网络之后,点击右键创建差分对网络,这两个网络是DDR的差分时钟,将这两个网络设置成差分对网络。

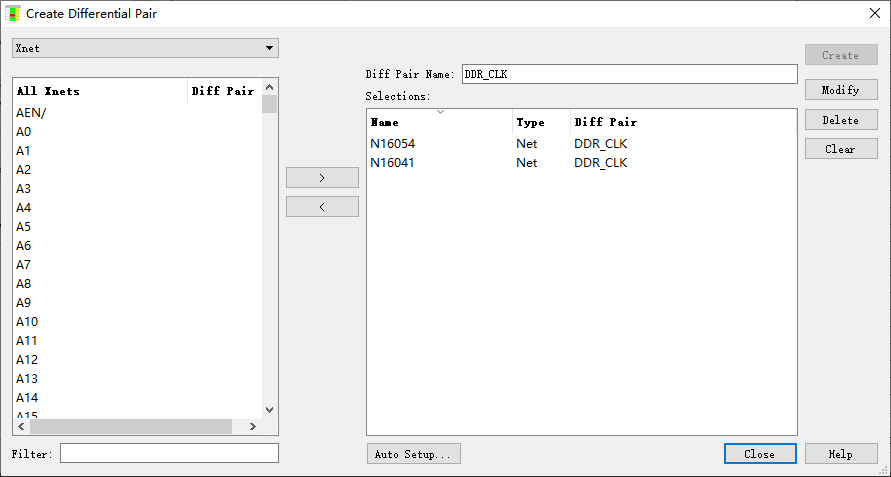

创建成差分对网络以后,如下图所示。

设置规则完成以后,关闭Constraint manager约束管理窗口。约束的规则不用执行保存,因为约束管理器是实时同步的操作,执行后软件会自动进行保存。

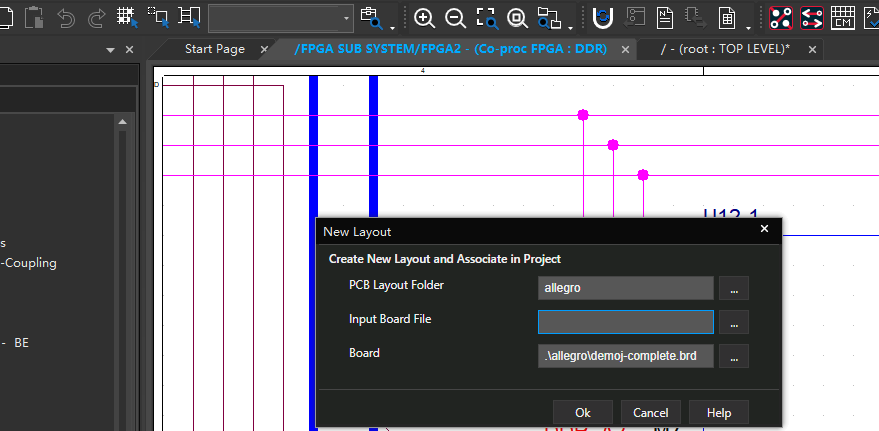

选择生成PCB Layout文件,选择new Layout命令,可以生成新的PCB文件。可以通过新建PCB文件验证刚才设置的规则是否有成功带入到PCB文件里面。

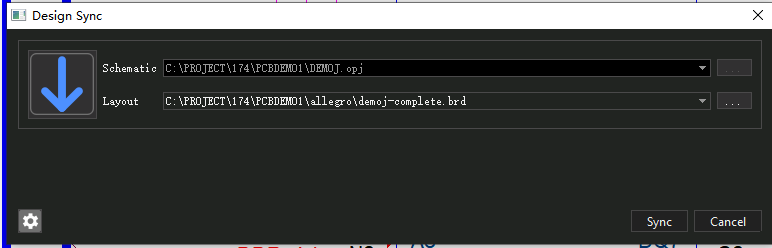

若之前原理图工程已经生成过PCB可以同步的功能,将刚才在约束管理器里面设置的规则约束同步到之前的PCB文件里面。选择 C:\PROJECT\174\PCBDEMO1\allegro\demoj-complete.brd的PCB文件,将我们刚才设置的规则同步到PCB中。

在这里我选择同步之后,可以看到,刚才设置的DDR-CLK的差分对网络规则已经同步到PCB文件里面。

在PCB里面打开CM约束管理的管理窗口,可以看到在原理图设置约束规则的相对规则DDR-DATA0TO31的相对规则已经带入。

在PCB里面打开CM约束管理的管理窗口,可以看到在原理图设置约束规则的总线长规则DDR_A0TOA10,也已经同步过来,说明设置有效。

在PCB里面打开CM约束管理的管理窗口,可以看到在原理图差分对设置DDR_CLK也同步过来,说明设置有效。

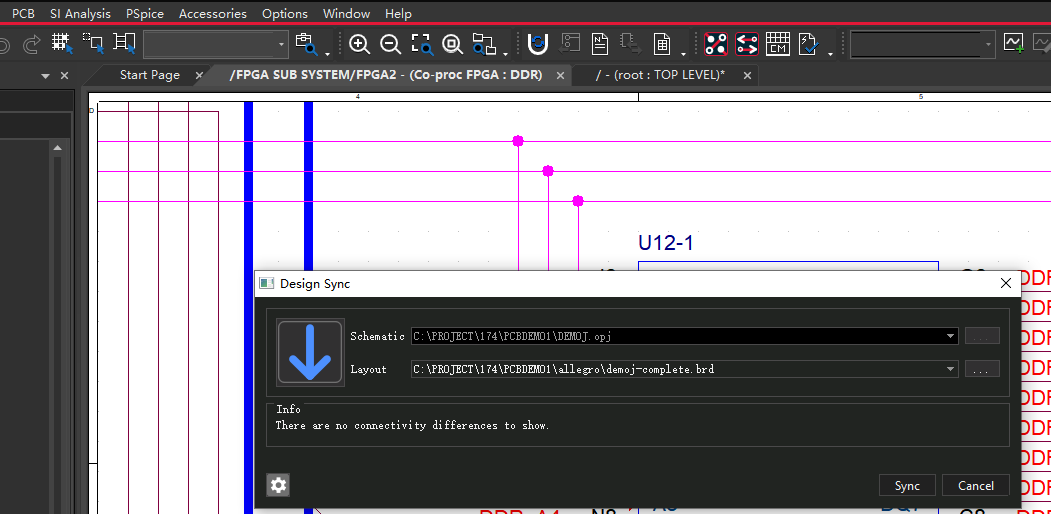

原理图的元件或者网络及规则约束等做出修改后,执行Design Sync用来同步,执行该命令弹出同步的对话框,软件会自动检查出当前的原理图文件和选中的PCB Layout之间存在的差异,并通过详细的信息列表的形式给出提示。点击sync按钮确认执行修改,PCB Layout文件按照原理图做出同步修改。

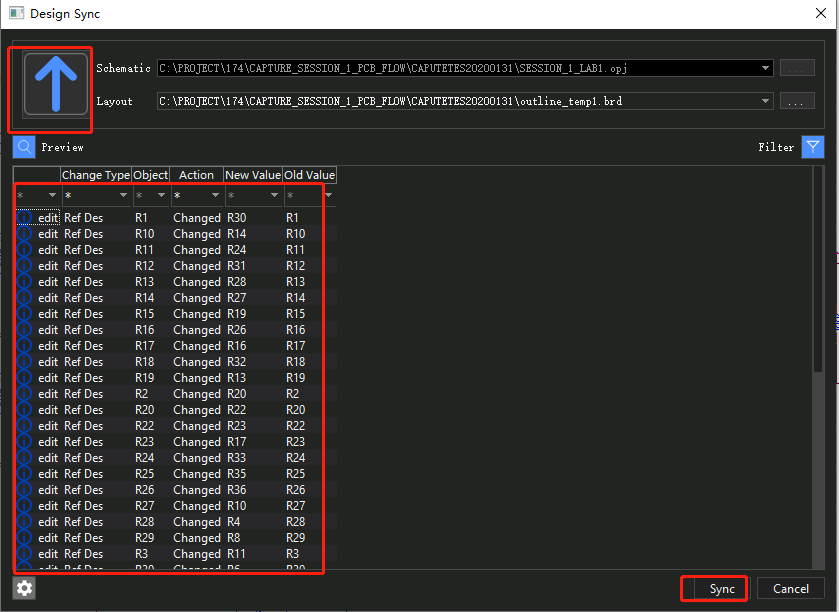

同理,打开Design Sync对话框。点击左侧同步按钮,切换成反向同步图标,在下面同步列表里面就可以看到,涉及到修改编号元件的详细列表信息,如下图所示,这些都是edit Ref Des的信息,点击Sync同步按钮以后,这些在PCB Layout里面的修改信息将会被同步到原理图文件里面。(约束的规则也可以通过这样的方式反向同步到原理图里面)。

通过上面的学习让我们看到了OrCAD Capture和Allegro约束管理规则设置和相互同步的方法,这个双向规则同步,解决了很多工程师的实际问题。该功能可以让PCB Layout和原理图之间的链接更加紧密,直接支持通过PCB文件进行双向的同步操作,避免了之前版本的繁琐操作,让同步的操作更加简洁,提高了设计效率。这个操作便于发现设计过程中存在的错误,并督导工程师及时纠正这些设计错误和存在的问题,为电路的原理图设计打好坚实基础。该方法可以大大的规范工程师的设计习惯,减少潜在原理设计问题,同步操作也对于提升设计效率以及设计的准确性是有很大帮助。

您是否在寻找企业级电子元器件资源库管理解决方案、电子协同设计管理解决方案、嵌入EDA软件的工艺以及设计规则检查分析方案、电路设计在线评审解决方案、智能“一键式”标准化归档解决方案、以及EDA(Cadence、Mentor、Altium Designer)设计软件与PDM/PLM/ERP系统在设计、工艺、制造数据的接口集成方案,欢迎了解并关注我们的合作伙伴“迪浩公司”。

迪浩公司基于自身深厚行业背景,开发了具有自主知识产权的CMS® 系列化软件,依托CMS®系列化的软件,为客户提供行业领域内EDA/CAD/CAE/PLM/ERP/PDM/MES/CAPP系统集成以及软件部署服务,确保用户电子设计资源数据高质量(ESHP)的无缝流转助力其实现数字化设计、智能制造的目标。

北京耀华创芯电子科技有限公司(英文:U-Creative Technology Limited,以下简称耀创科技),是一家专注于从事电子设计自动化(EDA)服务的高科技公司,是Cadence在国内合作时间最长的代理商。

耀创科技公司的管理和服务团队人员均拥有多年的EDA从业经验,公司自成立以来,为来自国内各区域和行业数百家的客户提供了优质的服务。

耀创科技通过十几年的发展,我们积累了丰富的EDA产品市场与服务经验,已经帮助国内多家客户成功地使用EDA产品,极大地提高了这些客户的电子设计水平和生产效率。在引进国外先进的EDA工具的同时,我们针对中国市场的特殊性,与Cadence公司合作,在国内最早提出了电子设计与数据管理平台的概念,开发出具有自主知识产权的电子电气设计集成数据管理平台CMS Suite,成功地在一些研究所及商业公司内进行实施,极大的加速了板级产品的标准化设计流程,覆盖从优选元件选控、协同设计输入、在线检查分析、标准化文档输出及PLM/PDM系统集成,在业界获得一致好评。与此同时,根据国内客户的实际情况,我们还提供除了软件使用培训之外的项目陪同设计服务,以帮助客户在完成实际课题的同时能够熟练掌握软件的使用,这一举措也取得了非常好的效果。

我们一直秉承“与客户共同成长”的服务理念,希望在国内EDA领域内能为更多客户提供支持与服务!

耀创深圳

www.u-c.com.cn

欢迎您的留言长按扫码可关注