IEDM: Novel Interconnect Techniques Beyond 3nm

编者按:作者展示了他从IMEC的Chris Wilson处了解到的3nm以后的新型互联技术,本文中不但简述了传统的铜互连技术,还探讨了一些新的“比铜更好”的金属。

During the short course on the Sunday before IEDM, Chris Wilson of imec presented Novel Interconnect Techniques for Advanced Devices Beyond 3nm.

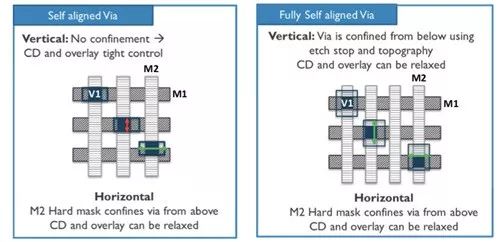

Going forward requires DTCO and scaling boosters, such as self-aligned block, fully self-aligned via, supervia (going up more than one level), and buried power rail (BPR). Chris went over the process implications of many of these, but I won't repeat everything here, not least because I'm not a process expert.

But here is one example, the fully self-aligned via. Fully self-aligned means that the via is confined by both the interconnect layer underneath and the one on top, as in the diagram on the right below, so that the via metal is precisely where it is required to join the two layers.

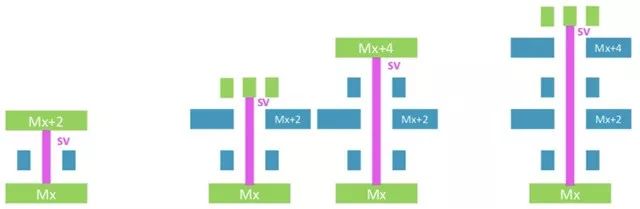

Supervias are another feature with implications for design. A Gen-1 supervia goes from Mx to Mx+2 (of course a normal via goes from Mx to Mx+1). This is very useful in an SRAM. Gen-2 from Mx to Mx+3 or Mx+4, useful for buried power rail. Then Gen-3 from Mx to Mx+5, allowing it to jump to low-resistance interconnect layers directly.

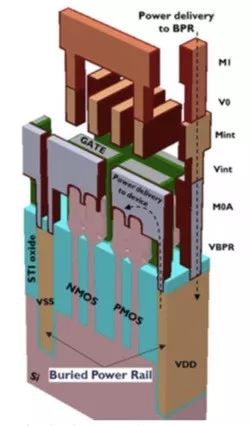

Buried power rail enables a transition from 6-track standard cells to 5T for 1-fin or nanosheet devices, and reduces the area by 17% without pitch scaling. Since the power is now at the bottom of the whole stack, supervias are useful to get the power up to higher levels of interconnect where they can deliver power to the cells on the chip, as you can see in the diagram.

By using ruthenium for the power rail, and a high aspect-ratio, BPR can satisfy the resistance target of 50Ω/um

Extending Copper

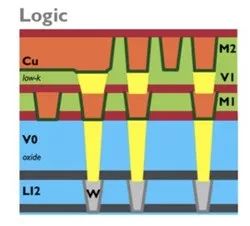

The big problem with copper is that it needs a barrier/liner since otherwise the copper migrates into the surrounding oxide. But it is hard to scale the liner as much as the interconnect itself, meaning that there is very little copper in the track (and there is a barrier at the bottom of every via that the current has to flow through). We need a sub-2nm barrier/liner for 16nm half-pitch and beyond. We have no material for 1nm although we can do 2nm with ruthenium.

Hybrid metallization (with cobalt, yellow in the image, which is barrierless) allows easier copper fill margin plus no barrier at the bottom of the vias.

Beyond Copper

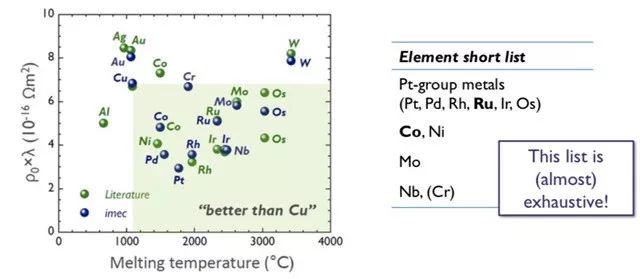

This chart shows all the metals that are "better than Cu" in that they have a higher melting temperature and a lower resistivity. We want a higher melting temperature since that is good for electromigration.

There are only a few good choices. The most attractive metals are Co and Ru. For barrierless Ru, with the same trench cross-section, it outperforms Cu at 16nm. For barrierless Co, it outperforms Cu from 12nm.

A big challenge with Co is CMP (chemical mechanical polishing) due to galvanic corrosion in narrow trenches. The process needs to be changed to use a different alkali rinse after the clean. CMP is also a challenge for the integration of Ru with a big spread depending on exactly what the critical dimension ends up being. There are also challenges with Ru adhesion strength to the oxide. But with 21nm metal pitch Ru interconnect, imec has built wires that can pass 10-year lifetime for both TDDB (time-dependent dielectric breakdown) and electromigration.

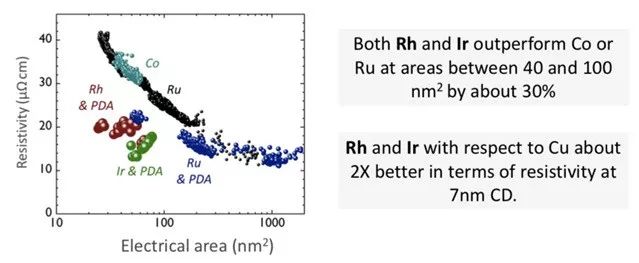

Another approach is to go away from dual damascene copper process and go to subtractive etch (how interconnect was all done in the pre-copper days). There is a resistivity benefit from doing this. This works with Ru, too, giving a resistivity benefit due to less grain boundary scattering. This can get down to 14nm critical dimension, and an anneal can modulate resistance.

Better than Ru and Co are rhodium (Rh) and iridium (Ir) for line resistivity. There are also more complex compounds, not just single elements, that show excellent figures of merit, and will be needed to address resistance increases.

Summary

Chris's summary was:

BEOL requires scaling boosters and DTCO to enhance the process and to enable device architectures.

Via pre-fill (with Co or Ru) offers a stepping stone to an alternative metal.

But alternative metals like Co or Ru will be needed for interconnect.

Ru integration is viable MP21 damascene passing all reliability metrics but faces scaling limits at MP16.

Subtractive etch to Ru lines offers 20-30% RC benefit for interconnects beyond MP16 technology.

There is a pipeline of materials to combat resistance increase.

看完有什么感想?

请留言参与讨论!