出行再不便,挡不住云上阅读的脚步

目前新冠肺炎疫情防控仍在关键时间,不出门、少出门就是为疫情做贡献。虽然疫情造成出行不便,但宅家的日子,不要忘记给自己“充电”哦,接下来就让我们一起复习一下之前干货满满的eKnowledge吧。

还记得eKnowledge资源中心是在哪里吗?不记得?没关系!点击《1分钟揭开Teradyne LINK平台的“神秘面纱”,eKnowledge资源中心就藏身于此》,快速get 功能强大的Teraradyne LINK平台操作指南。最全面、最实时的技术信息,可轻松获取的视频观看和文档下载,这里都能实现。

不知道有哪些eKnowledge?查看下面摘要,点击相应图片。

1 用于减少皮安级小电流测量中的负载电容的创新DIB版图解决方案

在测量皮安级低电流中一直有一些问题,尽管用于这些测量的ATE板卡很精确。除此之外,驱动芯片输出到板卡也是一个问题,因为线路容值相应地表现为芯片输出管脚上的负载电容。更高的线路容值将会降低测量的重复性和可再现性。传统的解决方案是将放大器电路放置在离待测芯片较近的位置来降低负载电容,但不能适应有低电流测试的DIB设计。这篇文章将解释RF设计中通过版图设计来减少线路容值的解决方案。

2 大数据分析在ATE(自动测试仪器)领域的应用

本文分析了在ATE(自动测试仪器)领域,可以应用大数据分析的几个方面。其应用范围主要包括,通过大数据分析来提升良率以及对设备的主动维护。大数据分析有助于数据的整理,并且可以轻松扩大数据规模,处理海量数据,以便在适当的时间根据提供的统计数据来控制和管理生产过程中的各种问题,最大限度的提高良率。本文还介绍了自适应测试的概念,它与大数据分析相结合,有助于理解测试之间的“连接”关系,从而缩短测试时间(TTR)。大数据分析还可以有效地用于主动性维护。即便是在其中的某一台机器出现了某单一故障的极端情况。

3 多工位高速HRAM读回

本文将描述兼容J750,flex和 Ultra-Flex的一个示例程序,演示在运行多工位测试时读取HRAM的三种方法。第一种是传统方法,其中设置了HRAM来获取数据,运行向量,并在工位循环中从每个工位读取数据。第二种方法在执行回读的方式上稍有进步,可以减少大约40%的测试时间。第三种方法最快,在one-bit模式下使用HRAM,减能少大约90%的测试时间。注:基于12工位(12-site)程序读芯片254的8位总线,测试时间优化。

4 低漏电流的测量:是否使用APU-12?

本文比较了在ETS-364平台上nA/pA范围的低漏电流测量的两种测试技术,以及两种测试方法的测量精度,重复性,测试时间和测试资源分配(多工位数):第一种使用APU-12测量低漏电流,分享了低漏电流的难点和最佳做法,第二种使用了额外的电路,即电流电压转换器测量低漏电流。本研究试图回答以下难题,APU-12设备本身是否足以对给定的漏电流进行测量?

5 浮动资源的优点

在本文中, 您将了解如何连接Eagle的浮动资源以使测试机的潜能最大化。将标准配置中的浮动资源通过特定的连接方式进行连接可以测试许多独特的测试项。不同的测试系统由于体系结构的不同, 在面对这些独特的测试时往往需要使用第三方的资源或额外的通道, 而这无疑会影响测试效率和提高测试成本。Eagle 测试机中浮动资源的这些优点将通过几个实际的测试案例来体现。

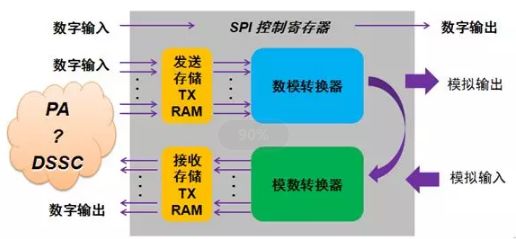

6 PA 和 DSSC 在混合信号测试中的使用

测试工程师常常在UltraFLEX系统中使用DSSC来提供数模转换器芯片的输入,以及抓取模数转换器芯片的输出。近几年,Protocol Aware(PA)作为UltraFLEX的新功能,可以支持很多种协议的读写,被广为使用。那我们有没有可能用PA替换掉DSSC呢?本文从一个角度回答了这个问题,并且详细分析了相关的数据,展示了结论。前半部分主要侧重于两种测试方法的使用描述,而且提供了源代码, PA文件和pattern给大家参考。后半部分分析了两种方式的优缺点,并着重分析了开发难度和测试时间。

7 适用于ETS364和ETS88系统的新颖方法&技巧汇总

本文将涉及以下话题:如何通过使用QTMU仪器测量并计算一组重复的低频和高频信号的周期;当需要测量的电流值略大于APU12仪器的量程时,如何提高电流测量的精度;如何通过提前退出测试向量以及消除mcurun()指令的系统开销加快阈值(threshold)搜索的速度;使用APU12仪器(或者任何具有任意波形发生器AWG的仪器)来产生持续的,占空比可变的方波;使用CBIT仪器来量化时间;使用QMTU的时间片(timeslices)进行频率阈值的快速搜索。

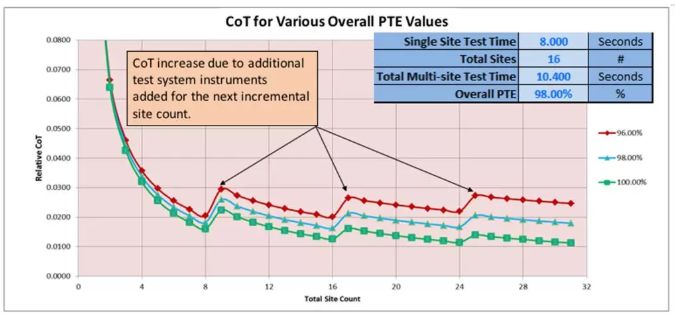

8 测试方案策略对测试成本(CoT)的影响

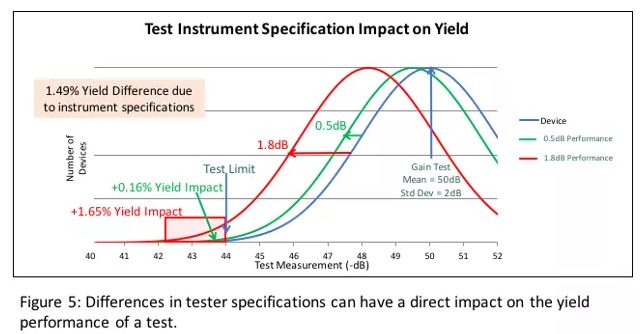

影响测试成本(CoT)的因素有很多: 工位(site)数,并行测试效率,产量,机台板卡规格指标(specifications),测试流程(test flow),设备成本,当然还包括测试时间以及其它,本文重点分析了测试方案中以下几个因素对测试成本(CoT)的影响:工位(Site)数;测试系统的架构: 单站(Single) vs. 多站(Multi-Sector);探针触压(Touchdown)效率和最大可能达到的良率;完整测试流程(test flow)分析和良率损失成本(cost of yield loss)。一般意义上来讲,增大工位数可以减少测试成本,但其实还要考虑并行测试效率(PTE)。如果同时考虑到更多因素的话,往往工位数有一个最优值,并不是越多越好。

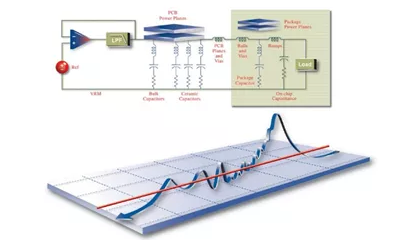

9 解密ATE接口板的电源完整性

在本文中,将展示整个设计中解决电源完整性的正确方法,解决ATE板子的最大问题(有仿真数据支持),并且展示可供选择的不同设计。干货亮点包括:目前ATE行业在电源完整性方面的发展状况、向您展示可用的工具以及结果分析,帮助您了解不同的电源完整性设计流程方案。

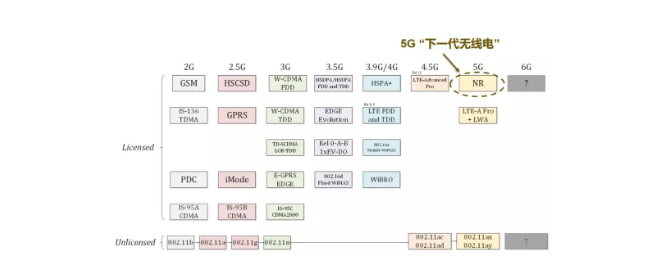

10 5G、无线毫米波、自动化测试(ATE)三者的巧妙化学反应

作为下一代无线通信技术,5G常常是爆点话题的宠儿,广泛被业界所探讨。当大家逐步清晰5G基本概念后,更将注意力转向5G技术的优势,5G背后的技术发展动因,技术目标,5G产品上市时间,机遇与挑战等等。本文将揭秘未来5G的标准制定和部署下,我们的日常工作、手机无线波段的未来,待测芯片以及自动化设备(ATE)将历经的改变。

11 快速精确的低压差线性稳压器测试

以低压差线性稳压器芯片为切入点,本文重点介绍Eagle测试系统的优势:如何使用SPU100和QMS资源测试LDO,以及描述了如何在SPUlow side分离开尔文连接以添加精确的偏置。Sense line上具有偏置,SPU给芯片提供电流,即使是最严格的负载调整率也可以使用SPUx100测量模式读取。更将演示一种新颖的LDO测试电路设计,包括如何基于该电路进行快速精确的LDO测试,测试结果以及相关的注意事项。

12 想要降低测试成本?这些策略可要了解一下 【上】

测试策略分析对减少片上系统(SOC)半导体器件的测试成本而言,正在变得越来越重要。每一个SOC芯片的测试流程都是独一无二的,需要深入分析来确定最佳的减少测试成本的策略。测试流程一般包括晶元测试和封装芯片测试。典型的测试流程可能包括两到五个或更多的testinsertion,这取决于芯片和终端客户的需求。在过去, 在每个测试流程中增加工位个数是一个降低测试成本的标准方法。

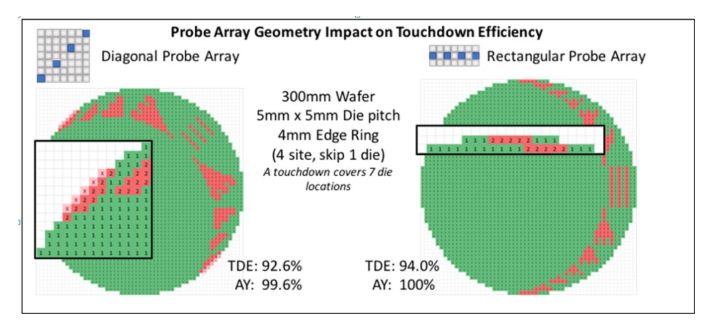

12 想要降低测试成本?这些策略可要了解一下 【中】

在晶圆测试中,除了探针卡成本过高会限制增加测试工位数数量外还有一个限制。接触效率(Touchdown efficiency ,简称TDE)也是影响晶圆测试成本的一个关键指标。TDE是所有触压次数中针卡上的探针阵列有效接触芯片的比例。

12 测试方案会影响测试成本?这些策略可要了解一下 【下】

在分析整个测试流程成本时,每一个test insertion的良率是要考虑的一个关键参数。失效率导致的成本损失(CoYL)包括每个test insertion的良率损失成本。各个test insertion的CoYL由芯片成本,每个前序test insertion的成本、当前test insertion的成本以及终测情况下封装和组装的成本决定。然后将总的CoYL平摊到良品芯片的测试成本中,以确定完整的测试流程成本。

看完全文的你,是不是收获满满?嫌干货太少?接下来还有系列eKnowledge回顾,满足好学的你,敬请期待。