来源:内容由半导体行业观察(icbank)编译,作者:Nadine Collaert ,比利时Leuven IMEC项目主任,谢谢。

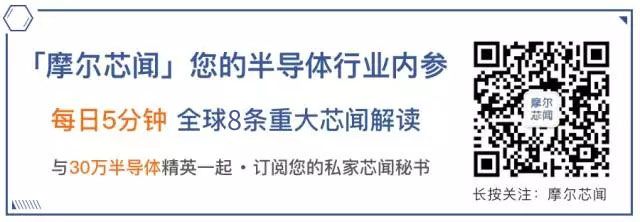

不可否认的是,CMOS的微缩已经成为推动过去几十年的巨大进步的“燃料”,以提高性能、效率和降低集成电路和系统的成本,从而实现新的应用。摩尔定律的终结已经被预言了很多次,而材料、设备概念和图案的创新已经为当前的10nm以下技术扫清了道路。然而,该行业已经到了这样一个阶段:过去50年的规模化所带来的功耗、性能、面积和成本(PPAC)方面的典型收益已经变得越来越难以实现,尤其是在展望未来3nm技术的时候。随着22nm FinFET的引入,我们已经清楚地认识到,单纯的尺寸缩放不足以满足半导体经济的需求。设计-技术协同优化(DTCO)的概念(如图1),其中可扩展到功能块的级别,已经获得了很大的吸引力,目前越来越多地成为工业中用于评估技术权衡和挑战下一代精细设计规则的标准方法。例如,在3nm处,通过缩放栅极间距和金属间距所减少的面积最多只有34%,而所需的比例为50%。因此,已经提出了有助于减少电池缩放的特殊构造,如埋入式电源轨道,通过将电力线嵌入隔离的前端线路(FEOL)或衬底,标准单元的轨道高度可以从6轨道(6T)缩放到5轨道(5T)。图1:从传统的维度标度到设计技术协同优化(DTCO)导向标度到系统技术协同优化(STCO)。

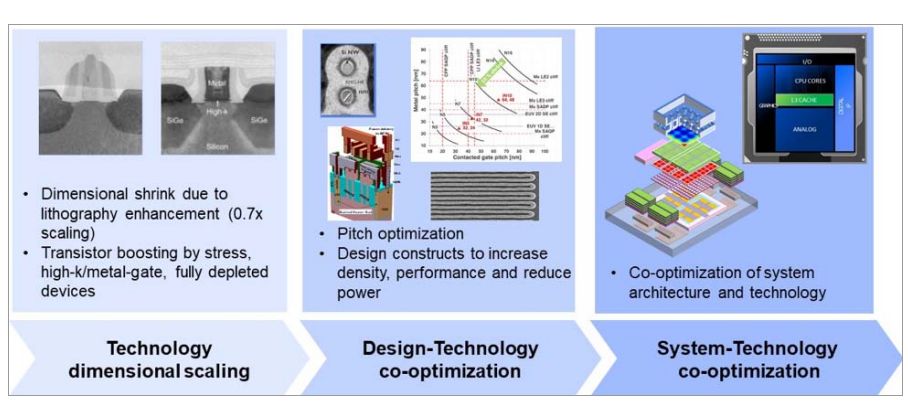

从器件架构的角度来看,FinFET(图2a)仍然是人们感兴趣的主要器件概念,但单元高度缩放正在迫使FIFIN减少。将每个器件的FIFIN数从两个FIFIN减少到一个FIFIN,从而显著地削弱了器件强度并增加了可变性。通常可以通过增加FIFIN高度来恢复器件强度。然而,这通常会增加工艺和集成的复杂性,从而使这些高纵横比薄膜的机械稳定性开始下降。图2:3nm器件结构的优化 (a)高纵横比FinFET的TEM图像,(b)堆叠纳米片器件的TEM图,(c)分叉片(Forksheet)的示意图,(d)互补场效应晶体管(CFET)的原理图。

类似纳米片 (图2b)这样的衍生结构(硅通道的薄板相互堆叠)引起了人们的极大兴趣,因为这些设备不仅提供了更好的静电学,而且还提高了相对于finfet的性能效率,从而实现更短的栅极长度、更高的每个足迹的驱动电流,以及对特定的接触电阻率等元素的更轻松的要求。但是,n- p分离的挑战仍然存在,这限制了cell footprint的进一步减少。在FinFETs中,栅极过度活跃的扩展基本上限制了SRAM单元高度的降低,因为栅极需要完全覆盖垂直的侧壁。因此,提出了一种新的设备架构:Forksheet(图2c)。在栅极图案形成之前,叉形栅极结构依赖于在NMOS和PMOS之间形成一层介电墙,从而形成自然屏障,使栅极和触点同时自对准。它消除了器件一侧的门极过扩展边缘,允许它将门极边缘与通道自对准,从而比标准的纳米片布局减少了20%的位单元。纳米片的一个更具革命性的进展是互补的FET或CFET(图1.3.2d),其中NMOS堆叠在PMOS之上。该装置的概念特别针对单元的互补性质,从而完全消除了n- p分离的瓶颈。该结构允许面积增益高达50%的标准电池以及SRAM,使它成为一个可能的总CMOS微缩解决方案。集成方案可以嫁接在一个典型的门式全流程flflow,也可以使用顺序3D处理,这是一种薄片级3D处理的薄片,它允许不同层之间以同样的分辨率和密度进行连接,而高级光刻技术可以为标准的后端金属化(BEOL)提供同样的分辨率和密度。CFET基本上是开发第三维度的第一步。单个CMOS技术通常实现系统(SoC)中的所有功能。如今,更多的趋势是定制化设计,为所需的功能挑选最好的技术,并将其与系统的其他部分很好地结合在一起,这些部分通常非常不同,而不是采用一种通用的技术。这种异构集成需要设置与DTCO类似的方法,但是要将抽象级别提升到(子)系统:STCO,在STCO中跨许多不同级别进行优化,从流程单元步骤和集成一直到应用程序级别(图1.3.1)。下面将列举几个例子。

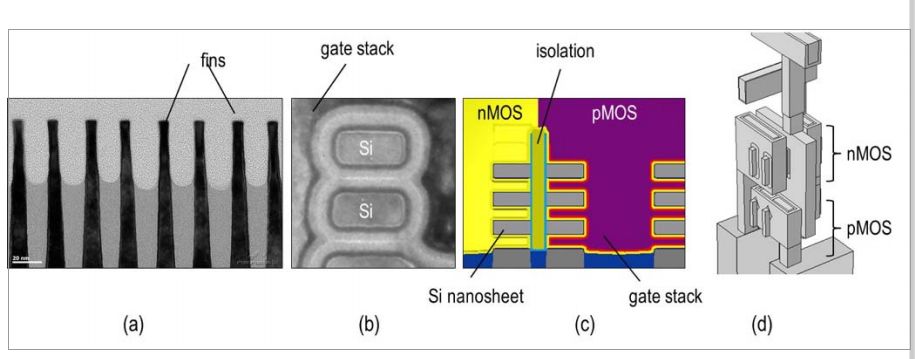

ML、5G、AR/VR等新兴应用将需要启用多种功能(内存计算、超低功耗、高速等)。对将这些不同技术融合在一起的混合微缩的需求越来越大。以前作为缩放路线图的一部分而考虑的器件概念,由于不是完整的CMOS解决方案而被放弃,现在在其他应用的背景下和异构集成的背景下被再次考虑。一个例子是用于机器学习的电阻式RAM(RRAM)。第二个例子与化合物半导体的使用有关,如GaN和III-V族化合物。在寻求能够在降低电源电压的情况下提供更高速度的逻辑晶体管的过程中,这些材料由于具有更高的迁移率和饱和速率,被认为是MOSFET中Si沟道的替代材料。在过去的十年中,他们在CMOS兼容的Si基板上的co集成、与栅极堆栈相关的可靠性和可扩展性方面的挑战一直是一般研发工作的重点。虽然越来越明显,这些设备的性能在ultra-scaled维度将无法与成熟的Si FinFET技术的进展已经协整的这些不同的材料如果平台带头再考虑他们作为其他应用程序的可行的选项(高压和射频应用程序),但这一次添加的优势能够制造CMOS-compatible生产线。在高压应用方面,与GaN-on-SiC相比,GaN-on-Si在过去几年中获得了大量的发展,它是一种成本效益更佳的选择,可以升级到比6英寸更大的基片,同时在比LDMOS更高的频率上提供更高的输出功率。GaN高压领域的发展趋势与热膨胀(CTE)匹配基板的系数有关,这些基板超越了Si,但仍然与CMOS工艺兼容。新的设备概念,如允许高击穿电压和高单位面积电流的半垂直设备,改进的可靠性和更容易的热管理,以及从独立组件转移到GaN- ic选项,在GaN层启用更多的功能(图3)。图3:采用深沟槽隔离的GaN-on- soi工艺的原理图,使不同的GaN集成在同一衬底上。

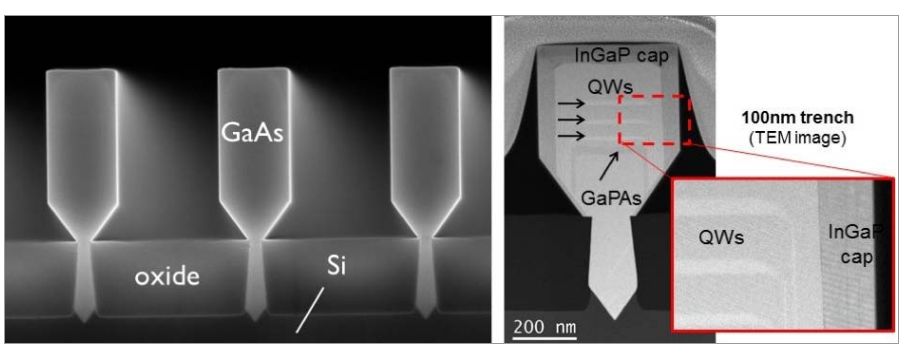

除此之外,GaN或III-V器件具有高片状电荷、高电子迁移率和宽带隙等独特的特性,因此通常也非常适合于高频应用。5 g部署和已经下一代无线通信更高数据速率在哪里设想(> 100 gb / s),有明显的担忧增加的复杂性相关射频Front-End-Module (RF-FEM),特别是在毫米波频率越高,波束形成无线电架构需要相控阵列天线的使用。当基于cmos的功率放大器的输出功率输出和效率PAE变得有限时,这一点尤为明显。更高的Pout和PAE意味着驱动天线所需的元件数量更少,而且可以启用更小形状的能量消耗系统,这对于手持设备和面积有限的小电池来说是必不可少的。但是,这些GaN和III-V器件的可积性较低,目前仅限于较小尺寸的基片和实验室式的处理,长期以来一直是采用这些技术的关键问题之一。将这些器件升级到200mm甚至300mm的Si平台将是使它们对包括光子学在内的各种应用更有吸引力的第一步,目前III-V对Si激光集成是一个非常活跃的研究领域(图4)。图4:(左图)在300mm硅衬底上生长的GaAs层的SEM图片,采用纵横比捕获和过度生长的组合,来降低III-V材料的缺陷,(右图)使用这种nano-ridge技术将III-V激光器用于光子学应用的整体集成。

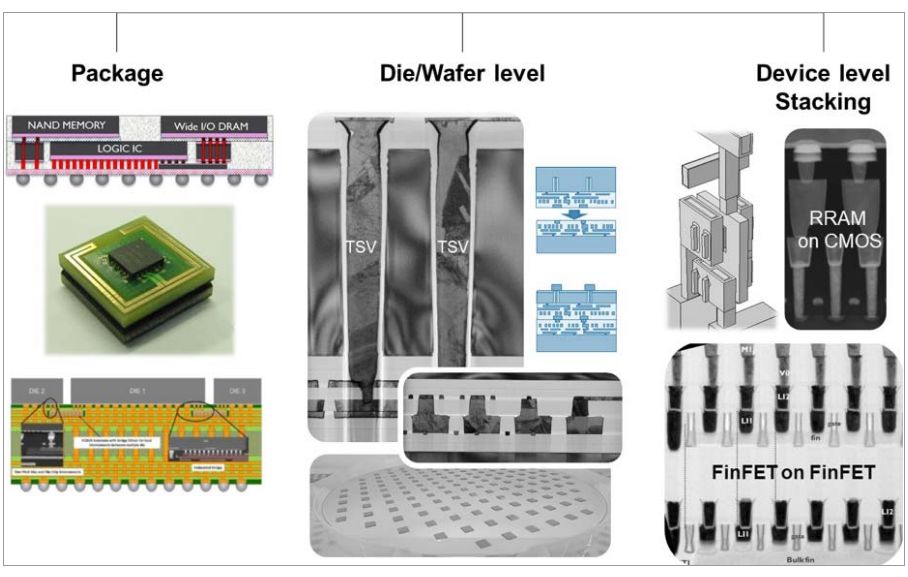

这些器件与Si CMOS的协同集成为将复合半导体器件的功率和速度与CMOS控制电路相结合提供了新的机会,从而使更大的功率响应系统(包络跟踪)成为可能。这种协整可以通过以下几种方式实现:使用集成电路(其中III-V设备与CMOS放在同一衬底中),或者使用3D集成(图5)。3D集成越来越受到关注,因为它允许人们以独立的方式处理和优化不同的技术,然后通过晶圆键合或基于TSV的互连将它们组合在一起。或者,顺序的3D处理,即以顺序的方式处理不同的设备层,有可能在不同层之间集成更小的、高密度的、更短的长度的互连。除此之外,减少的面积也是研究这项技术的主要驱动力之一。该方法已在批量Si上的平面Si无接点射频器件上得到证明。目前还没有观察到器件堆叠的影响,器件的射频性能符合fT预期的1/LG依赖性。这是第一次演示,展示了如何用不同的材料和架构构建专用的顶层器件,并将它们与提供逻辑功能的高级CMOS器件相结合。图5:不同的3D技术,从封装到裸片/晶圆到设备级叠加。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2227期内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

“芯”系疫情|AI|TWS|ARM|存储|CMOS|德州仪器|MEMS

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!