ISSCC 2020:高速串口解析

以下文章来源于haikun01 ,作者贾海昆

haikun01

清华大学微纳电子系,助理教授。研究方向:高速串口、功率放大器、信号源、毫米波电路与系统等全定制芯片设计。个人公众号,不定期分享一些芯片设计经验和感悟。

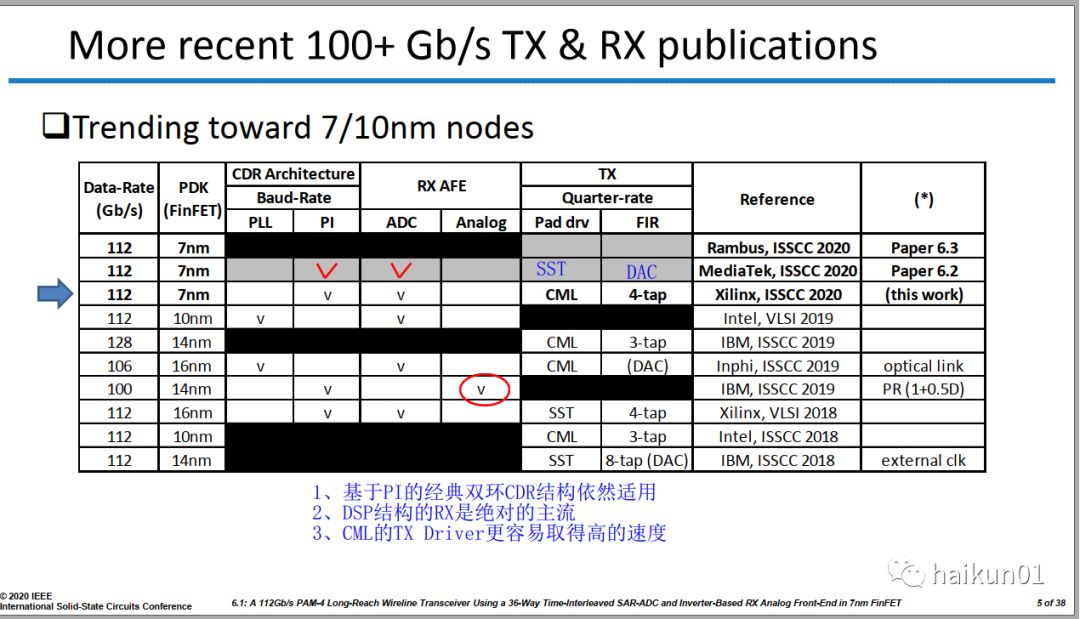

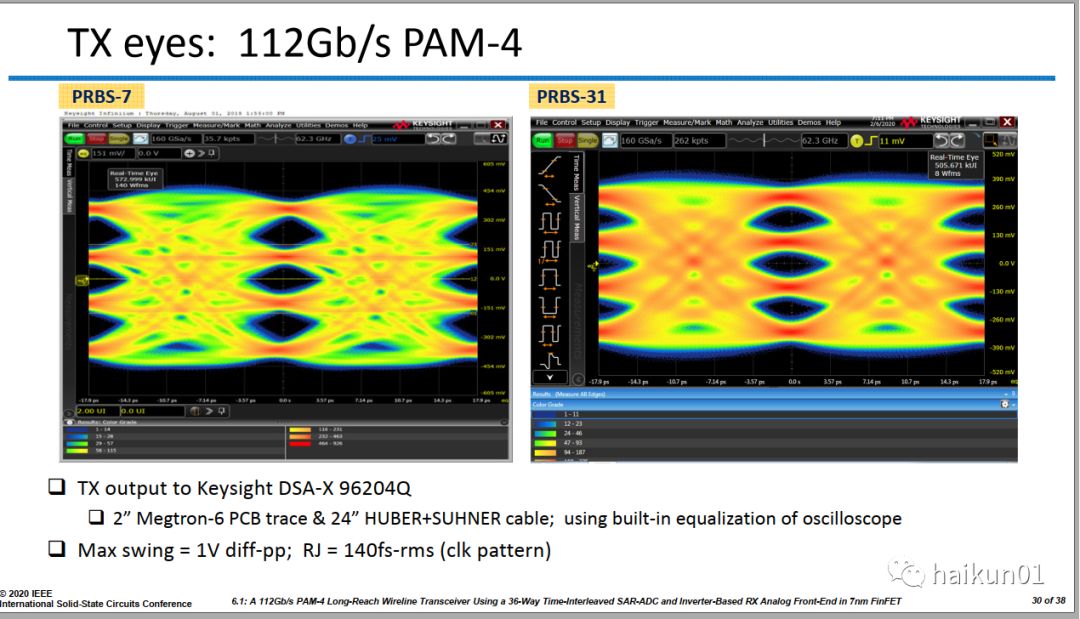

1、TX设计

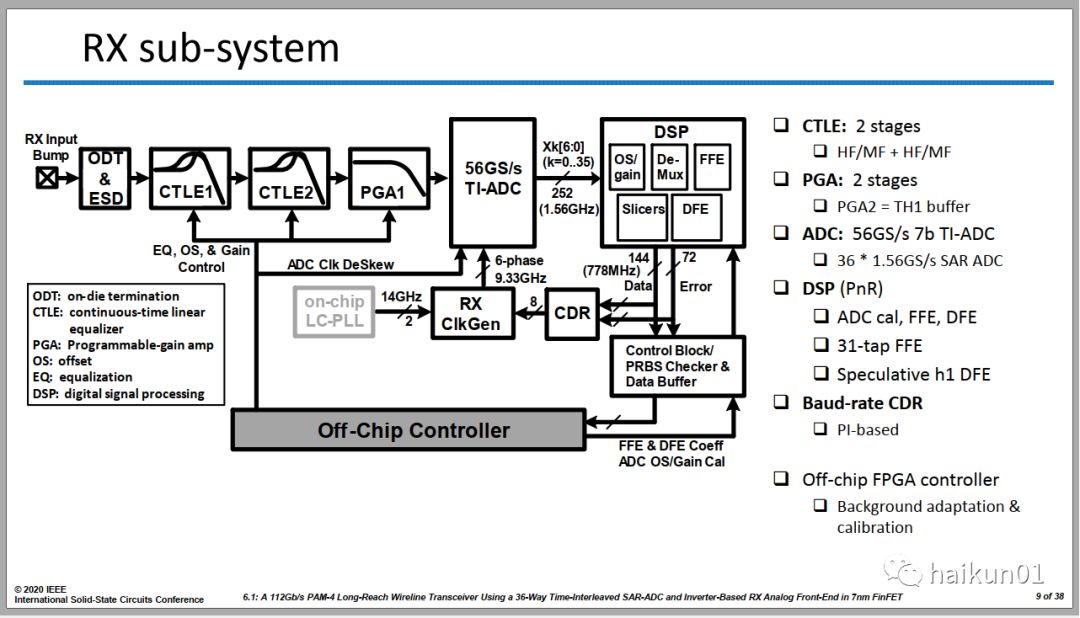

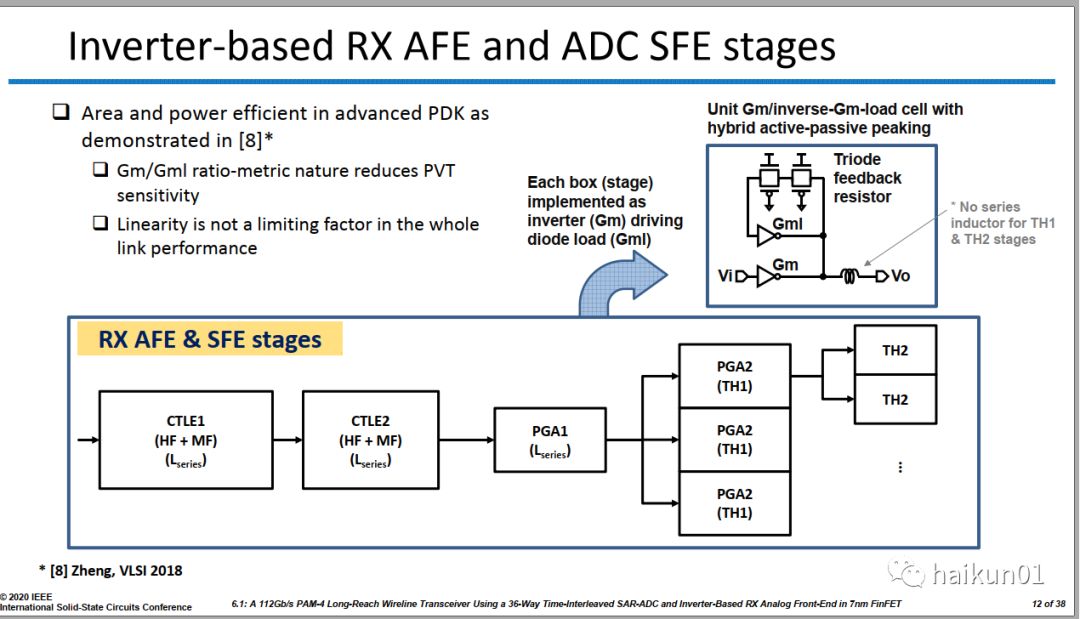

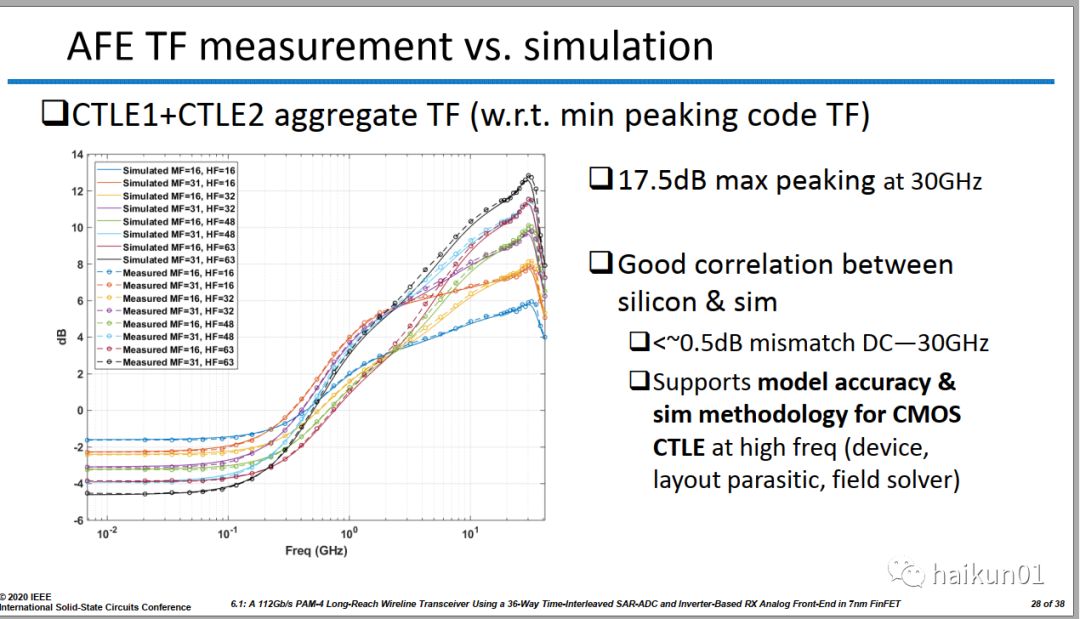

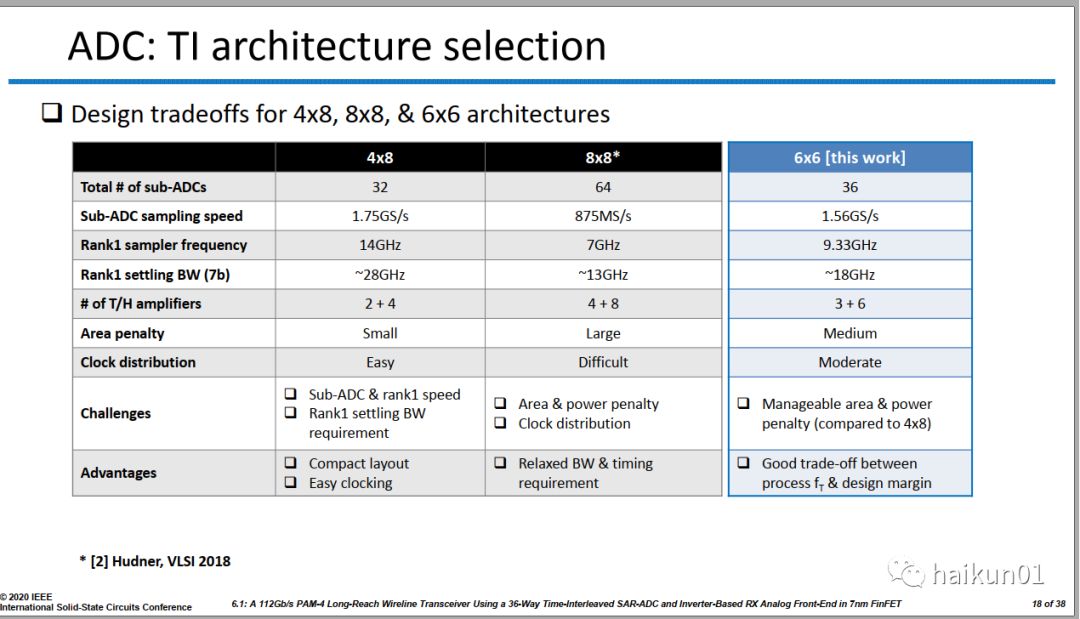

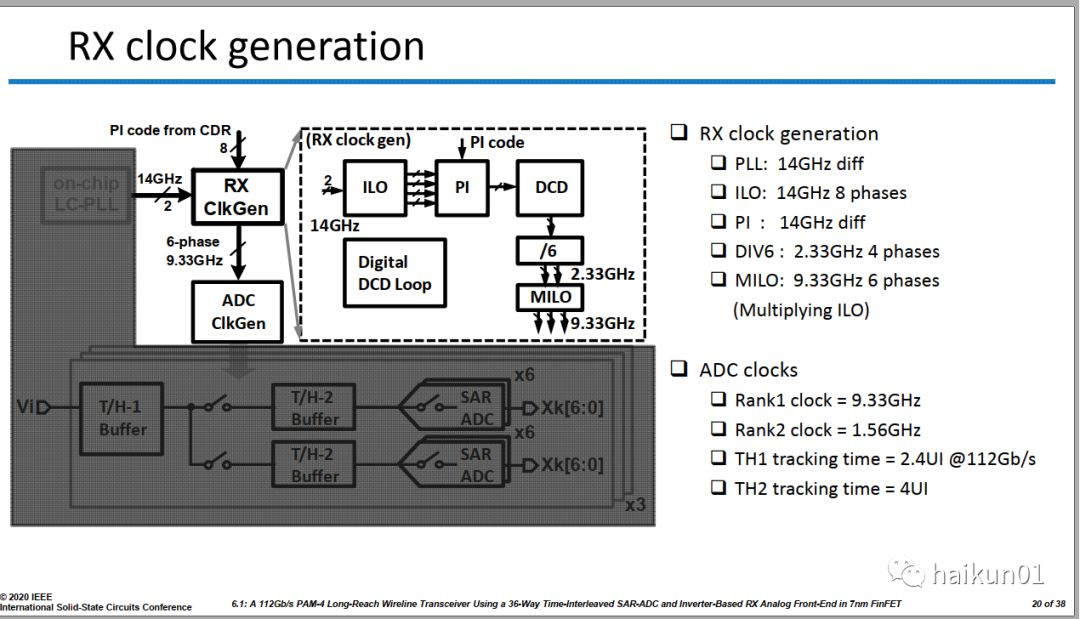

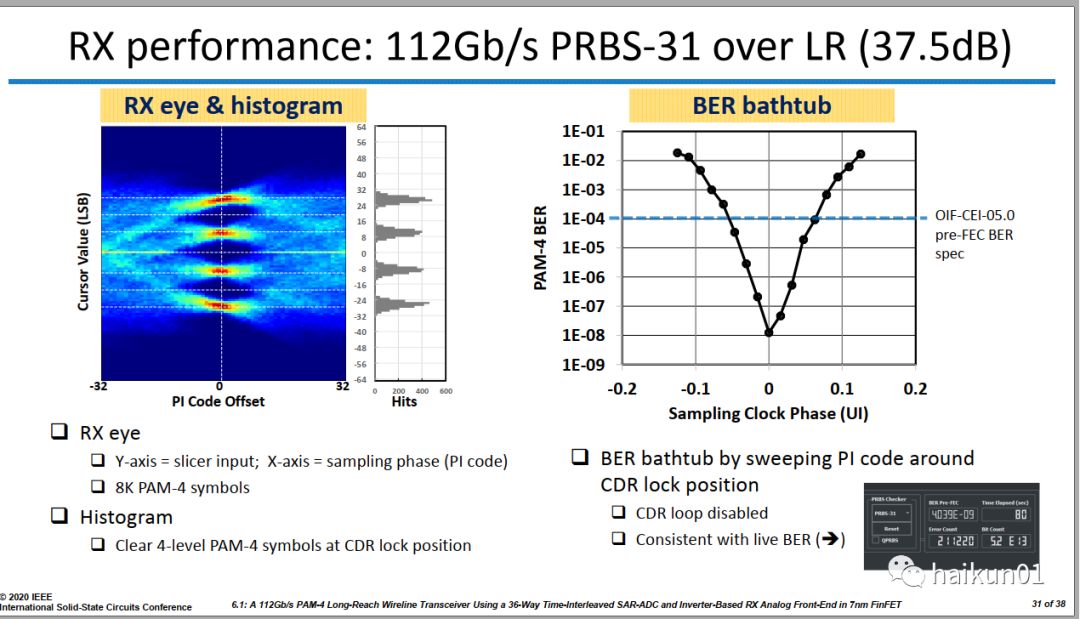

2、RX设计

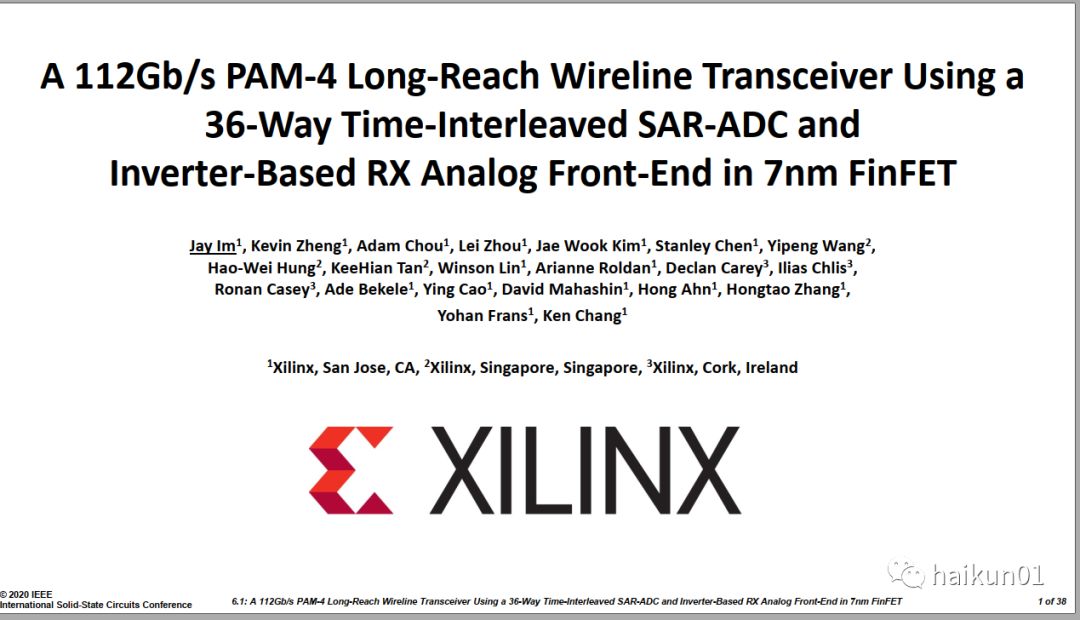

从技术上来说,56G的高速接口架构已经较为稳定,主流选择是:RX基于DSP,Time Interleaved ADC,一般先4到8的Track/Hold,每个Track/Hold带若干个ADC的Slice,TX采用Half Rate。均衡方面差不多都是CTLE、1-TAP DFE、若干TAP的FIR,以及TX-FFE。那56G接下来的技术挑战就是低功耗、以及更强大的Adaptive功能。对于112G的高速接口,我觉得现在大家追求的目标是先做出来再说,功耗什么的留给以后再优化,在架构选择上可以看到一些趋势,但还没有稳定下来。

3、总结

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2233期内容,欢迎关注。

推荐阅读

半导体行业观察

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

“芯”系疫情|功率半导体|TWS|华为|存储|Fab|MCU|小米

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!