2020新书试读IV《CMOS集成电路闩锁效应》第七章:触发闩锁效应的必要条件

内容简述:

CMOS工艺集成电路中电源、地、输入和输出管脚可能会遭受各种浪涌信号和ESD静电脉冲信号,它们构成多种触发方式,各种触发方式都可能产生衬底电流,只要这些衬底电流足够大,都有可能触发寄生NPN和PNPN结构,并导致闩锁效应。

请同学们随时关注EETOP创芯大讲堂,将为大家提供优惠购买渠道及免费阅读机会。相关咨询添加微信:ssywtt

之前我们已经试读了新书《CMOS集成电路闩锁效应》的 第一章(点击查看)、第三章(点击查看)、第四章(点击查看),今天接着读第七章。

本章侧重介绍闩锁效应的触发分类和触发方式。

第七章:触发闩锁效应的必要条件

7.1物理条件

7.1.1 回路增益βn*βp >1

7.1.2阱等效电阻Rn和Rp足够大

7.1.3形成低阻通路

7.2电路偏置条件(不发布)

7.2.1电源电压大于自持电压 (不发布)

7.2.2瞬态激励足够大(不发布)

7.2.3适合的偏置条件(不发布)

7.3小结 (不发布)

扫描二维码可以购买本书作者在创芯大讲堂《CMOS集成电路闩锁效应》视频教程。

添加微信ssywtt获取创芯大讲堂课程内部价格

4.2闩锁效应的触发方式[1]

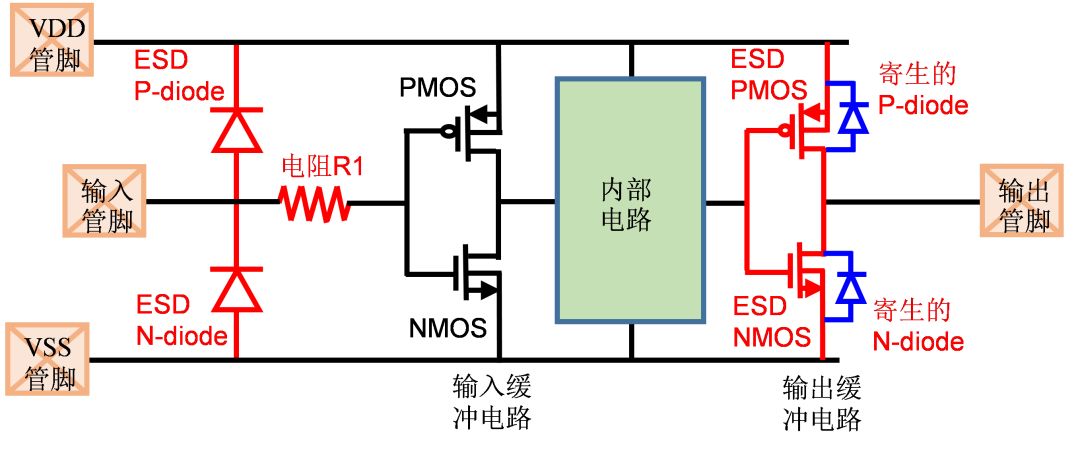

图4-5所示的是带有电源、地、输入和输出管脚的电路简图,这些管脚会遭受各种各样的瞬态激励或者ESD静电脉冲,导致相应的电路被导通或者击穿,从而产生瞬态电流,如果这些瞬态电流足够大,有可能触发CMOS工艺集成电路的寄生NPN或者寄生PNPN结构的闩锁效应。例如浪涌信号出现在输出或者输入管脚,就可能导通寄生PN结,产生瞬态电流。或者浪涌信号出现在电源管脚导致NW和PW之间的PN结雪崩击穿、NW到NMOS n+有源区的穿通、漏极雪崩击穿等,都会产生瞬态电流。

图4-5 带有电源、地、输入和输出管脚的电路简图

4.2.1输出或者输入管脚的浪涌信号引起PN结导通

输出管脚信号的上冲/下冲

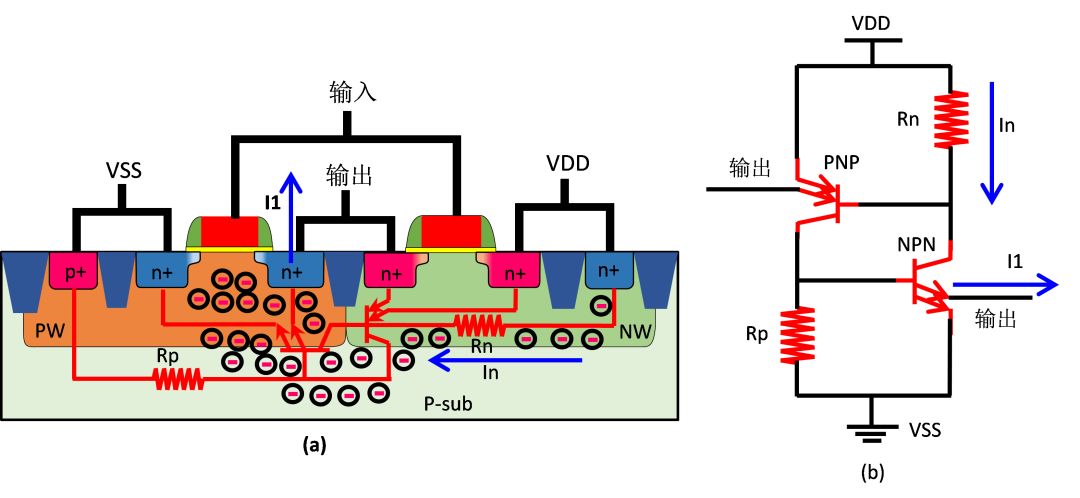

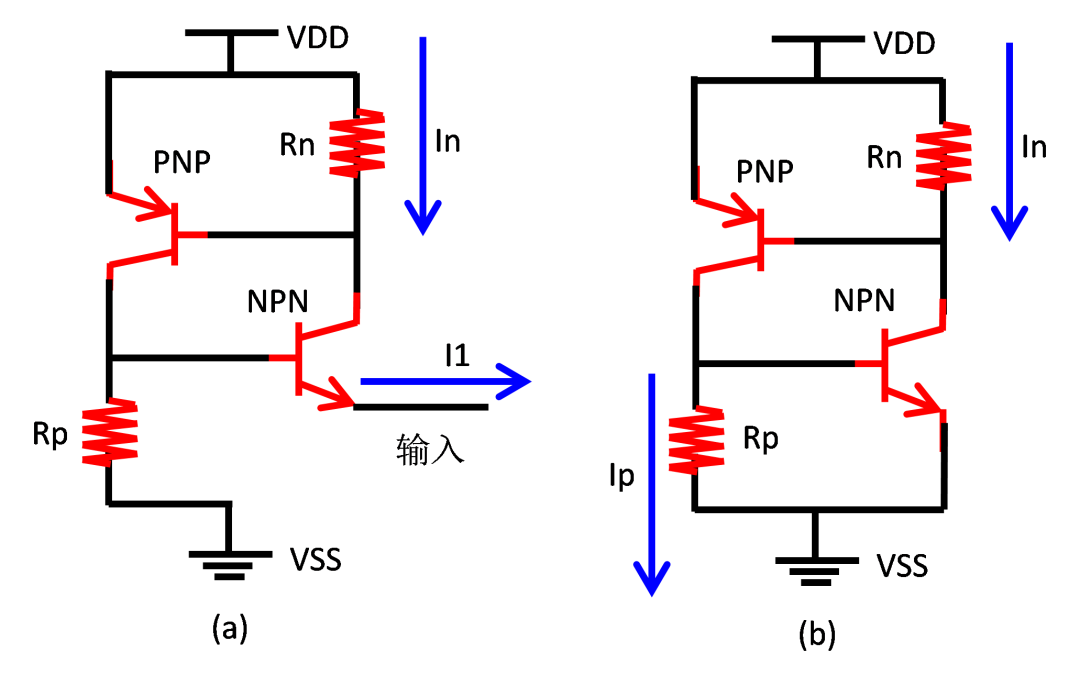

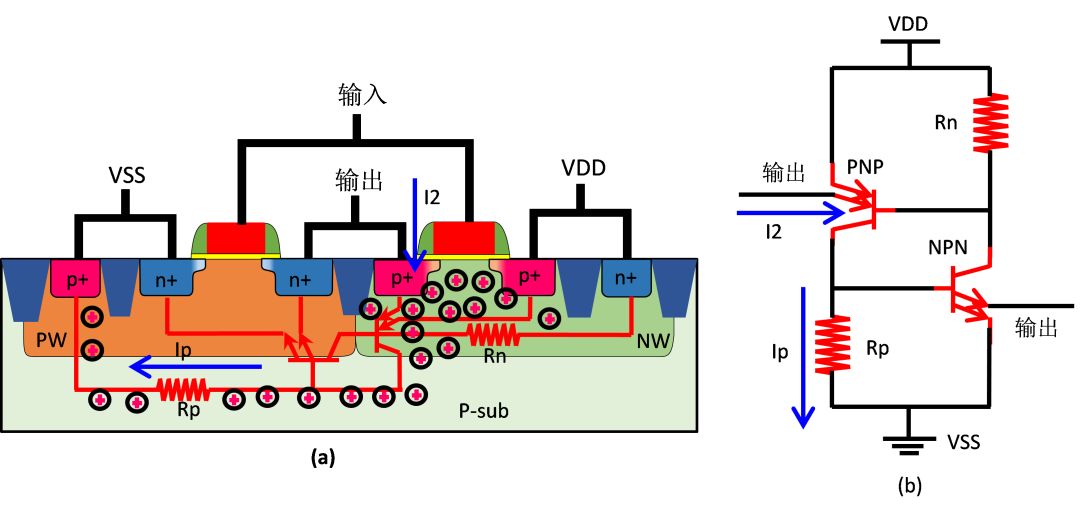

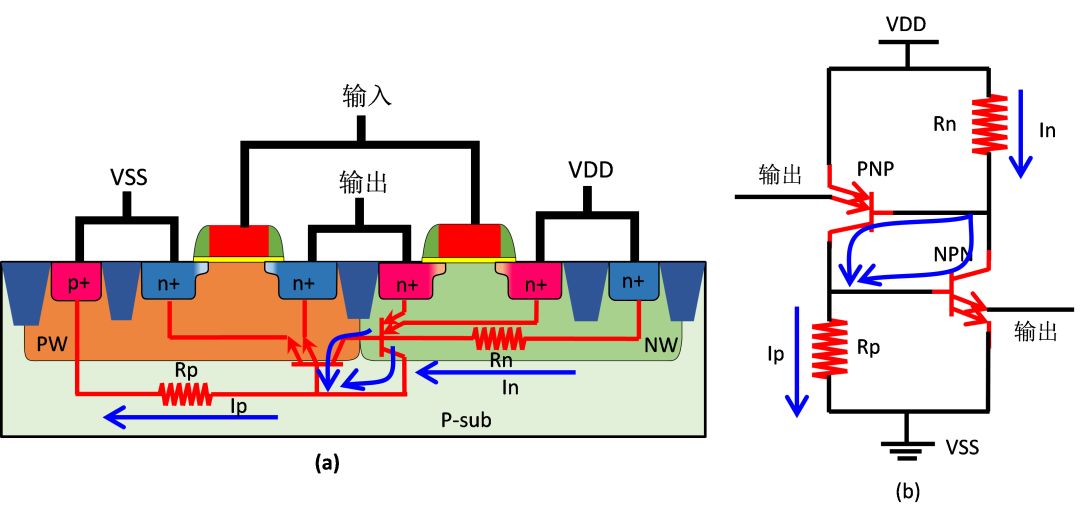

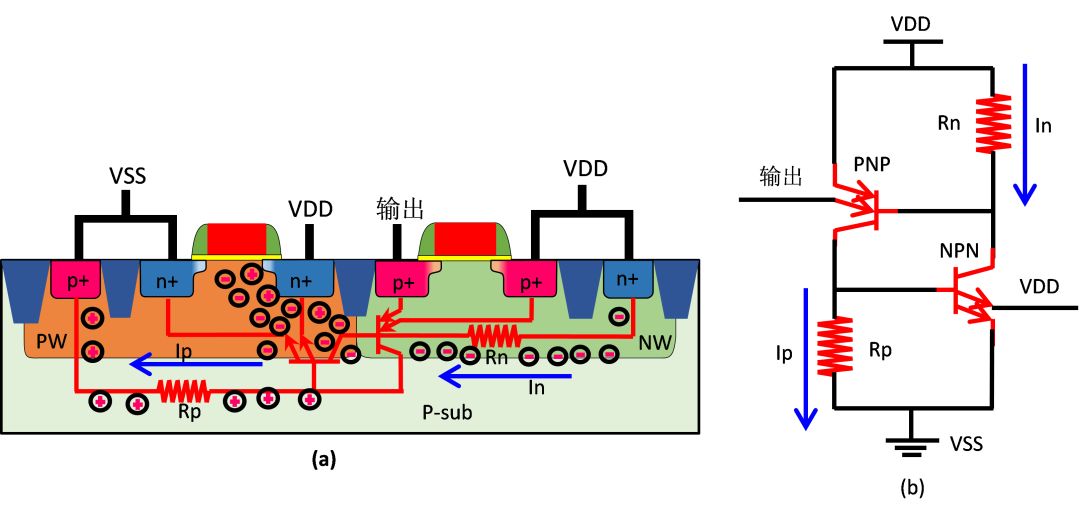

图4-5所示输出管脚是用ESD P/NMOS做ESD保护的,当输出管脚的瞬态电压突然下冲,并比连接到PW电压VSS低0.6V时,连接输出管脚的NMOS漏极n+有源区与PW之间的PN结正偏,也就是寄生NPN发射结正偏,寄生NPN导通,NMOS漏极n+有源区将电子注入到PW衬底中,电子在PW衬底中是少子,依据双极型晶体管原理,这些注入的电子有一部分会与空穴复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分电子会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被NW收集,形成In电流,该电流会在NW衬底的等效电阻Rn上形成欧姆压降In*Rn,如果In*Rn>0.6V,PMOS源极p+有源区与NW之间的PN结正偏,也就是寄生PNP的发射结正偏,寄生PNP导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-6所示的是输出管脚NMOS漏极n+有源区将电子注入到PW衬底。

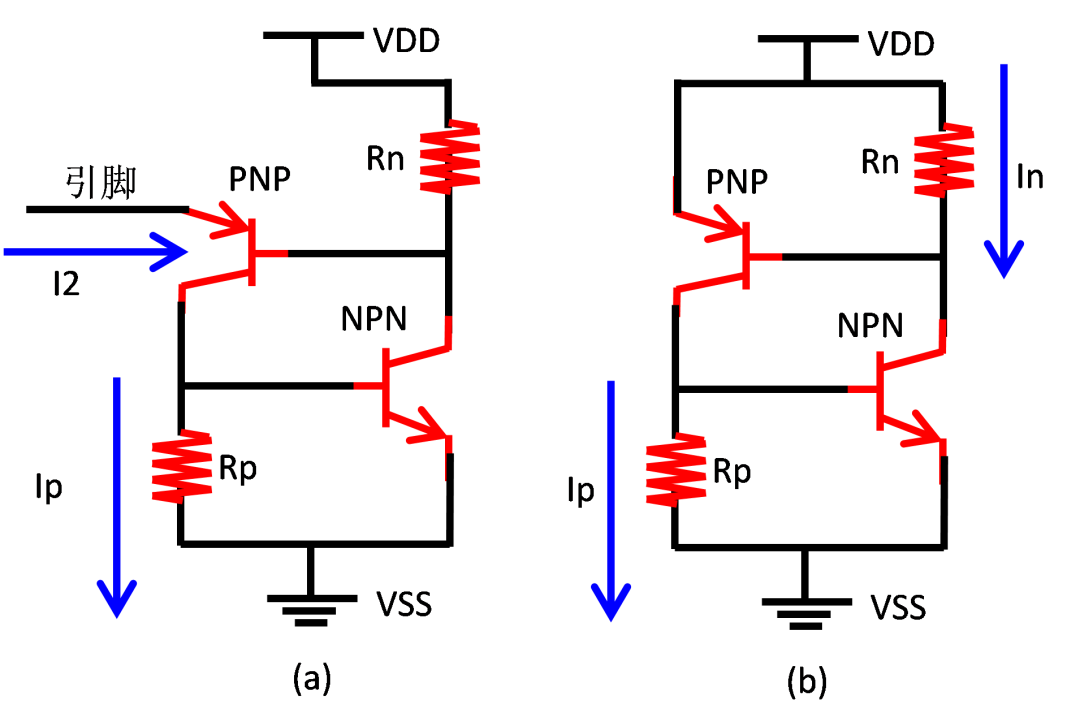

图4-7所示的是输出管脚信号的下冲引起“输出”闩锁和“主”闩锁。“输出”闩锁是在瞬态激励出现时被触发,触发引起的低阻通路可能产生瞬间大电流,并烧毁芯片,而瞬态激励消失后,“输出”闩锁也消失。“主”闩锁是在瞬态激励出现时被触发,触发引起的低阻通路也会产生瞬间大电流,并烧毁芯片,如果瞬态激励消失后,“主”闩锁也消失,那么“主”闩锁不具有自持能力,如果瞬态激励消失后,“主”闩锁依然存在,那么“主”闩锁具有自持能力。

图4-6输出管脚NMOS漏极n+有源区将电子注入到PW衬底

图4-7输出管脚信号的下冲引起“输出”闩锁和“主”闩锁

与输出管脚的瞬态电压突然下冲类似,当输出管脚的瞬态电压突然上升,并比NW电压高0.6V时,连接输出管脚的PMOS漏极p+有源区与NW之间的PN结正偏,也就是寄生PNP发射结正偏,寄生PNP导通,PMOS漏极p+有源区将空穴注入到NW衬底中,空穴在NW衬底中是少子,依据双极型晶体管原理,这些注入的空穴有一部分会与电子复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分空穴会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被PW收集,形成Ip电流,该电流会在PW衬底的等效电阻Rp上形成欧姆压降Ip*Rp,如果Ip*Rp>0.6V,连接输出管脚的NMOS源极n+有源区与PW之间的PN结正偏,也就是寄生NPN的发射结正偏,寄生NPN导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-8所示的是输出管脚PMOS漏极p+有源区将空穴注入到NW衬底。

输出管脚信号的上冲也会引起“输出”闩锁和“主”闩锁,图4-9所示的是输出管脚信号的下冲引起的“输出”闩锁和“主”闩锁。

图4-8输出管脚PMOS漏极p+有源区将空穴注入到NW衬底

图4-9输出管脚信号的上冲引起“输出”闩锁和“主”闩锁

输入管脚信号的上冲/下冲

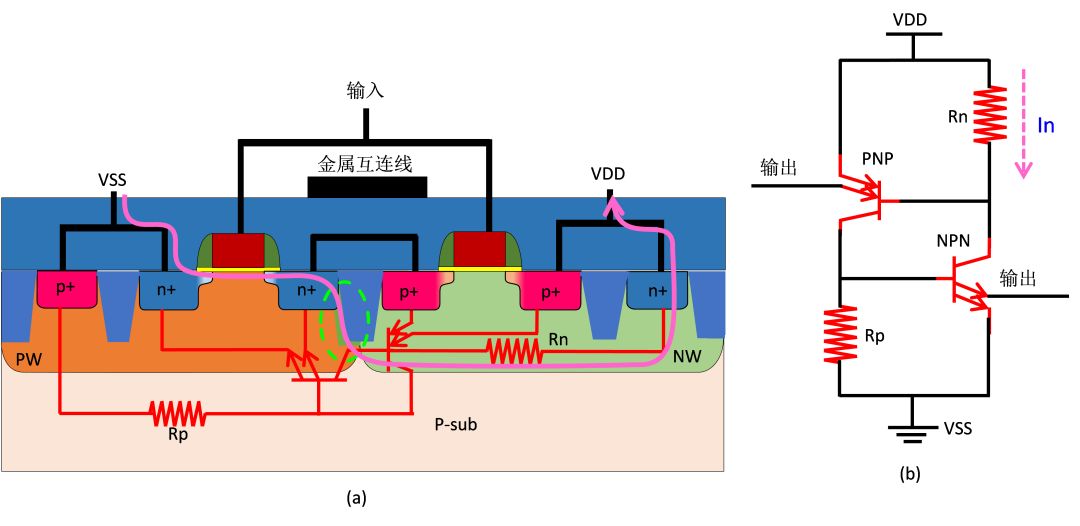

图4-5所示输入管脚是用ESD P/N-diode做ESD保护的,当输入管脚的瞬态电压突然下冲,并比连接到PW电压VSS低0.6V时,连接输出管脚的ESD N-diode导通,由ESD N-diode与NW形成的寄生NPN导通,N-diode将电子注入到PW衬底中,电子在PW衬底中是少子,依据双极型晶体管原理,这些注入的电子有一部分会与空穴复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分电子会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被NW收集,形成In电流,该电流会在NW衬底的等效电阻Rn上形成欧姆压降In*Rn,如果In*Rn>0.6V,连接输入管脚的PMOS源极p+有源区与NW之间的PN结正偏,也就是寄生PNP的发射结正偏,寄生PNP导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-10所示的是输入管脚N-diode将电子注入到PW衬底。

图4-10 输入管脚N-diode将电子注入到衬底

与输入管脚的瞬态电压突然下冲类似,当输入管脚的瞬态电压突然上升,并比NW电压高0.6V时,连接输出管脚的P-diode导通,由ESD P-diode与PW形成的寄生PNP导通,P-diode将空穴注入到NW衬底中,空穴在NW衬底中是少子,依据双极型晶体管原理,这些注入的空穴有一部分会与电子复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分空穴会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被PW收集,形成Ip电流,该电流会在PW衬底的等效电阻Rp上形成欧姆压降Ip*Rp,如果Ip*Rp>0.6V,连接输入管脚的NMOS源极n+有源区与PW之间的PN结正偏,也就是寄生NPN的发射结正偏,寄生NPN导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-11所示的是输入管脚P-diode将空穴注入到NW衬底。

图4-11 输入管脚P-diode将空穴注入到NW衬底

4.2.2电源管脚的浪涌信号引起击穿或者穿通

NW和PW之间的PN结雪崩击穿

对于CMOS工艺集成电路,正常情况下电源电压全部都加载在NW和PW之间反偏的PN结上,如果电源管脚出现瞬间很大的浪涌信号,有可能引起该PN结雪崩击穿,产生的电流同时流过NW和PW的两个等效旁路电阻,形成正反馈,如果正反馈电压Ip*Rp >0.6V和In*Rn >0.6V,那么寄生NPN和PNP会同时导通,并形成闩锁效应。图4-12所示的是NW和PW之间的PN结雪崩击穿。

图4-12 NW和PW之间的PN结雪崩击穿

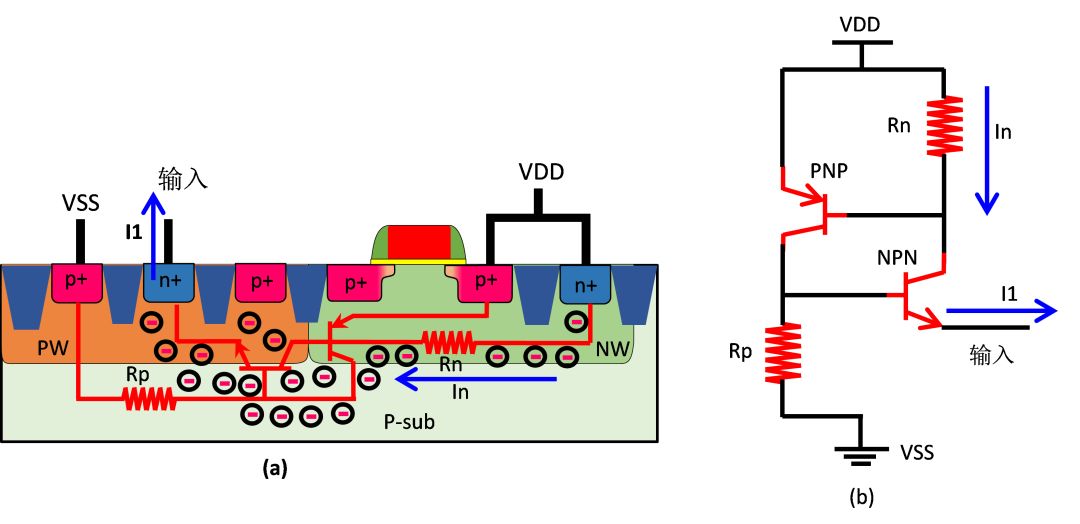

从NW到PW的n+有源区的穿通

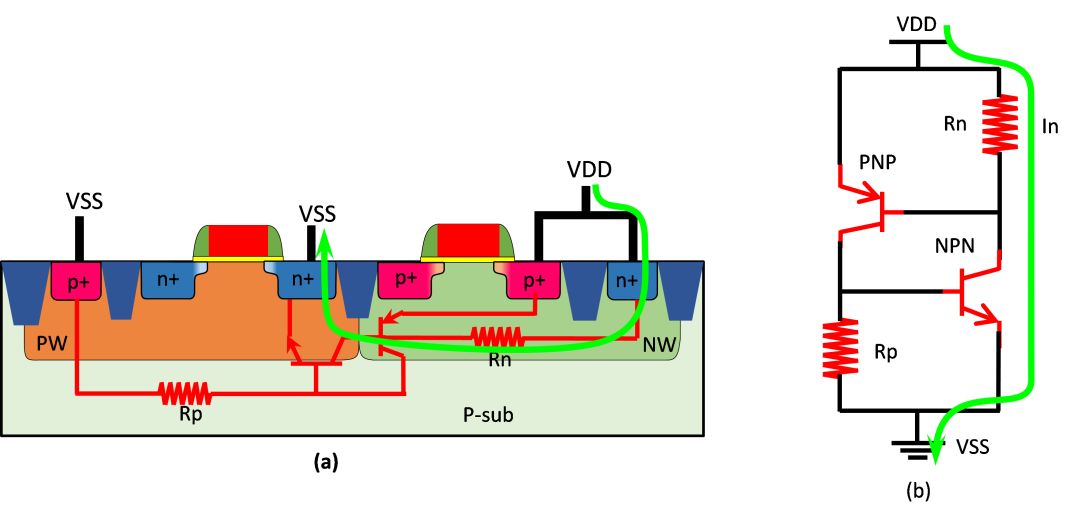

如果NW距离PW的n+有源区距离很近,电源管脚出现瞬间浪涌信号,除了会使NW和PW之间的PN结发生雪崩击穿,还会使该PN结的耗尽区与PW的n+有源区穿通,从而产生的电流In流过NW旁路电阻Rn,并产生欧姆压降In*Rn,如果该反馈电压In*Rn>0.6V,那么PMOS源极P+有源区与NW之间的PN结正偏,由PMOS源极P+有源区与PW形成的寄生PNP导通,PMOS源极P+有源区将空穴注入到NW衬底中,空穴在NW衬底中是少子,依据双极型晶体管原理,这些注入的空穴有一部分会与电子复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分空穴会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被PW收集,形成Ip电流,该电流会在PW衬底的等效电阻Rp上形成欧姆压降Ip*Rp,如果Ip*Rp>0.6V,连接输入管脚的PMOS漏极p+有源区与NW之间的PN结正偏,也就是寄生PNP的发射结正偏,寄生PNP导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-13所示的是NW到PW的n+有源区的穿通。

图4-13 NW到PW的n+有源区的穿通

从P-sub衬底到NW的p+有源区的穿通

如果NW的结深很浅,P-sub衬底到NW的p+有源区距离很近,电源管脚出现瞬间浪涌信号也会使NW与P-sub之间PN结的耗尽区与NW的p+有源区穿通,从而产生的电流Ip流过PW旁路电阻Rp,并产生欧姆压降Ip*Rp,如果该反馈电压Ip*Rp>0.6V,PMOS源极p+有源区与NW之间的PN结正偏,也就是寄生PNP发射结正偏,寄生PNP导通,PMOS源极p+有源区将空穴注入到NW衬底中,空穴在NW衬底中是少子,依据双极型晶体管原理,这些注入的空穴有一部分会与电子复合,有一部分会扩散到PW与NW之间反偏PN结边界附近,这部分空穴会被加载在PW与NW之间的强电场加速进入集电区,最后被集电区收集,也就是被PW收集,形成Ip电流,该电流会在PW衬底的等效电阻Rp上形成欧姆压降Ip*Rp,如果Ip*Rp>0.6V,连接输出管脚的PMOS漏极p+有源区与NW之间的PN结正偏,也就是寄生PNP的发射结正偏,寄生PNP导通,此时PNP和NPN同时导通,PNPN结构形成低阻通路,并发生闩锁效应。图4-14所示的是输出管脚PMOS漏极p+有源区将空穴注入到NW衬底。

图4-14 P-sub到内部P+有源区的穿通

NMOS漏极雪崩击穿

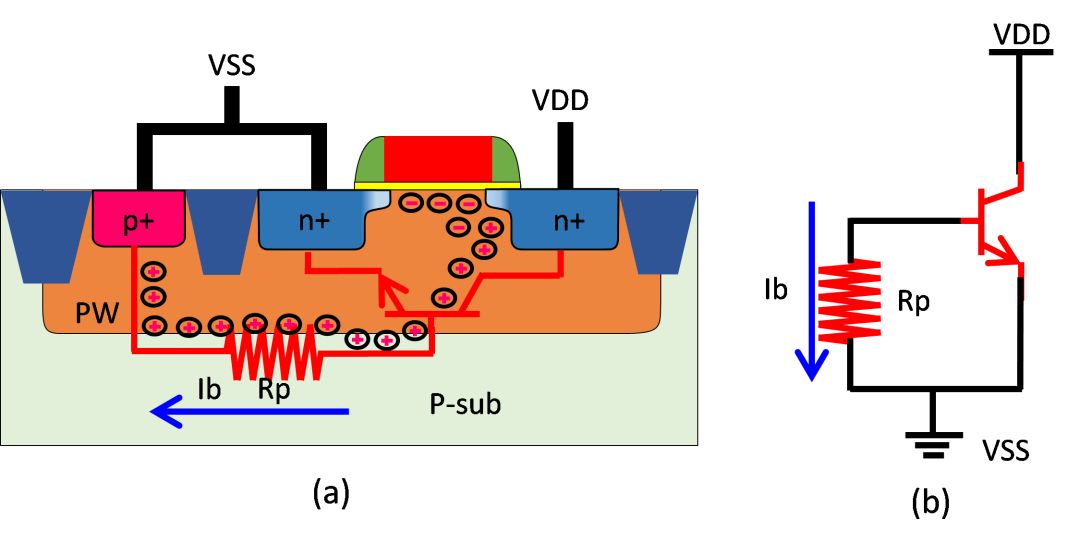

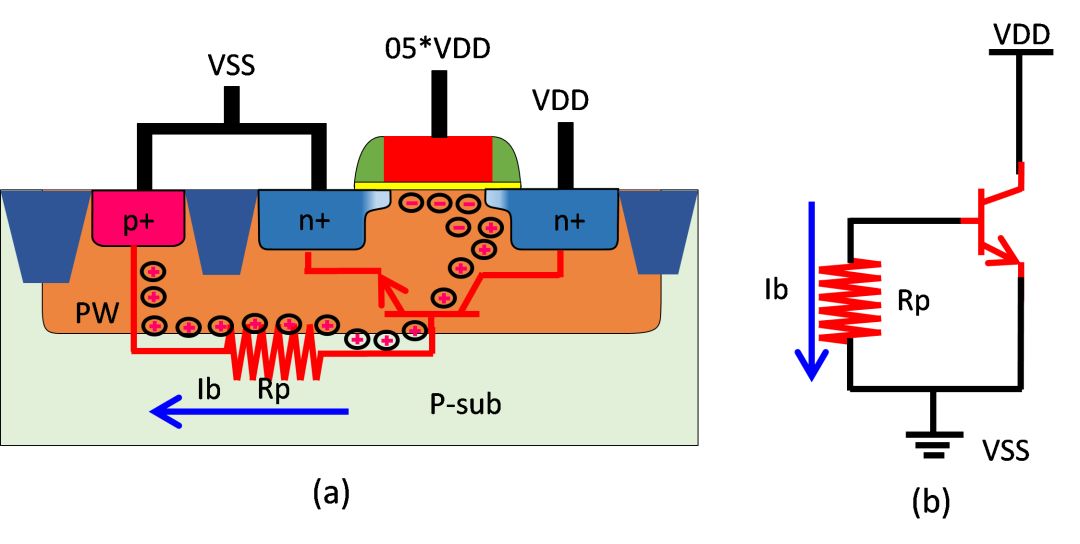

通常把ESD NMOS作为电源ESD钳位保护电路,在该电路中,NMOS的漏极接电源VDD,NMOS的衬底PW和源极接地VSS。如果VDD管脚的瞬态ESD脉冲电压大于NMOS漏极的雪崩击穿电压时,NMOS漏极雪崩击穿会在PW衬底内产生电子空穴对,电子被漏极收集,空穴在PW衬底是多数载流子,会被PW衬底收集形成衬底电流Ib,并在PW衬底等效电阻上形成压降Vb=Ib*Rp。如果反馈电压Vb>0.6V,该反馈电压导致PW衬底与NMOS源极n+有源区之间的PN结正偏,并使NMOS自身寄生NPN导通,如果Rp足够大,在瞬态ESD脉冲电压消失后,寄生NPN依然导通,它也会形成闩锁效应。图4-15所示的是NMOS雪崩击穿。

图4-15 NMOS雪崩击穿

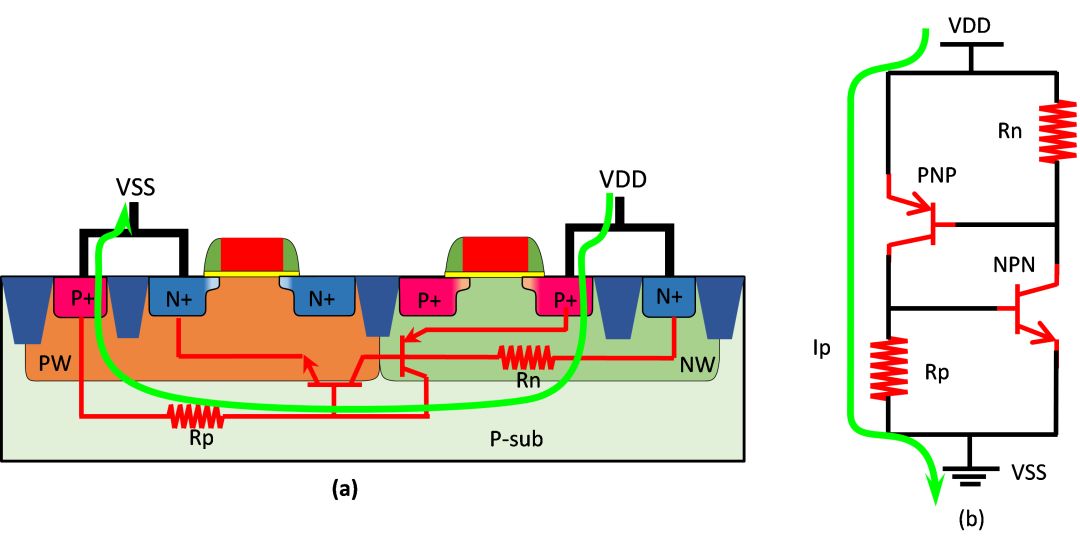

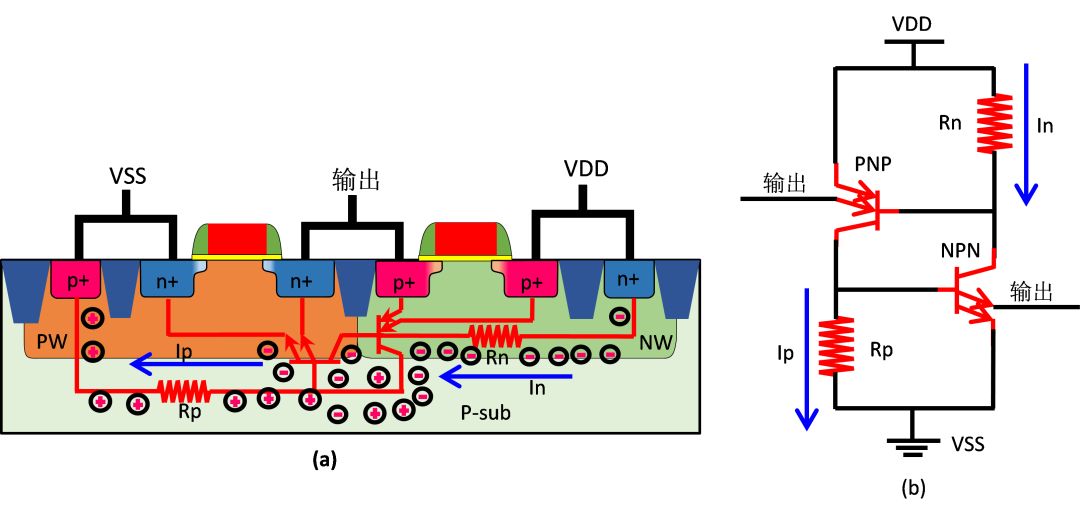

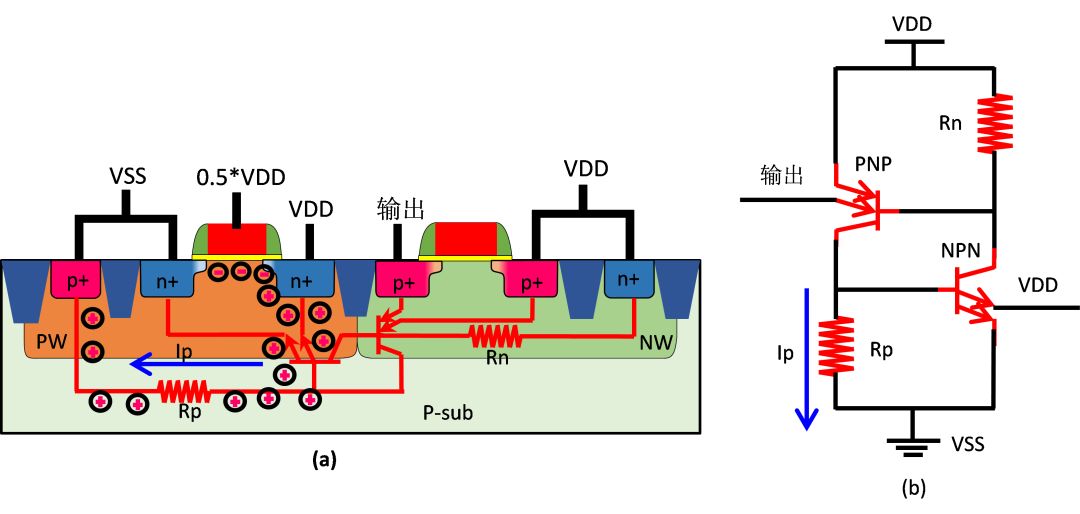

如果NMOS附近存在PMOS,NMOS漏极的雪崩击穿也会引起NMOS与PMOS之间的PNPN结构发生闩锁效应。NMOS漏极雪崩击穿会在PW衬底内产生电子空穴对,空穴在PW衬底是多数载流子,会被PW衬底收集形成衬底电流Ip,并在PW衬底等效电阻上形成压降Ip*Rp。如果反馈电压Ip*Rp>0.6V,NMOS源极n+有源区与PW衬底之间的PN结正偏,并使NMOS与NW的寄生NPN导通。而电子会被NW收集形成电流In,在NW的等效电阻上产生欧姆压降In*Rn,如果In*Rn>0.6V, NW衬底与PMOS源极p+有源区的PN结正偏,PMOS与PW的寄生PNP导通,此时寄生NPN和PNP同时导通,PNPN结构形成低阻通路,形成闩锁效应。图4-16所示的是NMOS雪崩击穿导致PNPN结构导通。

图4-16 NMOS雪崩击穿导致PNPN结构导通

4.2.3电源上电顺序引起的闩锁效应

芯片非正常的上电顺序会触发正常的ESD保护电路的二级管或者是寄生的二极管,从而触发寄生NPN和寄生PNP,导致闩锁效应。图4-17所示的是电源的ESD保护电路,当VDDH2先于VDDH1上电时,VDDH2与VDDH1之间的ESD P-diode会被导通,VDDH2把空穴注入到衬底中,如果该ESD P-diode距离其它的NMOS足够近,它们形成的PNPN结构就有可能被触发。

图4-17 两个电源的ESD保护电路

4.2.4寄生场区效应晶体管

就像寄生晶体管是CMOS固有的一样,寄生场区晶体管也是CMOS固有的。在CMOS工艺中,Poly层和金属层都可以作为互连线,Poly层和金属层就可以作为寄生场区效应晶体管的栅极,互连层与衬底之间的隔离氧化层作为栅氧化层,被poly层和金属层覆盖区域的衬底受到互连层电压的影响,场区隔离氧化层与衬底的边界聚集电荷,当互连层电压足够大时隔离氧化层下的衬底就会反型并产生沟道,从而把互连层两边的有源区连起来,形成电流通路。

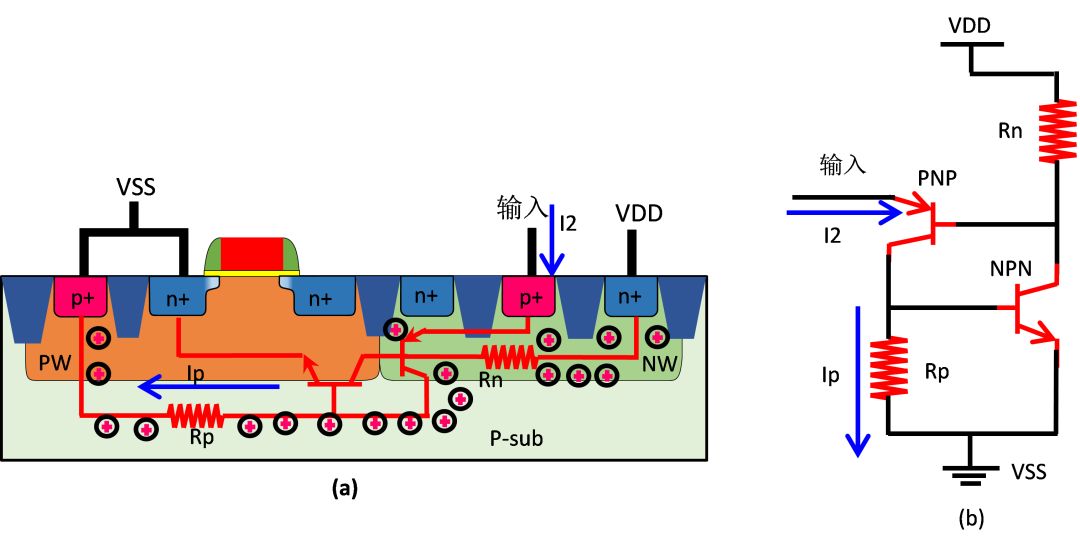

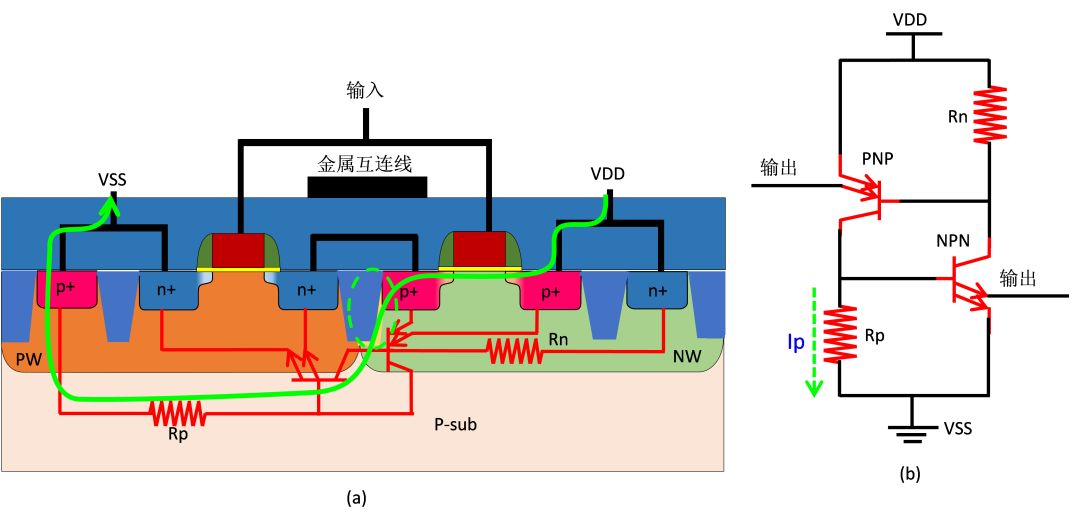

对于正的Poly层和金属层偏压,寄生场区效应晶体管NMOS可能导通。图4-18所示的是寄生场区效应晶体管NMOS。NMOS的漏极是它的源极,NW是它的漏极,当金属互连线的电压足够大时,该寄生场区效应晶体管NMOS导通,CMOS反向器中NMOS输出的信号会因为该寄生场区效应晶体管NMOS的存在,而把信号传递到VDD,In是该寄生场区效应晶体管NMOS导通后的电流,电流In在NW等效电阻Rn上产生欧姆压降In*Rn,如果该反馈电压In*Rn>0.6V,那么PMOS源极p+有源区与PW之间的PN结正偏,PMOS与PW的寄生PNP导通。寄生PNP在VDD与VSS形成通路,并产生电流Ip,电流Ip在PW等效电阻Rp上产生欧姆压降Ip*Rp,如果该反馈电压Ip*Rp>0.6V,那么NMOS源极n+有源区与PW之间的PN结正偏,NMOS与NW的寄生NPN导通,此时寄生NPN和PNP同时导通,形成闩锁效应。

图4-18寄生场区效应晶体管NMOS

对于负的Poly层和金属层偏压,寄生场区效应晶体管PMOS可能导通。图4-19所示的是寄生场区效应晶体管PMOS。PMOS的漏极是它的源极,PW是它的漏极,当金属互连线的负电压足够大时,该寄生场区效应晶体管PMOS导通,CMOS反向器中PMOS输出的信号会因为该寄生场区效应晶体管PMOS的存在,而把信号传递到VSS,Ip是该寄生场区效应晶体管PMOS导通后的电流,电流Ip在PW等效电阻Rp上产生欧姆压降Ip*Rp,如果该反馈电压Ip*Rp>0.6V,那么NMOS源极n+有源区与NW之间的PN结正偏,NMOS与NW的寄生NPN导通。寄生NPN在VDD与VSS形成通路,并产生电流In,电流In在NW等效电阻Rn上产生欧姆压降In*Rn,如果该反馈电压In*Rn>0.6V,那么PMOS源极p+有源区与NW之间的PN结正偏,PMOS与PW的寄生PNP导通,此时寄生NPN和PNP同时导通,形成闩锁效应。

图4-19寄生场区效应晶体管PMOS

4.2.5光生电流

各种形式的辐射均能在CMOS工艺集成电路的整个衬底中产生电子空穴对,光生空穴在P型衬底是多数载流子,被PW收集形成电流Ip,并在PW等效电阻Rp上形成欧姆压降Ip*Rp,如果该电压Ip*Rp>0.6V,那么NMOS源极n+有源区与PW实际的PN结正偏,NMOS与NW的寄生NPN导通。光生电子在P型衬底是少数载流子,根据双极型晶体管工作原理,这些光生电子有一部分会与空穴复合,还有一部分会扩散到PW与NW的边界附近,并被强电场加速进入集电区,最后被集电区收集,也就是被NW收集,形成NW电流In,并在NW等效电阻Rn上形成欧姆压降In*Rn,如果该电压In*Rn>0.6V,那么PMOS源极p+有源区与NW实际的PN结正偏,PMOS与PW的寄生PNP导通。此时寄生NPN和PNP同时导通,形成闩锁效应。图4-20所示的是CMOS工艺集成电路内的光生电流。

图4-20 CMOS工艺集成电路内的光生电流

4.2.6 NMOS热载流子注入

NMOS热载流子注入效应在衬底内产生电子空穴对,空穴在PW是多数载流子,会被连接到VSS的PW接触收集形成衬底电流Ib,同时热空穴会到达源极,每一个到达源极的空穴都会引起大量电子注入衬底,这些电子被漏端收集。电流Ib在PW衬底等效电阻上形成压降Vb=Ib*Rp。如果反馈电压Vb>0.6V,该反馈电压导致PW衬底与NMOS源极n+有源区之间的PN结正偏,并使NMOS自身寄生NPN导通,形成闩锁效应。图4-21所示的是NMOS热载流子注入。

图4-21 NMOS热载流子注入

如果NMOS附近存在PMOS,NMOS热载流子注入也会引起NMOS与PMOS之间的PNPN结构发生闩锁效应。NMOS热载流子注入会在PW衬底内产生电子空穴对,空穴在PW衬底是多数载流子,会被PW衬底收集形成衬底电流Ip,并在PW衬底等效电阻上形成压降Ip*Rp,电流Ip在PW等效电阻Rp上产生欧姆压降Ip*Rp,如果该反馈电压Ip*Rp>0.6V,那么NMOS源极n+有源区与NW之间的PN结正偏,NMOS与NW的寄生NPN导通。热电子会被NW收集形成电流,同时寄生NPN在VDD与VSS形成通路,也会产生电流,它们的总电流为In,电路In在NW等效电阻Rn上产生欧姆压降In*Rn,如果该反馈电压In*Rn>0.6V,那么PMOS源极p+有源区与NW之间的PN结正偏,PMOS与PW的寄生PNP导通,此时寄生NPN和PNP同时导通,形成闩锁效应。图4-22所示的是NMOS热载流子注入导致PNPN结构导通。

图4-22 NMOS热载流子注入导致PNPN结构导通

扫描二维码可以购买本书作者在创芯大讲堂《CMOS集成电路闩锁效应》视频教程。

添加微信ssywtt获取创芯大讲堂课程内部价格。

4.3小结

本章内容主要介绍了CMOS工艺集成电路闩锁效应的触发分类和触发方式。

正常情况下,CMOS是通过沟道传递电流,衬底不会出现大量电流。但是各种形式的浪涌信号和ESD脉冲信号会造成衬底出现大量的空穴或者电子,它们被PW或者NW收集形成电流,并在PW或者NW的等效电阻上形成欧姆压降,使寄生NPN和PNP导通,导致闩锁效应。本质上来说,闩锁效应的问题是衬底出现大量空穴或者电子的问题。

参考文献:

[1] CMOS技术中的闩锁效应 — 问题及其解决方法(美)R.R.特劳特曼(R.R.Troutman)著;嵇光大,卢文豪译 科学出版社

《CMOS集成电路闩锁效应》内容简介:

本书以实际应用为出发点,通过具体案例和大量彩色图片对CMOS集成电路设计与制造中存在的闩锁效应(Latch-Up)问题进行了详细介绍与分析。在介绍CMOS集成电路寄生效应的基础上先后对闩锁效应的原理、触发方式、测试方法、定性分析、改善措施和设计规则进行了详细讲解。随后给出了工程实例分析和寄生器件的ESD应用。为读者提供了一套理论与工程实践相结合的闩锁效应测试和改善方法,

本书面向从事微电子、半导体与集成电路行业的朋友,旨在给业内人士提供简单易懂并且与实际应用相结合的图书,同时也适合相关专业的本科生和研究生阅读。

《CMOS集成电路闩锁效应》作者简介:

温德通,资深ESD设计工程师。毕业于西安电子科技大学微电子学院,曾供职于中芯国际集成电路制造(上海)有限公司,负责工艺制程整合方面的工作;后加入晶门科技(深圳)有限公司,负责集成电路工艺制程、器件、闩锁效应和ESD电路设计等方面的工作;目前就职于一家全球领先的集成电路设计公司,负责闩锁效应和ESD电路设计等方面的工作。出版作品《集成电路制造工艺与工程应用》和《CMOS集成电路闩锁效应》。

《CMOS集成电路闩锁效应》出版社和出版日期:本书由机械工业出版社负责出版,将于2020年3月下旬面市。

点击阅读原文获取创芯大讲堂更多好课