新世代技术趋势 | 异质整合

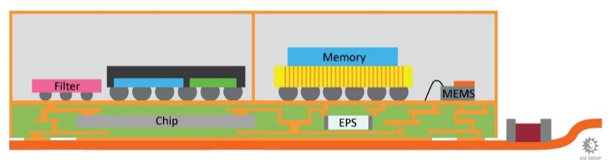

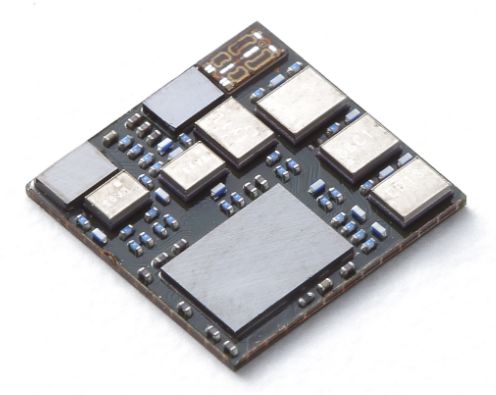

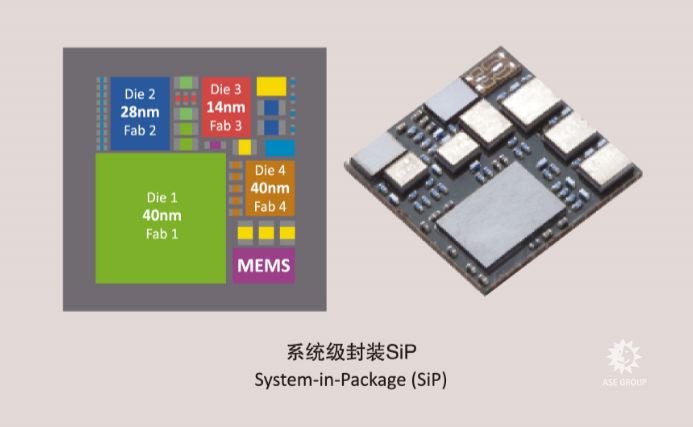

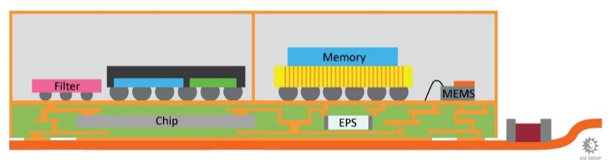

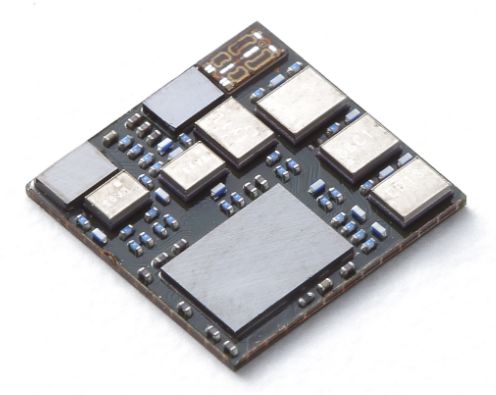

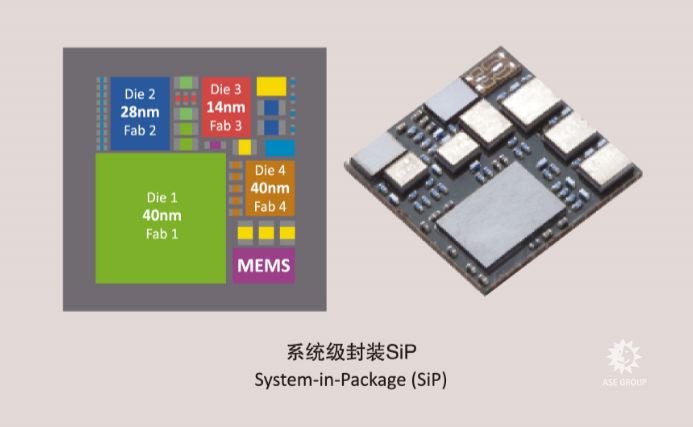

2.5D/3D IC, FOCoS, Bumping & Interconnection, Fan-In, Fan-Out, Double Side Mold, Shielding/Antenna, Stacking, Sensors/ MEMS, HD-SMT, Filter(SAW/BAW, AIC), SESUB, a-EASI, Flex Assembly, advanced Wire-Bond and Flip-Chip

2.5D/3D IC, FOCoS, Bumping & Interconnection, Fan-In, Fan-Out, Double Side Mold, Shielding/Antenna, Stacking, Sensors/ MEMS, HD-SMT, Filter(SAW/BAW, AIC), SESUB, a-EASI, Flex Assembly, advanced Wire-Bond and Flip-Chip