【中银半导体系列10】计算光刻技术管控升级,光刻工艺设备、材料、软件再迎国产化契机

以下文章来源于半导体设备与材料 ,作者杨绍辉赵琦余嫄嫄

专注半导体设备、材料与软件,做半导体产业链的坚实基础

报告要点:

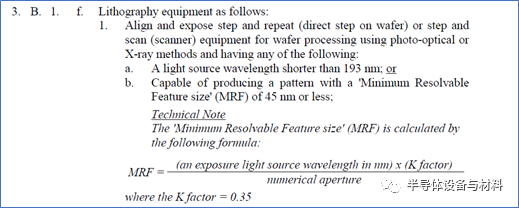

瓦森纳协议增加对EUV计算光刻软件的出口管制。根据瓦森纳主页,去年年底《瓦森纳安排》进行了新一轮修订,增加了计算光刻软件和12英寸硅片切割、研磨、抛光等方面的技术出口管制。新版《瓦森纳安排》是在原有版本基础上,增加了一条针对EUV光刻掩膜而设计的计算光刻软件内容,并保留对符合光源波长短于193 nm,或MRF(最小可分辨特征尺寸)小于或等于45 nm的光刻机的出口管制标准。

计算光刻技术是通过对掩膜、光源的正向或反演优化,降低因光波衍射影响光刻效果的程度。计算光刻是采用计算机模拟、仿真光刻工艺的光化学反应和物理过程,从理论上指导光刻工艺参数的优化。计算光刻通常包括光学邻近效应修正(OPC)、光源-掩膜协同优化技术(SMO)、多重图形技术(MPT)、反演光刻技术(ILT)等四大技术。随着线宽不断微缩,计算光刻软件成为光刻工艺环节上重要的辅助工具,其需求日益增加。

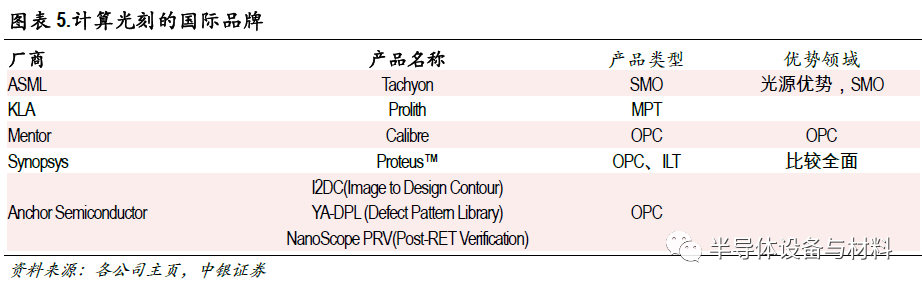

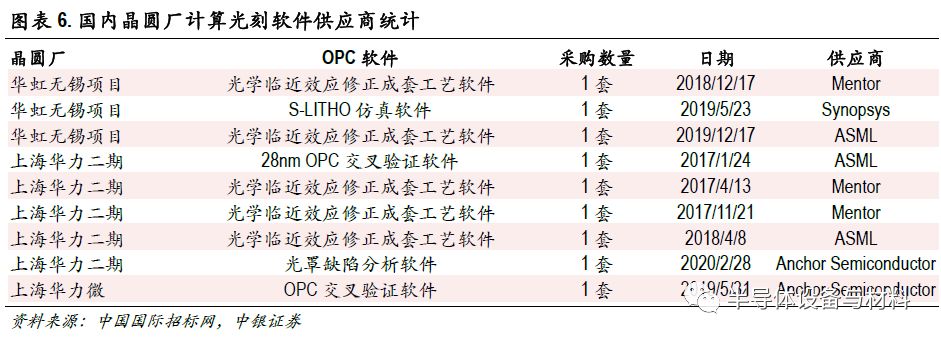

计算光刻软件产品市场被国际供应商垄断。参考中国科学院微电子研究所计算光刻课题组介绍,主流的计算光刻软件主要包括Tachyon(荷兰ASML/Brion)、Prolith(美国KLA)、Calibre(MentorGraphics)等,其中ASML在SMO有优势,Mentor在OPC优势明显,Synopsys东西比较多而全且灵活性强。但晶圆厂通常采购多个计算光刻软件品牌而达到提升议价能力的目的。根据中国国际招标网数据统计,大陆本土晶圆厂的OPC软件供应商包括ASML、Mentor、AnchorSemiconductor、Synopsys等。

计算光刻的国产化:中科院微电子所具备丰富的科研和产业化经验。中科院微电子所集成电路计算光刻与设计优化实验室成立于2013年7月,由韦亚一博士组建,参与国家科技重大专项22 nm先导光刻工艺及FinFET工艺产业转移研究,参与武汉新芯、中芯国际、华力微电子等的计算光刻技术合作研发,具备丰富的计算光刻技术理论和实践基础。目前国内从事计算光刻产业化的企业有南京诚芯集成电路技术研究院有限公司、全芯智造技术有限公司,其中南京诚芯集成电路技术研究院有限公司由国家02专项首席科学家、中国科学院微电子所计算光刻研发中心主任韦亚一组队成立;而全芯智造技术有限公司是Synopsys联合华大半导体、武岳峰、中科院微电子所等股东合资于2019年9月成立,主要从事OPC和器件仿真等的研发。

光刻工艺环节设备、材料、软件再迎国产化机遇。一是大基金二期即将启动投资,二是大基金将会对设备与材料等薄弱但关键环节予以重点支持:

(1)掩膜版:光罩产业链是很薄弱环节,从掩膜版的材料、曝光设备、检测、清洗都还没实现国产化。

(2)光源和镜头:长春光机所、上海光机所,以及产业化平台国科精密。

(3)光刻机工作台:华卓清科,其产品可应用于65nm及以下节点的ArFdry、ArFi光刻机、KrF光刻机。

(4)光刻机:上海微电子SSX600系列步进扫描投影光刻机可满足IC前道制造90nm、110nm、280nm关键层和非关键层的光刻工艺需求。

(5)光刻胶:光刻胶国产化比光刻机起步晚,I-line光刻胶可以自给,KrF光刻胶已产业化,但仍以进口为主。

(6)Track:沈阳芯源有Barc机台进入华虹系晶圆厂,也有I-line机台进入长江存储验证。

(7)去胶机:屹唐半导体在长江存储、华虹无锡等客户的市场率高。

重点推荐

随着瓦森纳对光刻技术、大硅片加工技术的出口管控升级,半导体设备、材料与软件的国产化再次受到重视,叠加大基金二期已明确会加大对设备与材料的支持力度(参考2019年半导体集成电路零部件产业峰会),包括光刻工艺在内的半导体设备、材料与软件迎来发展机遇。继续推荐北方华创、精测电子、万业企业、晶盛机电、长川科技,关注中微公司、至纯科技、芯源微、华峰测控、雅克科技、华特气体等。

评级面临的主要风险

客户项目进度低于预期,新产品工艺验证时间长且风险高。

一、瓦森纳协议增加对EUV计算光刻软件的出口管制

根据集微网,去年年底《瓦森纳安排》进行了新一轮的修订,增加了两条有关半导体领域的出口管制内容,主要涉及计算光刻软件和12英寸硅片切割、研磨、抛光等方面技术。其中,新版《瓦森纳安排》是在原有版本基础上,增加了一条针对EUV光刻掩膜而设计的“计算光刻软件”内容,而对符合光源波长短于193 nm,或最小可分辨特征尺寸(MRF)为45nm或更小的图案(MRF=曝光光源波长*0.35/NA)的光刻机出口管制标准尚未变化。

二、计算光刻技术是通过对掩膜、光源的正向或反演优化,降低因衍射影响光刻效果的程度

“计算光刻”是利用计算机建模、仿真和数据分析等手段,来预测、校正、优化和验证光刻工艺在一系列图案、工艺和系统条件下的成像性能。计算光刻通常包括光学邻近效应修正(OPC)、光源-掩膜协同优化技术(SMO)、多重图形技术(MPT)、反演光刻技术(ILT)等四大技术。随着线宽不断微缩,计算光刻软件的需求日益增加。

1、光学邻近效应修正(OPC)

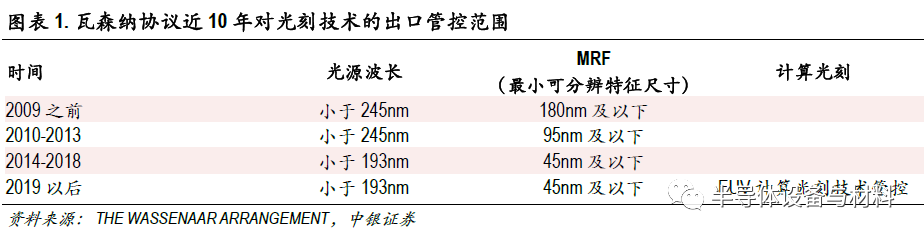

光学邻近校正(OPC)是一种光刻增强技术,主要在半导体器件的生产过程中使用,目的是为了保证生产过程中设计的图形的边缘得到完整的刻蚀。这些投影图像因光学衍射而失真如果得不到纠正,可能大大改变生产出来的电路的电气性能。光学邻近校正通过移动掩膜版上图形的边缘或添加额外的多边形来纠正这些错误。根据宽度和间距约束(即基于规则的OPC),或者是通过使用紧凑的模型动态仿真(即基于模型的OPC)的结果预先计算出一个查找表,根据这个查找表来决定怎样移动图案的边缘,找到最好的解决方案。OPC的目标是尽可能的使硅片上生产出的电路与原始的电路一致。

一般来说,当晶圆上的线宽小于曝光波长时,必须对掩膜上的图形做邻近效应修正。例如,使用248nm波长光刻机,当图形线宽<250nm时,必须使用简单的修正;当线宽<180nm时,则需要非常复杂的修正。使用193nm波长光刻机,当最小线宽<130nm时,就必须做图形修正。

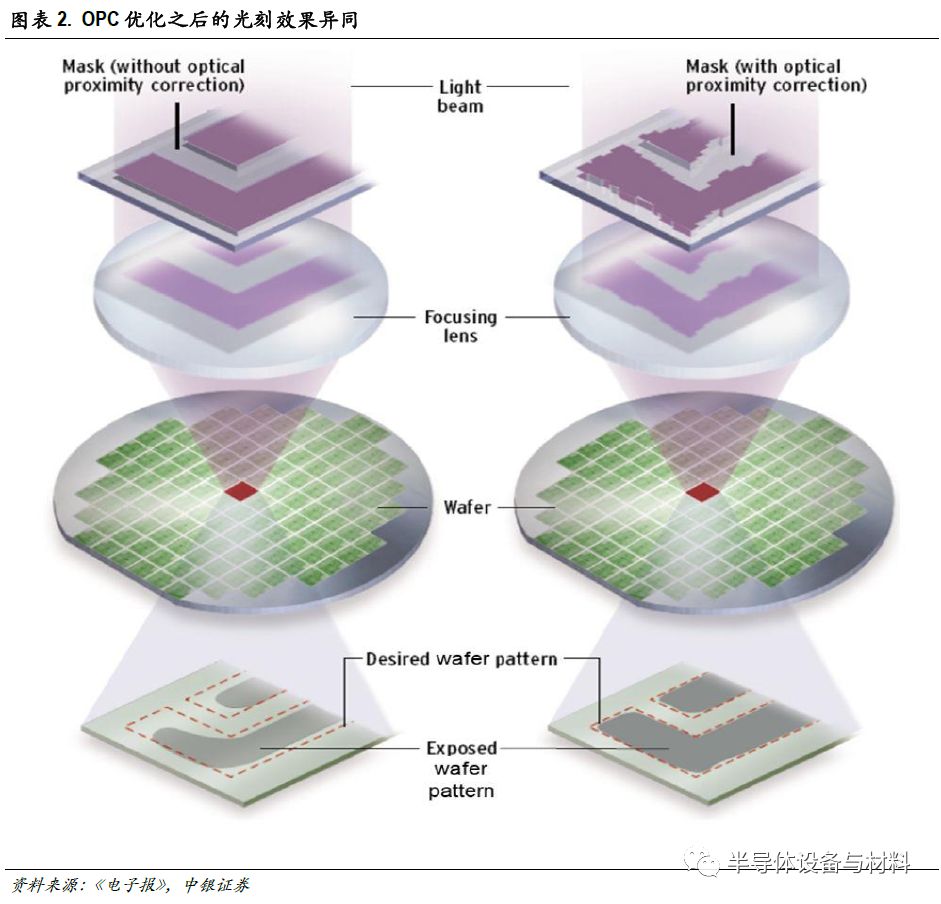

2、光源-掩膜协同优化技术(SMO)

光源—掩膜协同优化(Source Mask Optimization,SMO)仿真计算的基本原理与基于模型的邻近效应修正类似。光源—掩膜协同优化计算出的结果,不仅包含一个像素化的光源,而且包括对输入设计做的邻近效应修正。由于光照参数和掩膜上的图形可以同时变化,优化计算的结果可能不是唯一。

SMO技术是14纳米及以下技术节点必不可少的一项分辨率增强技术,针对特定层的设计规则、掩膜结构、光刻胶层属性和结构等,根据光学模型对光源形状、强度分布和掩膜形状进行同时优化,以获得具有最大光刻工艺窗口的定制型光源和修正后的掩膜形状。

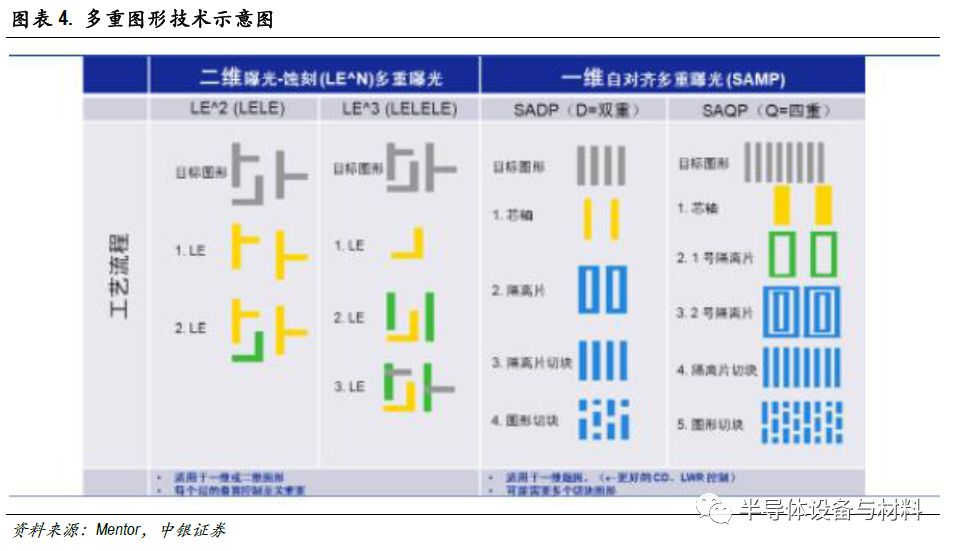

3、多重图形技术(MPT)

即用两个或更多个掩膜叠加成原始一张掩膜的形状,从而是每个掩膜形状的周围都有足够的空间实现OPC操控,进而确保可以与曝光/光刻。拆分的多个掩膜分布曝光,并最终曝光形成最初绘制的掩膜形状到晶圆上。

4、反演光刻技术(ILT)

反演光刻技术,即将光学邻近效应校正(OPC)或光源-掩膜交互优化(SMO)的过程看作逆向处理的问题,将光刻后的目标图形设为理想的成像结果,根据已知成像结果,根据成像系统空间像的变换模型,反演计算出掩膜图像。

反演光刻技术非常复杂,特别是对整个芯片而言计算量很大。目前普遍的做法是先使用通常的模型修正(OPC+SRAF)来完成掩膜数据的处理,然后找出其中不符合要求的部分。把这些“坏点”截取出来,局部做ILT处理,得到最佳的修正。最后再把经ILT处理后的部分贴回到数据中去。这种局部的ILT处理,可以节省大量的计算时间。

三、计算光刻软件产品市场被国际供应商垄断

参考中国科学院微电子研究所计算光刻课题组介绍,主流的计算光刻软件主要包括Tachyon(荷兰ASML/Brion产品,国际领先光源-掩膜协同优化软件,全球市场占有率第一)、Prolith(美国KLA公司产品,精确的光学、光刻工艺集成仿真软件)、Mentor Calibre(Mentor Graphics公司产品,业界领先的OPC专业仿真软件,美国企业,后被德国西门子收购),三种计算光刻仿真软件的功能各有侧重,在各自的细分领域里处于领先乃至垄断地位。

根据中国国际招标网数据统计,大陆本土晶圆厂的OPC软件主要采购ASML、Mentor、Anchor Semiconductor、Synopsys等厂商。

四、计算光刻的国产化正从多年科研走向产业化初期阶段

中科院微电子所集成电路计算光刻与设计优化实验室成立于2013年7月,由韦亚一博士组建,参与国家科技重大专项22 nm先导光刻工艺及FinFET工艺产业转移研究,参与武汉新芯、中芯国际、华力微电子等的计算光刻技术合作研发,具备丰富的计算光刻技术理论和实践基础。

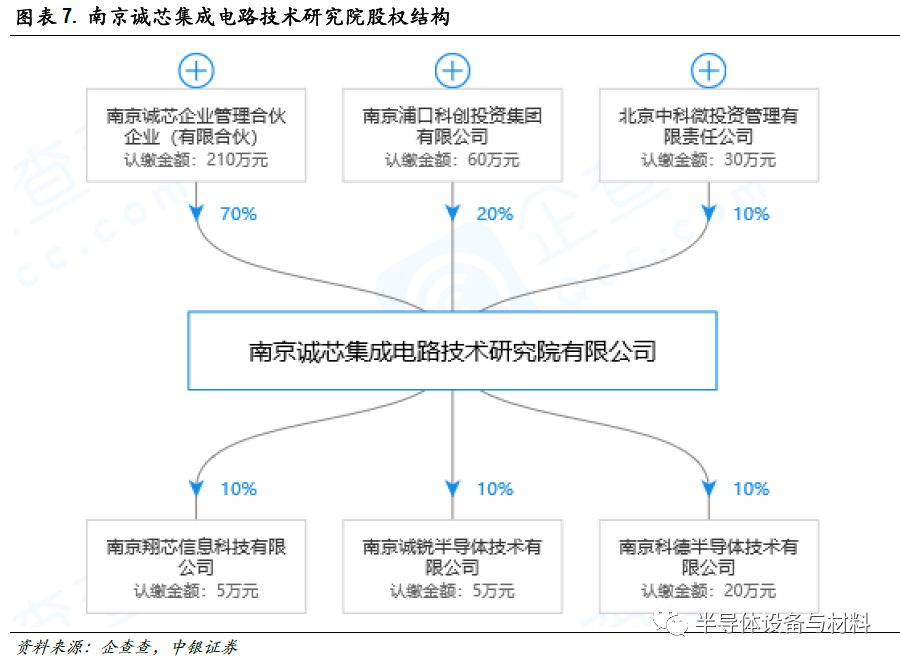

目前国内从事计算光刻产业化的企业有南京诚芯集成电路技术研究院有限公司、全芯智造技术有限公司,其中:

1、南京诚芯集成电路技术研究院有限公司于2018年11月成立,由国家02专项首席科学家、中国科学院微电子所计算光刻研发中心主任韦亚一带领团队经营,并参股南京翔芯信息科技、南京诚锐半导体、南京科德半导体等公司;

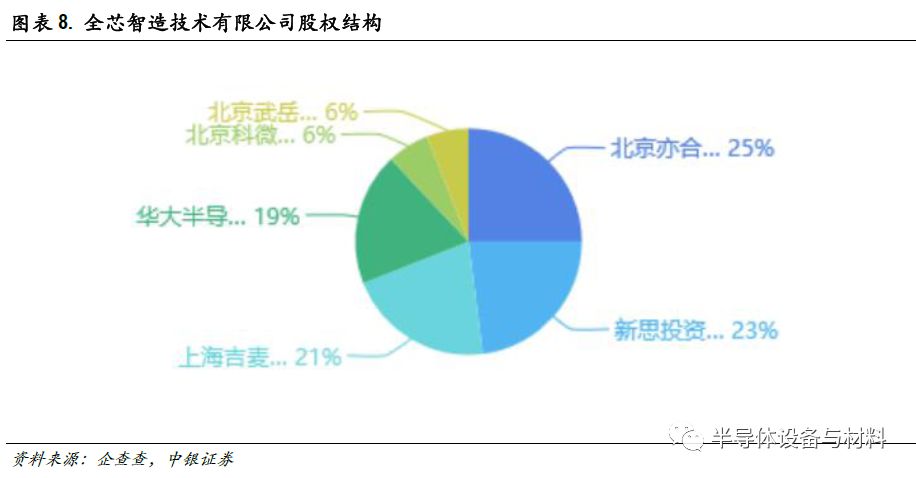

2、全芯智造技术有限公司是Synopsys、华大半导体、武岳峰、中科院微电子所等股东合资,并于2019年9月成立,主要从事OPC和器件仿真等的研发。

《半导体设备行业深度报告——装机大年到来,国产设备随芯崛起》2017-12-22

《平板显示设备行业深度报告—— OLED渐成主流且供不应求,Array/Cell制程设备开始进口替代》2017-10-10

《中微公司— 度过业务结构调整之年,刻蚀设备将主导公司未来业绩高成长》2020-3-2