一文看懂3D封装技术

以下文章来源于芯思想 ,作者赵元闯

芯思想

中国半导体正能量传播平台。为中国半导体产业服务,我们都是中国半导体产业腾飞的见证人。新闻分析,精彩评论,独家数据,为您定制信息,欢迎拍名片回复,和行业精英交流。

一、先进封装发展背景

二、三维封装技术发展

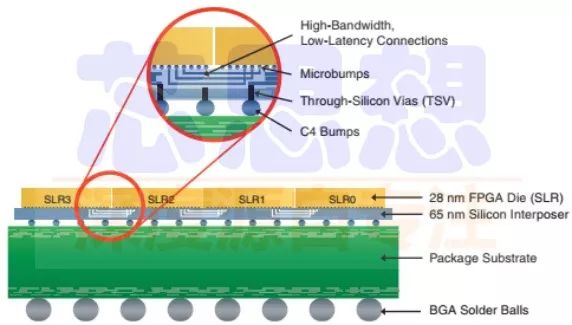

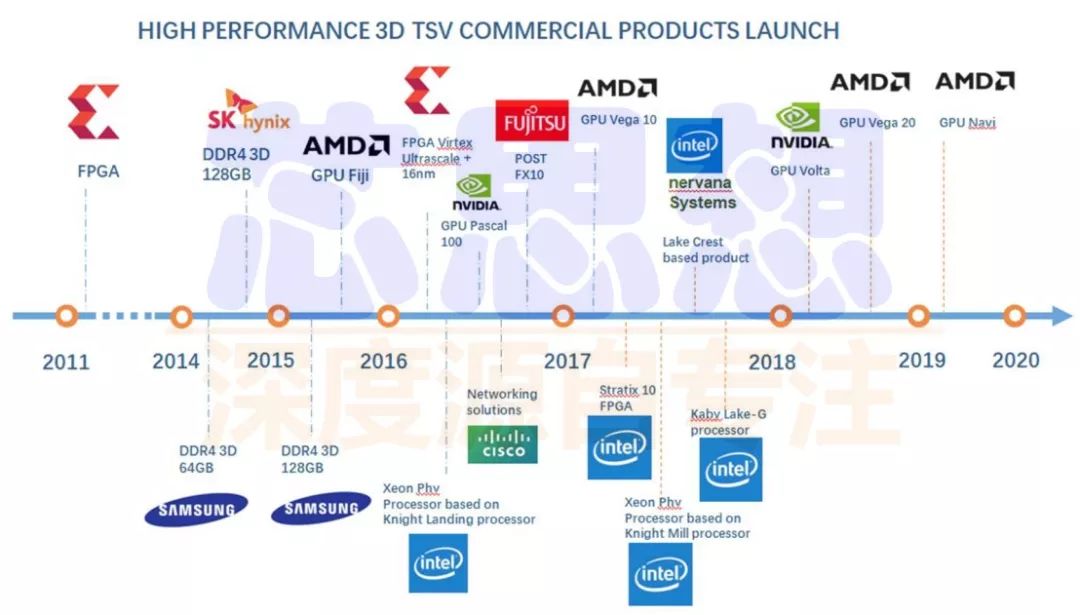

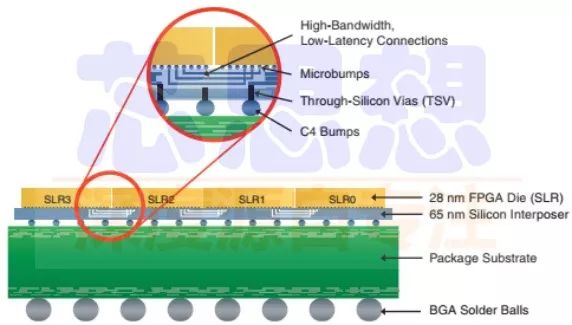

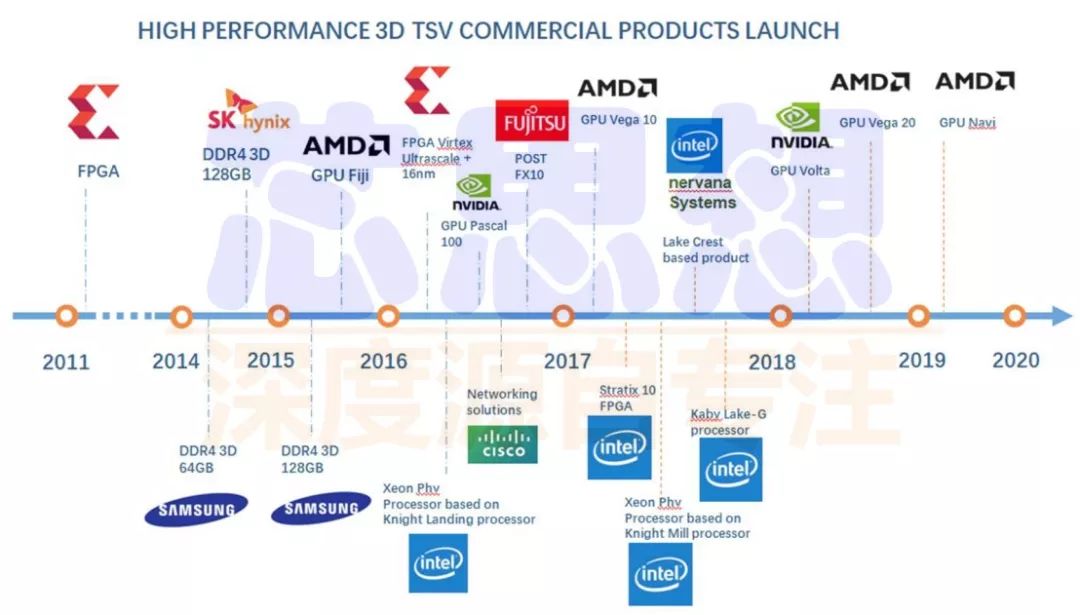

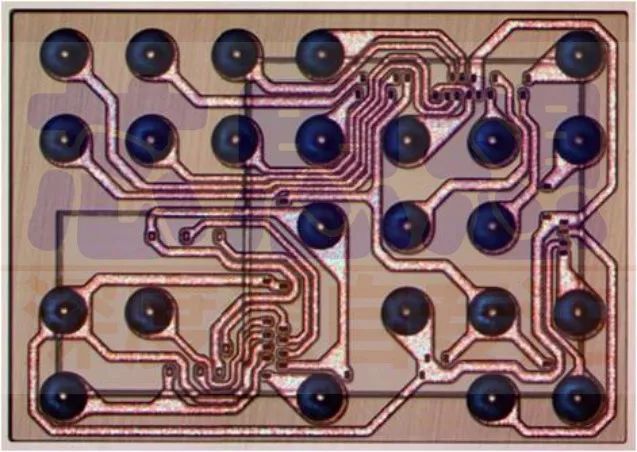

1、2.5D/3D IC技术

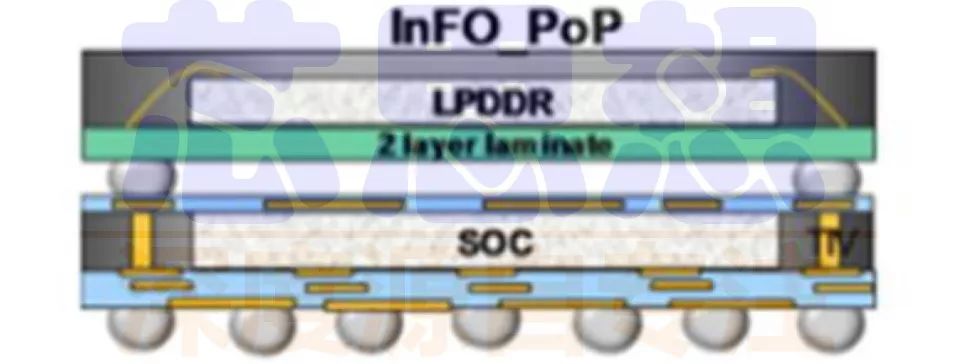

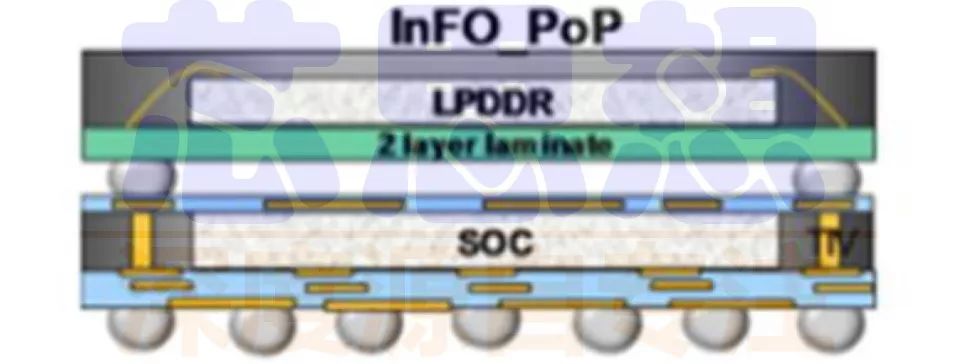

2、扇出(Fan-Out)封装技术

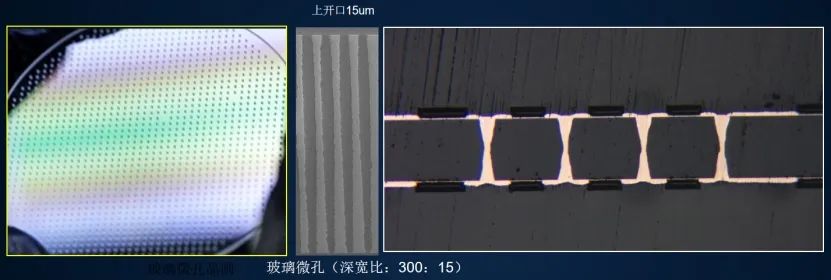

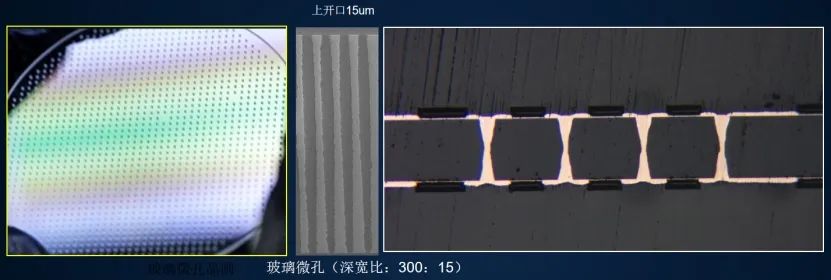

3、三维玻璃通孔封装

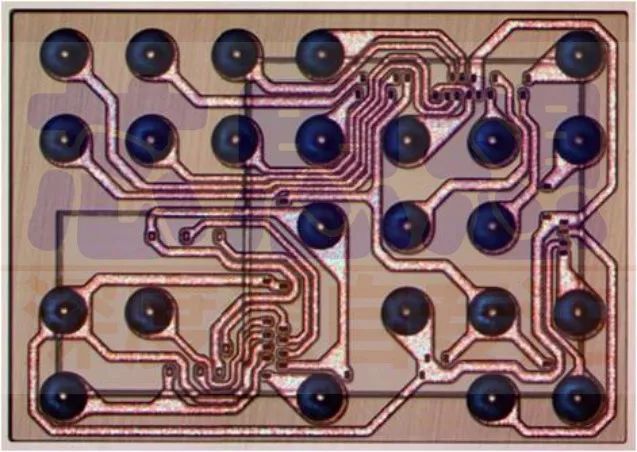

4、3D WLCSP技术

三、晶圆级三维集成新趋势

四、总结

以下文章来源于芯思想 ,作者赵元闯

中国半导体正能量传播平台。为中国半导体产业服务,我们都是中国半导体产业腾飞的见证人。新闻分析,精彩评论,独家数据,为您定制信息,欢迎拍名片回复,和行业精英交流。

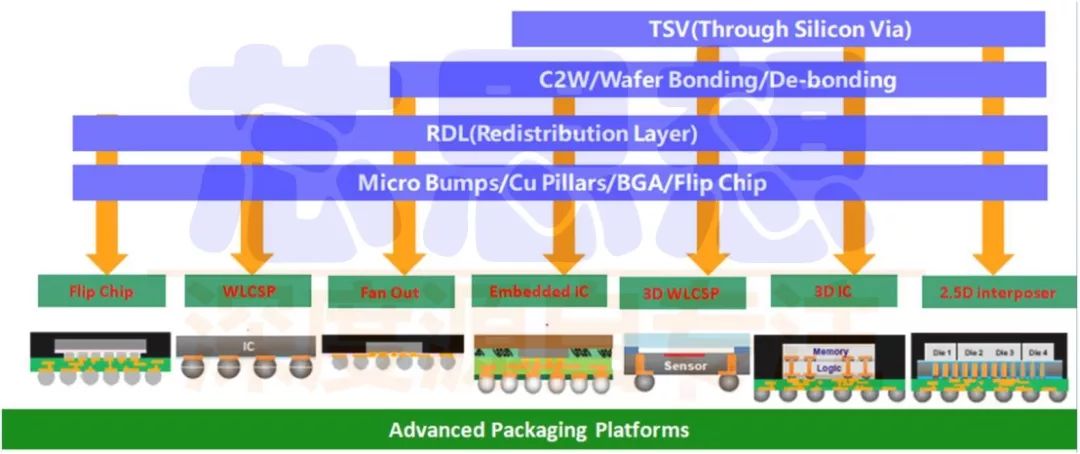

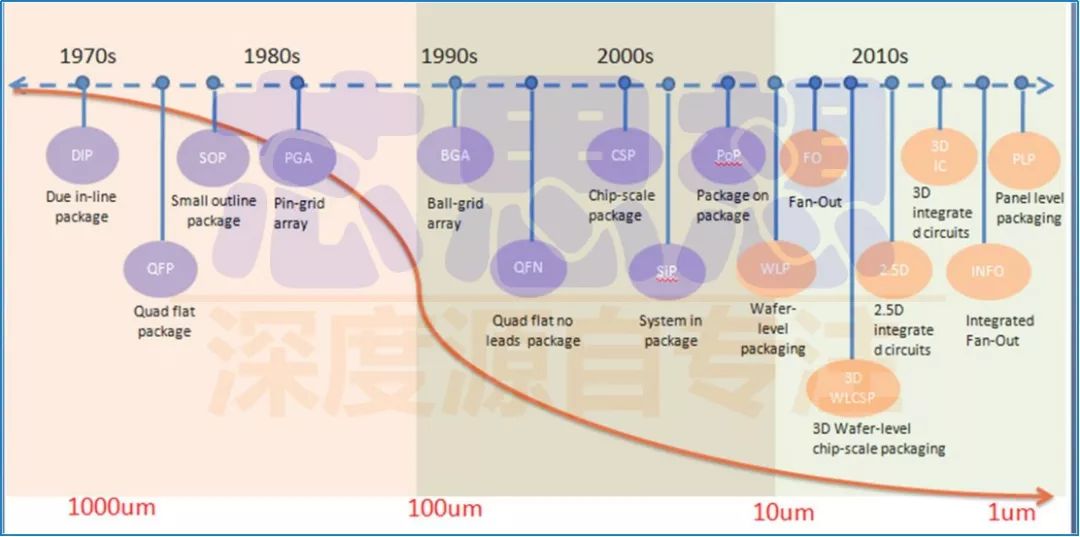

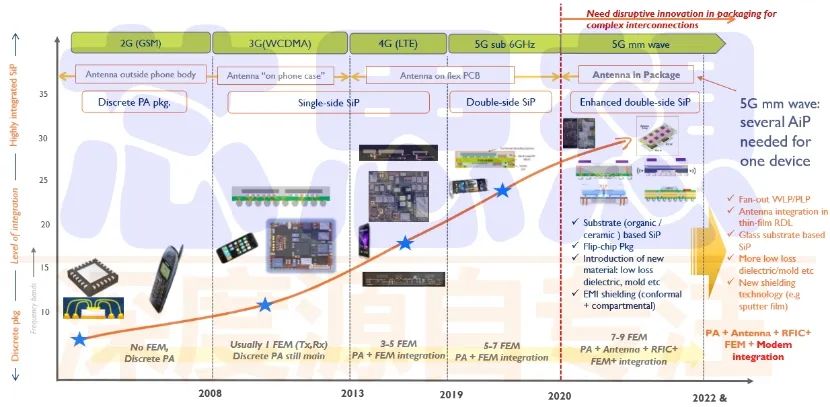

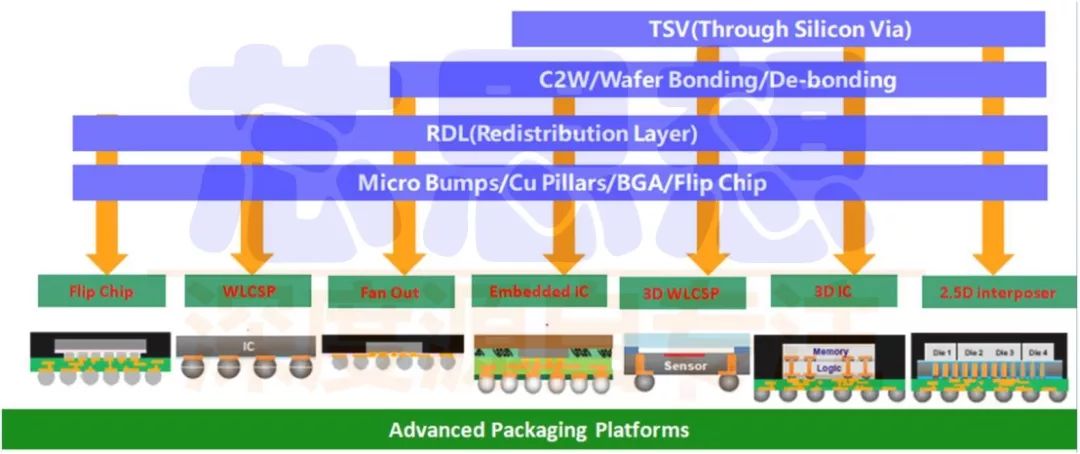

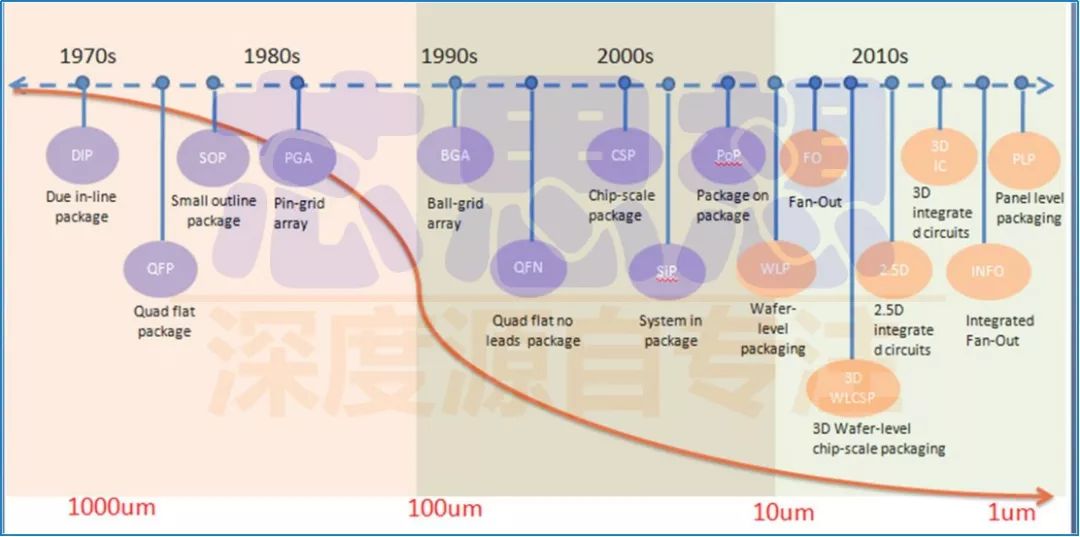

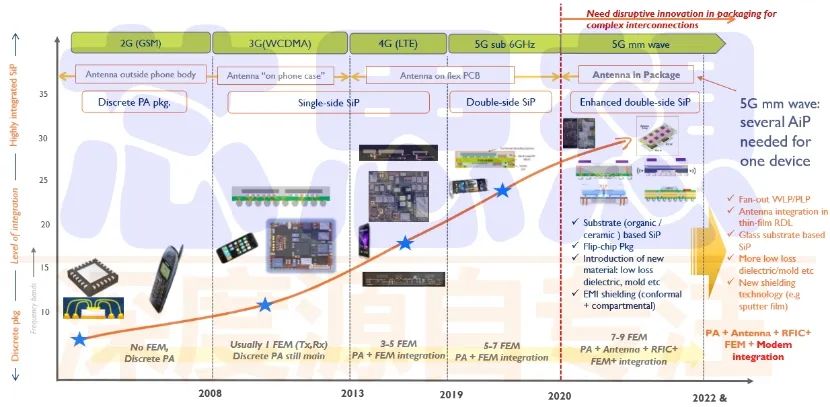

一、先进封装发展背景

二、三维封装技术发展

三、晶圆级三维集成新趋势

四、总结