Cadence发布行业首个SMIC 14nm 10G多协议SerDes PHY IP

行业首个SMIC 14nm 10G 多协议SerDes PHY IP

中国上海,2020年4月30日—— Cadence公司(NASDAQ:CDNS)宣布基于SMIC 14nm工艺的10Gbps多协议PHY研发成功,这是行业首个SMIC FinFET工艺上有成功测试芯片的多协议SerDes PHY IP。

该多协议SerDes PHY IP具有很强的灵活性,在保证PPA不损失的情况下对设计进行了简化。它采用了Cadence经过大量量产验证的Torrent架构,可以有效的帮助客户降低产品风险,缩短产品上市时间。

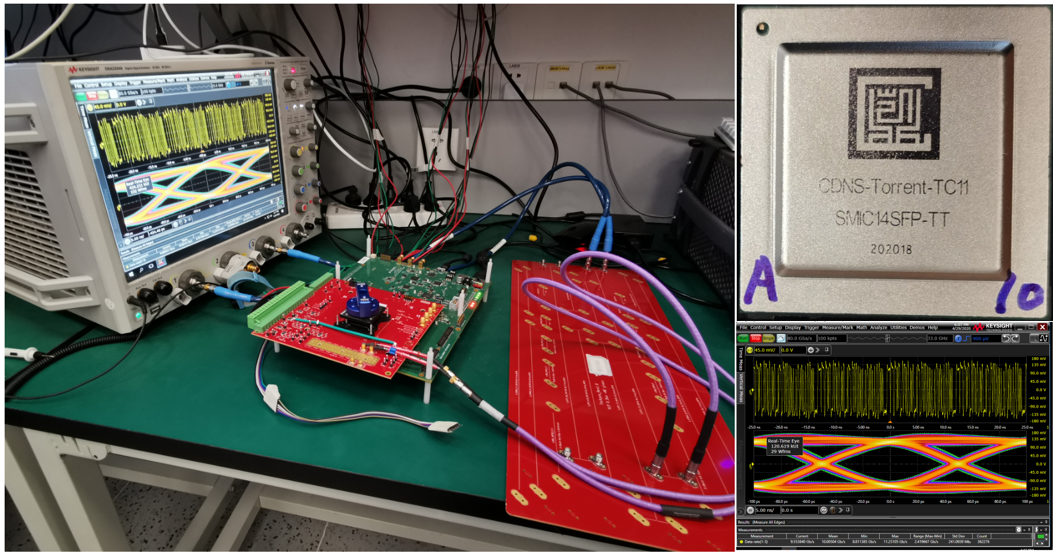

图 1 测试芯片和实际运用场景模拟演示

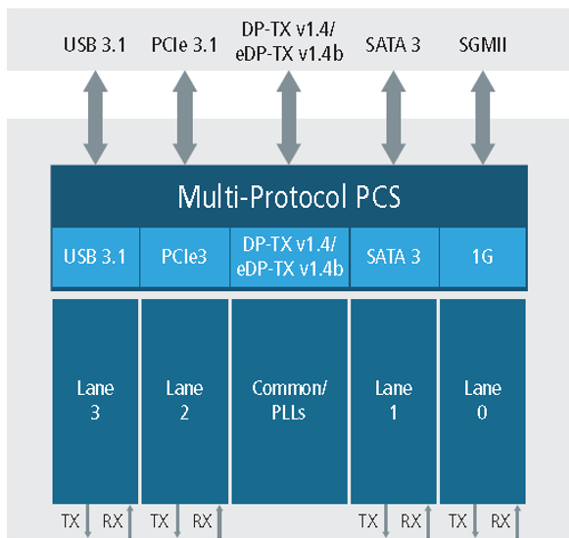

此PHY IP可以在单个macro上运行多种协议,支持从 1Gbps 到 10.3125Gbps的连续速率,适用于PCIe (Gen 1/2/3), USB 3.1 (Gen1/2), Display Port Tx v1.4, Embedded DisplayPort Tx v1.4b, JESD204b(max 10.3215Gbps), 10GBase-R, XFI, SFP+, RXAUI, XAUI, QSGMII/SGMII, 以及 SATA 3 (Gen 1/2/3) 等协议。PCS支持PIPE 4.2接口。

图2 系统级模块框图

Cadence多协议SerDes PHY IP的主要特性有:

独立链路的多协议支持

支持PCIe L1 sub-states

片上终端电阻自动校准

支持SRIS和内部SSC生成

支持多达16 通道(lanes)

支持分叉模式(bifurcation)

支持内外部时钟源动态检测

SCAN, BIST,串/并行环回功能

此多协议SerDes PHY IP可以快速、轻松地集成到SoC系统中,可以与Cadence或第三方PIPE兼容的控制器进行无缝对接。多协议SerDes PHY IP为高要求运用的客户提供了一个低成本、多功能、低功耗的解决方案。不仅为SoC集成商提供卓越的性能与灵活性,同时能够满足高性能的设计要求。

目前这款多协议SerDes PHY IP 已经可以支持SMIC14SFP 和 SMIC12SFe工艺节点。除了10G多协议SerDes PHY IP,Cadence 在2019年9月还发布了SMIC 14nm工艺下经过测试芯片验证的DDR PHY IP,它采用SMIC 自有标准库单元,支持DDR3/4/LPDDR3/4/X协议,最高速度可达4266Mbps。欢迎您通过Cadence销售渠道了解更多关于10G多协议SerDes PHY IP、DDR PHY IP 等相关信息。

关于Cadence

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向移动、云计算、数据中心、汽车、航空、IoT 和工业等最具活力的应用市场交付从芯片、电路板到系统的卓越电子产品。Cadence 已连续六年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

© 2020 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。