从三大半导体公司Chiplets(芯粒)方案看其神奇之处

不管摩尔定律会不会最终失效,但目前就有一项技术,或许能帮助延续摩尔定律,即Chiplets。

文︱苏岚

1965年,戈登-摩尔(Gordon Moore)提出摩尔定律,即当价格不变时,集成电路上可容纳的晶体管数目,约每隔12个月便会增加一倍,性能也将提升一倍。十年后的1975年,由于集成电路产业日趋成熟,摩尔修正了翻倍时间,即每隔24个月集成晶体管数目翻倍,这一定律在其诞生后的几十年时间里,一直是半导体行业可以信赖和依靠的预测模型或发展规律。

但随着芯片尺寸和制程工艺不断缩小,半导体制造也正面临越来越严峻的挑战,目前晶体管数量翻倍速度已经延缓至30个月左右。于是,很多人就会禁不住怀疑,摩尔定律是否还能延续,甚至还有更激进的想法则是,摩尔定律已死。

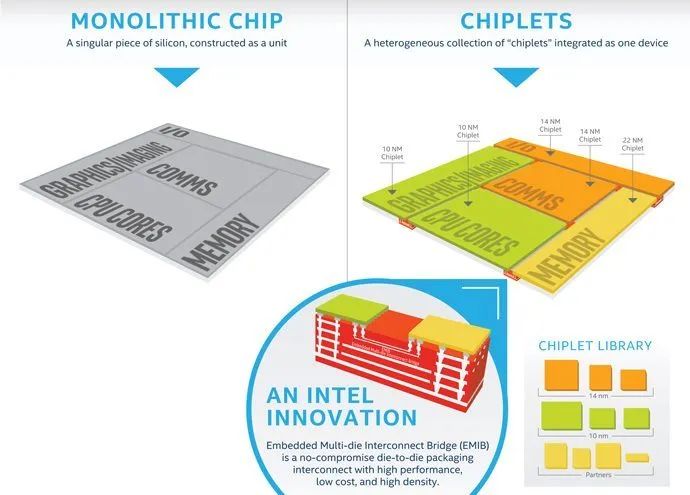

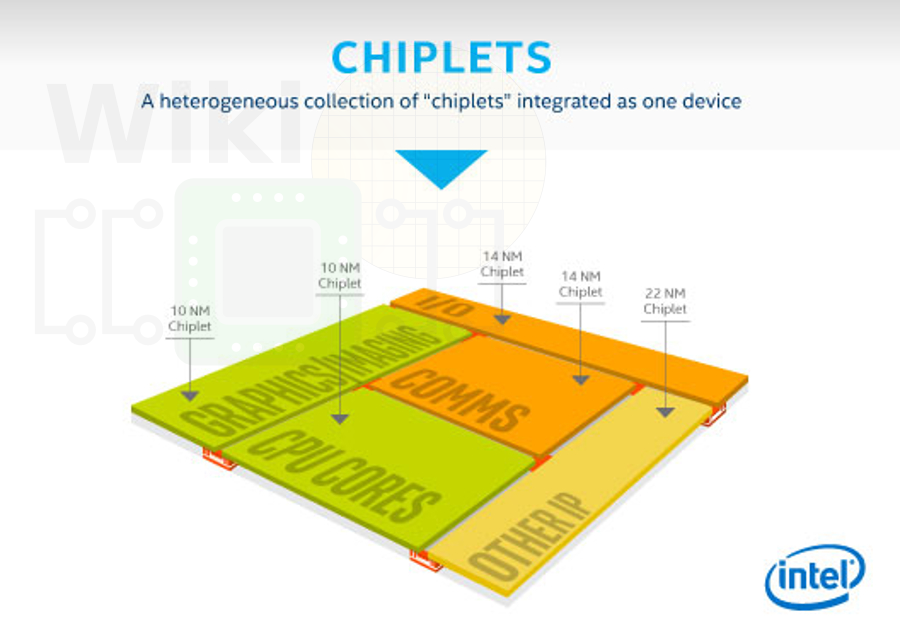

不管摩尔定律会不会最终失效,但目前就有一项技术,或许能帮助延续摩尔定律,即Chiplets。什么是Chiplets呢?Chiplets也就是“小芯片”或“芯粒”,它诞生于20世纪70年代,最近在AMD的Ryzen和Epyc x86处理器等产品中重新获得关注。它将复杂功能进行分解,然后开发出多种具有单一特定功能,可互相进行模块化组装的“小芯片”,它也是一个功能性电路块,并具有可重复使用的IP区块。目前已有很多大公司已经对该技术进行研发,如台积电、AMD、英特尔等。

根据市场研究公司Omdia预测,在制造流程中采用芯粒的处理器芯片全球市场预计将从2018年的6.45亿美元扩大至2024年的58亿美元。不到10年时间,增长9倍之多,可见,芯粒技术被寄予厚望,其市场潜力发展前景诱人。

台积电更是认为,芯粒将是未来10到20年最重要的发展成果。由于它将功能分解成一块一块进行设计和制造,这使得每一个芯粒可以被设计得尽可能小,从而增加其良率,并最小化成本。目前,越来越多的半导体器件都开始采用芯粒技术,如微处理器(MPU)、图形处理器(GPU)以及可编程逻辑器件(PLD)等,尤其是MPU,它需要一直采用最尖端的技术从而保持其竞争力。

各公司基于芯粒技术的解决方案

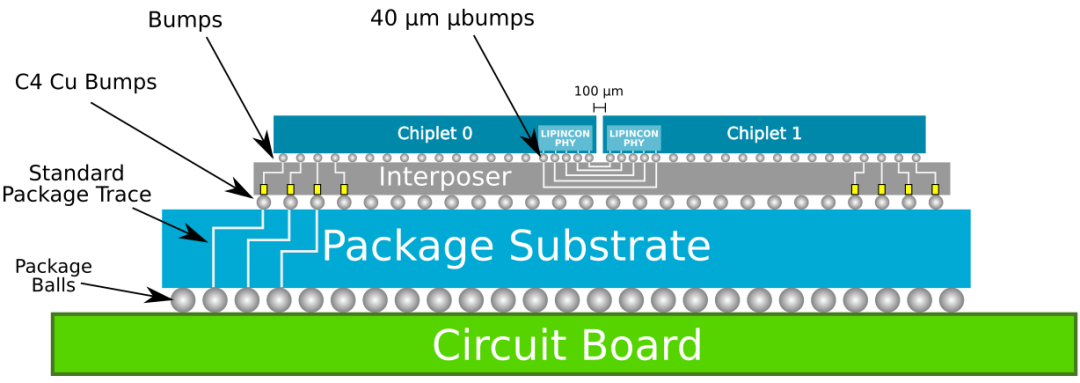

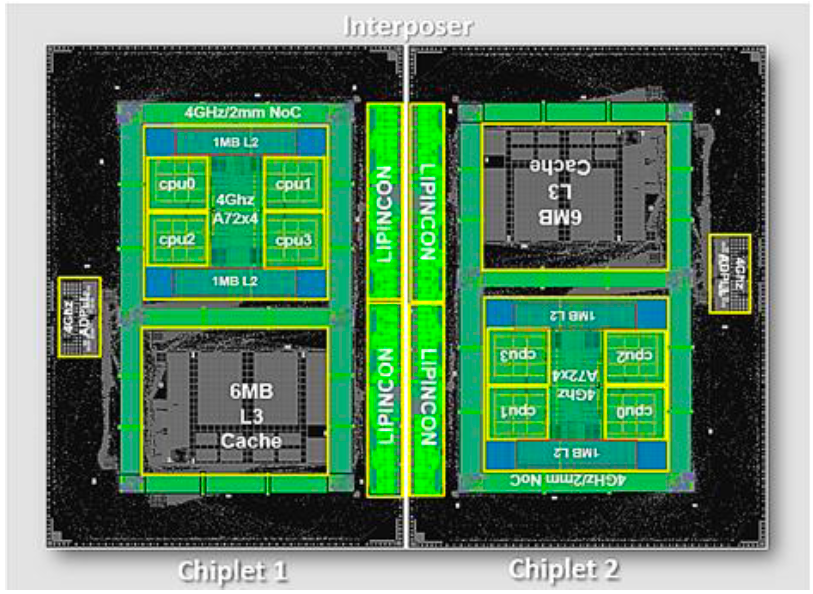

台积电基于芯粒技术的解决方案为无凸起的系统整合单晶片(System on Integrated Chip,SoIC™),它为3D架构,采用TSV(硅通孔)堆叠逻辑芯片、存储芯片,或两种芯片都连至一个有源中介层(active interposer)上。

台积电联手arm推出的7纳米chiplets解决方案

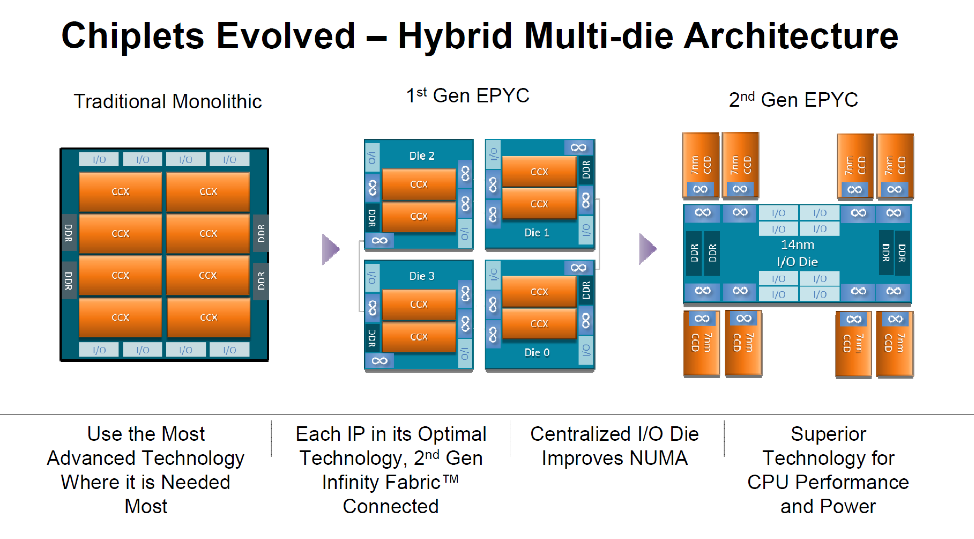

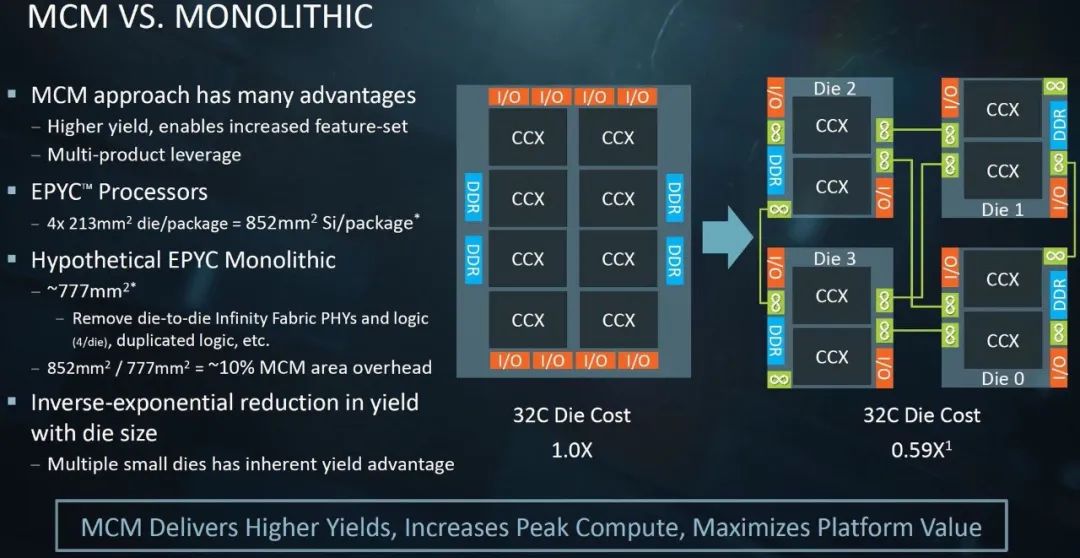

AMD目前的芯粒解决方案采用一块层压基板,它很多服务器的处理器产品已经采用了芯粒技术,例如Zen2架构就是在原来MCM多芯片设计的基础上再进一步,改用将CPU核心和I/O核心分离的芯粒技术,前者采用7纳米工艺,后者采用14/12纳米工艺,可以有效降低成本。

AMD已经量产的chiplets解决方案

Intel最新的芯粒解决方案名为Foveros,它是一种采用3D堆叠技术的异构系统集成方案。该技术采用一种3D面对面堆叠工艺,将逻辑芯片凸起并集成至一个有源中介层上,紧邻存储芯片或具有通信功能的芯片(如调制解调器)。有源中介层包括系统的有源器件,如管理系统I/O的集成南桥(platform controller hub,PCH)。Foveros技术能让设计人员更灵活地配置各种IP块,如存储和I/O等。

英特尔Foveros解决方案

结语

Omdia预测,在较长时间内,基于芯粒技术的芯片营收会持续增长,至2035年达570亿美元。特别是随着人工智能、物联网等新兴应用的不断发展,对于功耗和成本的要求也会越来越高,这些应用必将推动新的技术的发展,相信芯粒就是其中之一。芯粒可能不是唯一一个能够帮助延续摩尔定律的技术,但它的确是一个创新的技术,可以帮助推进新的封装技术、新的半导体材料的发展。众多的开发者和研究者会开创一个竞争的格局,有了竞争才会有进步,相信芯粒在承载众多期望下,也会不负众望。

参考文章:

Chiplets: The New Era Begins,Jan Vardaman

Chiplets Promise to put Moore’s Law Back on Track,Tom Hackenberg

END