很多文章探讨了前沿工艺并比较工艺密度。我经常得到的一个评论是,我提出的工艺密度数字与发布产品上的实际晶体管密度不相关。很多人想当然地将英特尔的制程与基于苹果手机应用处理器使用的台积电的制程与相比较,这不是有效的比较!在本文中,我将回顾我用于晶体管密度的度量标准,为什么使用它们以及为什么在产品设计上比较晶体管密度无效。我要发表的第一个评论是我不是电路设计师,因此我对创建可能影响最终产品晶体管密度的设计决策的所有方面都不熟悉,但是我确实有了解在给定过程中可能发生的密度差异。逻辑设计由标准单元组成,标准单元的大小由4个参数驱动,M2P,TH,CPP,SDB与DDB。

标准的高度是M2P乘以轨道数(tracks,轨道高度或TH)。近年来,为了继续缩小标准单元的面积,在降低TH的同时降低了M2P,这被称为设计技术协同优化(DTCO)的一部分。降低TH的一个关键方面是,由于空间限制,在低TH时必须减少每个晶体管的Fin数量,这称为fin depopulation。如果减少每个晶体管的Fin数量,则从每个晶体管获得的驱动电流会减少,除非您采取其他措施来补偿它,例如增加Fin高度,从而增加DTCO。

标准单元的宽度取决于CP),工艺是否支持SDB或DDB以及单元的类型。例如,NAND Gate的SDB宽度为3 CPP,DDB的宽度为4 CPP。另一方面,SFF单元的宽度大约为19 CPP(带SDB)和20 CPP(带DDB)(这可能因SFF设计而异)。如您所见,对SDB和DDB的影响比对SFF单元的影响更大。

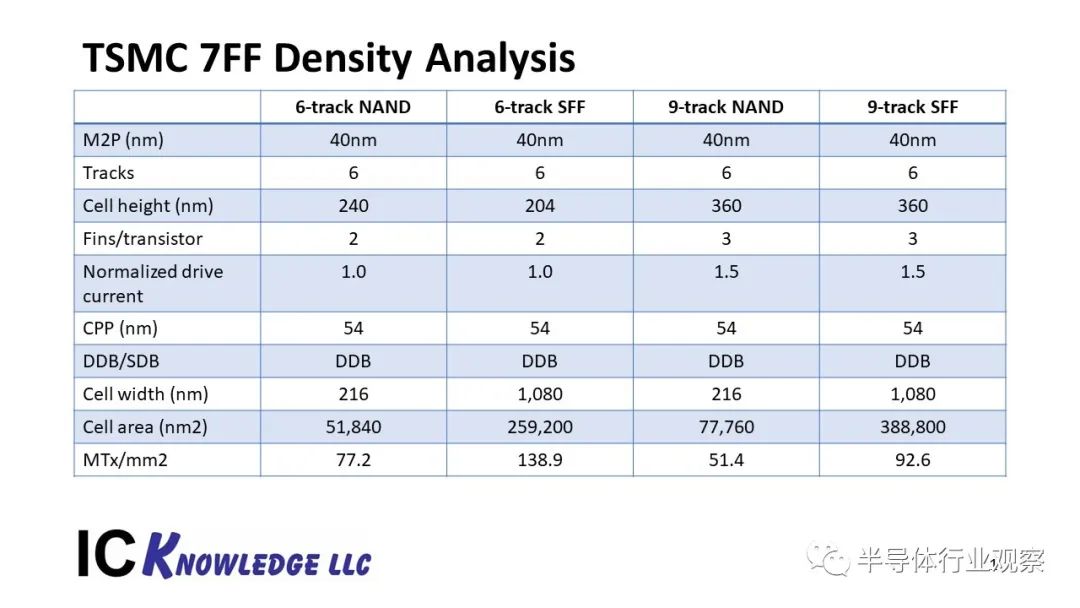

在讨论过程密度时,我总是比较最小单元大小,但是过程提供了多个选项。例如,台积电(TSMC)的7nm 7FF工艺提供了一个最小单元,即一个6-track cell,每个晶体管2片鳍,而9-track cell,每个晶体管3片鳍。9-trcak cell提供的驱动电流是6-track cell的1.5倍,但尺寸也是1.5倍。这说明了将两种产品设计作为表征晶体管密度的一种方式进行比较时的问题之一,高性能设计将具有更多的9-track cell,因此与针对最小尺寸或更低功耗6-track cell的设计相比,晶体管密度更低。-在同一过程中跟踪单元。甚至NAND单元相对于SFF单元的优势也会影响晶体管的密度。

图1总结了TSMC 7FF工艺在6 tracks和9 tracks cell之间的密度差异。请注意,MTx / mm 2参数是基于60%NAND单元和40%SFF单元的每平方毫米百万晶体管。从图1可以看出,最小面积的SFF单元在同一工艺中的晶体管密度是高性能NAND cell的2倍以上。还有许多其他类型的具有不同晶体管密度的标准单元。

大多数片上系统(SOC)电路都包含大量的SRAM存储器阵列,实际上,超过一半的裸片面积是SRAM阵列并不罕见。

7FF工艺提供了一个高密度6晶体管(6T)SRAM单元,该单元的面积为0.0270平方微米,得出的密度为222 MTx / mm 2。从理论上讲,设计上的大量存储阵列区域可能会导致更高的晶体管密度,但是,与很多与比较工艺密度有关的事情并没有那么简单。在为客户做项目时,我分析了3个TSMC SRAM测试芯片,并将SRAM阵列嵌入4个Intel芯片和1个AMD芯片中。根据过程的SRAM单元大小和阵列的位容量,SRAM阵列的平均大小为预期的2.93倍。据推测这是由于互连和访问存储器的电路。如果我们在阵列中的SRAM单元上将SRAM的晶体管密度作为基础,则密度会下降至75.84 MTx / mm 2,尽管在访问电路中肯定有一些晶体管没有计算在内。

某些SOC设计也可能包括模拟,I / O和其他元件,这些元件的晶体管密度明显低于最小单元。

最重要的是,如果您可以实现相同的设计,例如将具有相同SRAM数量的ARM内核应用于不同的过程,则可以使用实际设计来比较过程密度,但是由于这种方法不可用,因此需要某种类型的需要可以持续应用的代表性指标。当我比较工艺时,我比较了具有60%NAND单元/ 40%SFF单元比率的最小尺寸逻辑单元的晶体管密度。这不是一个完美的指标,但是可以比较相同条件下的过程。我还要提及的是,对于生产过程,我的计算是基于产品尺寸(通常由TechInsights测量),而不是基于我所研究的各个公司的信息。在估算未来的工艺密度时,我会使用公司公告中的信息。

看完有什么感想?

请留言参与讨论!

如侵权请联系:litho_world@163.com