来源:本文由半导体行业观察编译自CTIMES,谢谢!

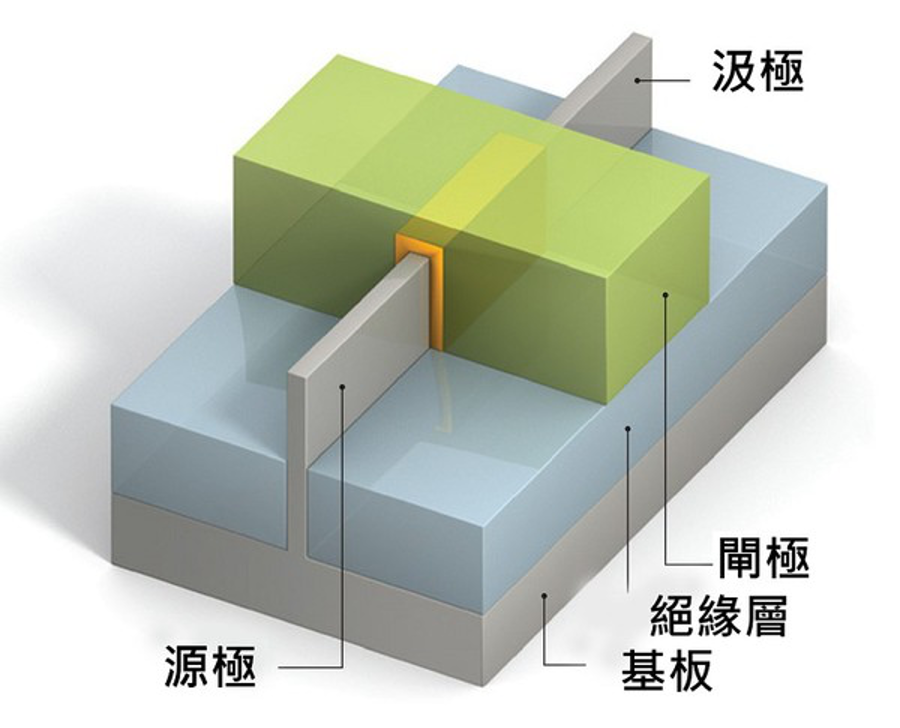

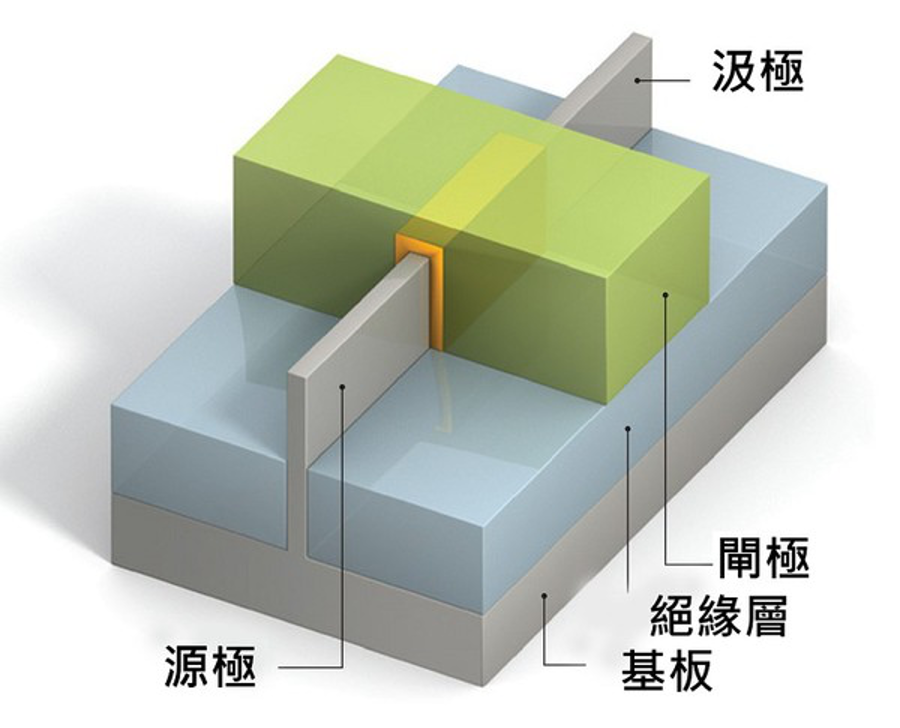

台积电终于在今年第一季的法人说明会里,透露了其3纳米将采取的技术架构,而出乎大家意料的,他们将继续采取目前的「FinFET」晶体管技术。而这代表了台积电的制程微缩能力远超乎市场想像,3纳米仍不是其极限所在。当制程下探,电路无可避免的会遭遇到控制的困难,产生如漏电、电压不稳定等的短通道效应(Short-channel Effects)。而为了有效抑制短通道效应,尽可能的增加电路的面积,提高电子流动的稳定性,就是半导体制造业者重要的考量,而鳍式晶体管(FinFET)架构就因此而生。FinFET运用立体的结构,增加了电路闸极的接触面积,进而让电路更加稳定,同时也达成了半导体制程持续微缩的目标。但这个立体结构的微缩也非无极限,一但走到了更低的制程之后,必定要转采其他的技术,否则摩尔定律就会就此打住。也因此,三星电子(Samsung)在2019年就宣布,将在3纳米制程世代,改采闸极全环(Gate-All-Around,GAA)的技术,作为他们FinFET之后的接班制程;无独有偶,目前的半导体龙头英特尔(Intel),也在不久前宣布,将投入GAA技术的开发,并预计在2023年推出采用GAA制程技术的5纳米芯片。由于世界前两大的半导体厂都相继宣布投入GAA的怀抱,因此更让人笃定,也许3纳米将会是GAA的时代了,因为至3纳米制程,FinFET晶体管就可能面临瓶颈,必须被迫进入下个世代。但唯独台积电,仍将在3纳米世代延续FinFET晶体管的技术。而就如同所有的业者,台积电的选择考量也是商业决策下的结果。而他们能做下这个决定,多少也意味着他们确认了3纳米并非FinFET技术的瓶颈,甚至还非常有自信能够在相同的FinFET技术下,在3纳米制程里取得水准以上的良率。这也代表着台积电的微缩技术远超过其他的芯片制造商。所以台积电将会在相同的制程技术与制造流程下,进入3纳米世代,也因此他们不用变动太多的生产工具,也能有较具优势的成本结构。而对客户来说,也将不用有太多的设计变更,也有助于客户降低生产的成本。若最终的产品性能还能与竞争对手平起平坐,那台积电可能又将在3纳米产品世代再胜一筹。尤其是对客户来说,在先进制程的开发里变更设计,无论是改变设计工具或者是验证和测试的流程,都会是庞大的成本,时间和金钱都是。因此若能维持当前的设计体系,对台积电和客户来说,都会是个双赢局面。剩下的问题,就是谁的效能表现比较好,而这个答案只有在2022年3纳米芯片量产之后才会知道。由于最先进制程的产品,都是运用在最高阶的产品上,这些产品的价格高,因此成本相对较不明显,一旦效能优势无法凸显,就会失去消费者的支持,进而失去订单。过往的三星电子就数次面临此一局面。尽管他们的价格较低,但是产品的效能始终无法超越台积电,因此一流的大厂都转往台积电投单,让他们在高阶晶圆代工的市场上频频失利。因此进入3纳米世代后,若三星的GAA制程在效能上可以胜过台积的FinFET,即使价格较高,都可能反转当前的先进芯片代工的市场局面。

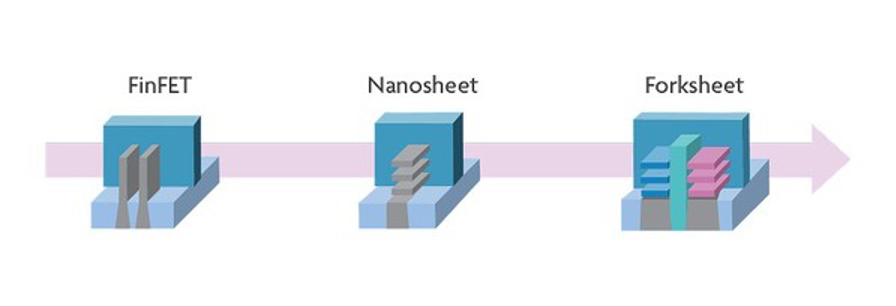

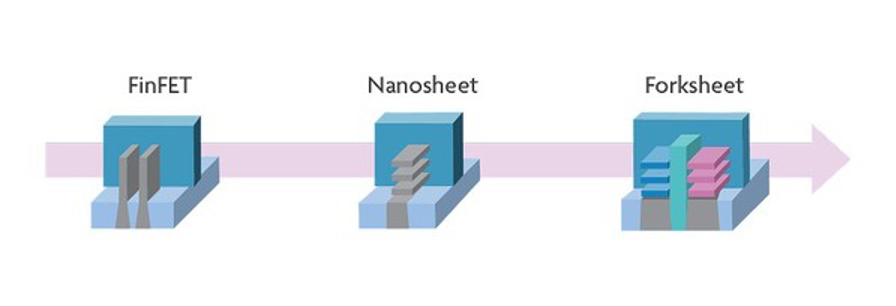

FinFET技术的片状结构成功延续了摩尔定律,但还能走多远?。另外一个问题,就是FinFET技术还能延续多久?如果3纳米不是瓶颈,那会是哪里?所幸,目前的可能的答案也只剩下两个,如果不是2纳米,就是1纳米。但无论是哪一个,都要很多年以后才会知道。但我们可从过去台积电的发言来看,他们对于微缩技术相当有信心,认为做到1纳米也不是问题,0.1纳米都可以挑战看看。再对照他们在3纳米世代所采取的策略,我们更可以大胆预测,也许要走到1纳米世代,才能摸清楚台积电的能耐,但那已经是一个完全无法想像的超级先进芯片制造技术。然而,FinFET制程终究会步入它的物理极限,接班技术的布局也应该要开始策动,而目前看起来,采用加大闸极电路面积的GAA技术会是最可能选项,其中Nanosheet FET又会是最适合的制程,目前三星也是采用此一结构,作为其3纳米世代的核心技术。当然Nanosheet FET也不是唯一的选项,目前仍有许多的研究机构针对3纳米之后的芯片制程技术进行研究。例如爱美科(imec)日前也宣布了一个名为「Forksheet FET」的技术,用以在2纳米的芯片制造。依据爱美科的资料,在「Forksheet FET」结构中,nFET和pFET被整合在同一个结构中,其中有一个介电墙把nFET和pFET分开。它也跟目前的GAA制程完全不同,也将使用不同的装置来生产nFETs和pFETs。这个技术的优势就在于它有更紧密的n到p的间距,并减少面积缩放。与Nanosheet FET相比,在相同的制程下,Forksheet FET的电路更加紧凑(42nm vs 45nm)。

与Nanosheet FET相比,在相同的制程下,Forksheet FET的电路更加紧凑。(Source:imec)除此之外,爱美科也在研发一种称为CFET(Complementary FETs)的技术,它是另外一种GAA的架构,为针对2纳米以下制程所开发。该技术由两个分开的Nanowire FET所组成(n型和p型),是一种把p型纳米线叠在n型纳米线上的结构。透过这种叠加的形式,CFET等于是实现了一种「折叠(folding)」的概念,借此消除了n到p分开的瓶颈,同时也减少了运作单元活动区域(cell active area)面积达到2倍之多。目前这些仍在研发中的技术都有更自的挑战待突破,包含散热的控制和制造成本等,但可以确定的就是,对于2纳米之后的芯片制造,现在已有数项技术正在进行中,同时也不会是遥不可及。

从现在分歧的制程技术采用决策来看,显然半导体制造商在3纳米之后的芯片制造,已经面临了需要转进新架构的挑战,而且目前仍未有主宰的技术出现。当此之时,除了制造商需要各显本事之外,如何从技术与成本中取得最大的利基,将是竞争的关键所在。特别是先进半导体制造的成本十分高昂,若不能在生产技术与制造成本中取得较佳的平衡,未来的发展也将会非常艰辛,再加上半导体的制造供应链牵连体大,不仅是制造设备,也包含设计工具和检验测试的部分,若不能有一致性的解决方案,想要一枝独秀也将是非常困难。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2331期内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

两会|台积电|RISC-V|汽车芯片|AI|EDA|中美|晶圆 | 射频

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!