RISC-V给FPGA带来的新机遇

EETOP专注芯片、微电子,点击上方蓝字关注我们

EETOP创芯网(易特创芯):国内著名的老牌电子工程师社区及半导体行业门户网站(150万会员)

blog.eetop.cn edu.eetop.cn

RISC-V的发展速度比我预期的要快得多。我认为这将给FPGA带来一个巨大的机会,使其可以更多地蚕食ASIC和ASSP。大多数SoC在通往ASIC的路上都要使用到FPGA,首先使用基于FPGA的仿真或原型设计进行验证。在ASIC开发的同时,许多SoC项目开始以FPGA的形式发布。而RISC-V可以帮助FPGA推迟甚至取消开发ASIC的计划。

对FPGA公司来说,好消息是生态系统的工作越来越多地由RISC-V开源社区来完成。开发ISA、工具链和软件栈的重任不再落在一家公司身上。将FPGA插入RISC-V生态系统剩下的唯一步骤是将RISC-V核心产品化,用于FPGA并可迁移到ASIC。

RISC-V将改变嵌入式处理器的格局

下一代SoC将在很大程度上依赖定制化的处理器来实现特定领域的架构(DSA),以实现摩尔定律无法再提供的性能和功耗提升。像苹果、高通和三星这样的一线公司多年来一直在做这件事,他们拥有庞大的设计团队和昂贵的架构授权,可以定制ARM处理器。而其他公司则推出自己的硬件加速器,或者将定制指令添加到像ARC和Tensilica这样的平价处理器内核中。

对于许多基于边缘的设备来说,ARM定制化并不是一个经济实惠的主流选择。ARC和Tensilica都是专有的ISA,随着RISC-V横空出世,它们将无法扩展到业界通用的处理器平台。

RISC-V已经成为创新者的首选。它本身就具有低功耗的特点----从一开始就有了一个干净的起点,它可以用最少的指令集来实现,避免了传统ISA的臃肿。它的开发考虑到了架构创新--支持16位到128位指令、自定义扩展、多核、多核、多核和硬件加速--它已经成为开发基于硬件的网络安全系统的第一大ISA。

ARM的市场霸主地位在未来几年内都是靠着传统软件和在移动领域的垄断地位来保证的。然而,开源的RISC-V创新浪潮将改变我们所知道的嵌入式处理器的其他领域:

大规模协作将把RISC-V生态系统构建到使专有ISA遭到淘汰

MIPS,ARC,Tensilica,MicroBlaze,Nios都会淡出

主要的创新工具将是RISC-V和FPGA

创新浪潮将流向拥有最佳RISC-V支持的FPGA公司

RISC-V具有成为ASIC处理器平台所需的条件。RISC-V开源社区已经完成了日益强大的RISC-V生态系统工作。值得重复的是--开发ISA、工具链和软件栈的重任不再由一家公司来承担。将FPGA插入RISC-V生态系统所需的唯一事情就是为FPGA生产且可移植到ASIC的RISC-V内核。

FPGA的机会

我前面说过,RISC-V可以帮助FPGA激励推迟甚至取消开发ASIC的计划,讽刺的是,增加从FPGA到ASIC的发展路径是增加FPGA收入的机会。让我们看一个简单的例子。

随着FPGA集成了越来越多的标准组件,如以太网、USB、PCIE、DDR和多核处理器子系统等标准组件的硬核,在向ASIC转型的道路上,机会成倍增加。而新的应用工作负载要求架构和内存优化超过频率的新的应用工作负载,使得SoC的性能对可编程逻辑的低速不那么敏感。令人惊讶的是,新的计算结果表明,即使是MCU(微控制器)(标准的现成ASIC SoC)也对运行处理器软核的FPGA敞开了大门。

在高端的MCU(32/64位处理器,GHz频率),需要DSA的新的工作负载将消除通用MCU作为一种选择。下一个选择是可配置的SoC(cSoC)--具有FPGA可编程逻辑的MCU。如果DSA映射到cSoC,并满足性能、功耗和成本限制,那么SoC就会从MCU转到cSoC。

如果没有,那么下一个选择是spin ASIC,这将从FPGA原型或仿真开始,因为验证架构性能的唯一确定的方法就是在硬件上运行应用代码。在这个过程中,一个意料之外的方案可能是一个通用FPGA,它的处理器软核能够提供足够好的性能。如果通用FPGA符合产品的功耗和成本要求,那么就会从MCU转到带有软核处理器的通用FPGA。

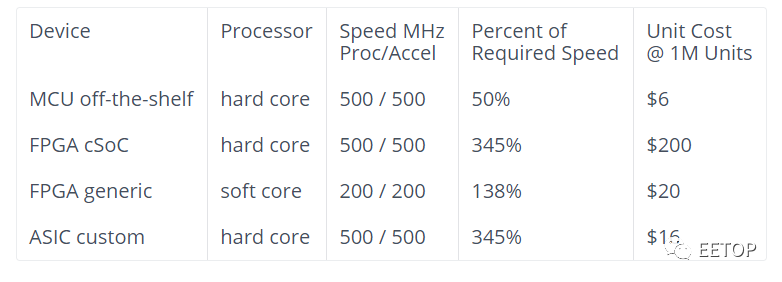

你可以从下面的表格中看到这些数字是如何计算出来的,其中带有处理器软核的通用FPGA使用成本和复杂度更低的解决方案提供了足够好的性能(场景说明了一个应用,MCU必须被带有硬件加速器的DSA取代,该硬件加速器可以将90%的工作从通用处理器上卸载,并以10倍的速度执行)。

在低端(16位处理器,<100MHz),市场正在推动MCU、FPGA和其他板卡芯片的集成,以提高性能、功耗和成本。FPGA供应商在十年前就以cSoC来应对,虽然许多MCU实现了转型,但由于成本或系统不适合,其他许多MCU没有实现转型。这些剩余的MCU应用将因廉价的FPGA和RISC-V软核提供的新自由度而失去市场份额。

结论

在不久的将来,采用RISC-V内核的FPGA将成为下一代基于物联网边缘设备的创新平台,这是不可避免的。这些设计将从基于FPGA的原型验证和仿真开始。在这个过程中,很多系统会发现,基于FPGA的RISC-V的方案可以提供足够好的性能、功率和成本。我认为所有FPGA供应商都提供RSIC-V软核产品只是时间问题。这对系统客户以及FPGA厂商本身都会有好处。

而在我们谈论变化的同时,我们也很有可能看到基于RISC-V的创新也会大量使用云计算。与传统的仿真器相比,基于FPGA的仿真器可以节省很大的成本,但并不是每个人都能利用这个优势,因为它很复杂。在云端拥有一个简化的IoT设备仿真能力--就像AWS-FPGA如何简化数据中心加速一样--可以真正改变游戏规则。

来源:EETOP综合编译

点击阅读原文进入eetop微信后台,输入“芯片”获取!

部分文章标题: