集成电路ESD电路设计与工程应用

《集成电路ESD电路设计与工程应用》

引言:

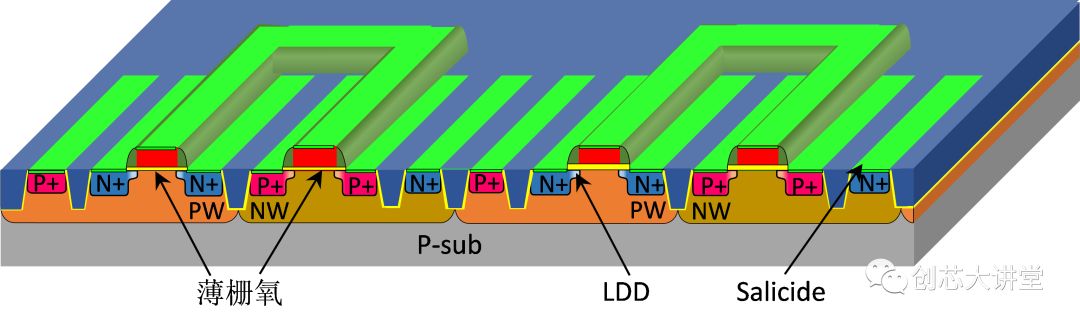

随着半导体工艺特征尺寸的不断按比例缩小,为了不断改善器件的性能,许多先进工艺技术被开发出来,并应用于实际集成电路工艺制程中,例如LDD工艺技术和Salicide工艺技术,使得深亚微米和纳米集成电路对静电放电的防护能力不断下降,但外界环境中所产生的静电并未减少,所以集成电路的ESD损伤变非常严重。如图1所示,是先进工艺技术平台器件结构的示意图。

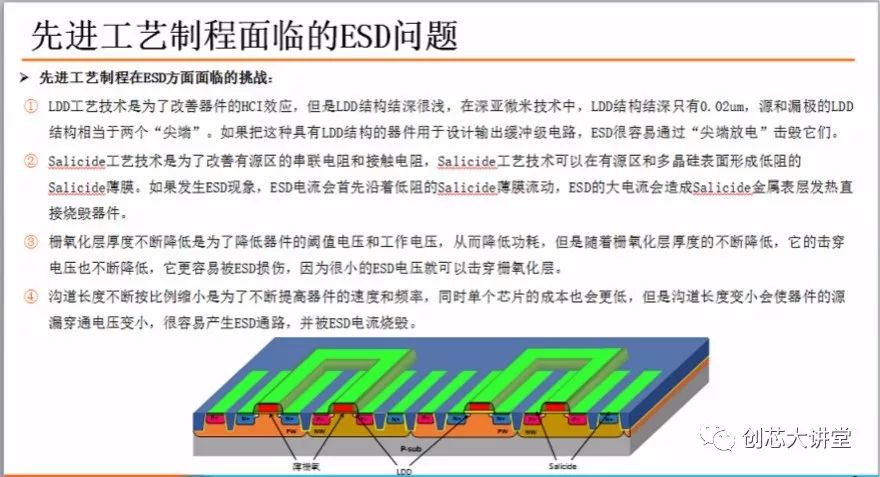

为什么使用先进制程工艺技术会减小CMOS集成电路对静电放电的防护能力呢?

第一为了克服热载流子注入(HCI)效应而发展出漏端轻掺杂(LDD)工艺与结构,LDD结构可以降低器件漏端在沟道下的峰值电场强度,从而改善因器件长时间使用带来的载流子注入造成器件的I-V特性漂移的问题。但是LDD结构结深很浅,在深亚微米技术中,LDD结构结深只有0.02um,源和漏端的LDD结构相当于两个“尖端”。如果把这种具有LDD结构的器件用于设计输出缓冲级电路,ESD(Electro Static Discharge - ESD)很容易通过“尖端放电”击毁它们。

第二为了降低CMOS器件漏端、源端和栅端的接触电阻和薄层方块电阻,而发展出的精神硅化物Polycide和Silicide工艺;在更先进的工艺中把Silicide与Polycide一起制造,称为Salicide工艺,它可以有效的提高集成电路的运算速度。Salicide工艺技术可以在有源区和多晶硅表面形成低阻的Salicide薄膜。如果发生ESD现象,ESD电流会首先沿着低阻的Salicide薄膜流动,ESD的大电流会造成Salicide金属表层发热直接烧毁器件。

第三为了降低器件的阈值电压和工作电压,从而降低功耗和提升集成电路的运算速度,栅氧化层越来越薄。但是随着栅氧化层厚度的不断降低,它的击穿电压也不断降低,它更容易被ESD损伤,因为很小的ESD电压就可以击穿栅氧化层。

第四为了不断提高器件的速度和频率,沟道长度不断按比例缩小,同时单个芯片的成本也会更低,但是沟道长度变小会使器件的源漏穿通电压变小,很容易产生ESD通路,并被ESD电流烧毁。

图1先进工艺技术平台器件结构的示意图

为了更好的理解先进工艺对集成电路的ESD鲁棒性的影响,以沟道宽度为200μm的输出级NMOS器件为例,用1μm的工艺时它的ESD可能超过2KV HBM;但是如果用0.8μm工艺时,这个输出级NMOS器件的ESD却在1KV HBM左右,因为在0.8μm工艺时该输出级NMOS器件已经包括了LDD结构;如果用0.35μm工艺,那么该输出级NMOS器件将包含LDD结构和Silicide源漏,其ESD仅几百伏HBM。可见当器件的尺寸不变,利用先进制程制造的器件它的ESD防护能力也会大幅地降低。在先进制程技术增大器件的尺寸也不能很好的使其ESD能力改善。相对于利用比较落后的制程制造的器件,先进制程制造的器件的ESD保护能力不但没有提升,反而严重地下降,几乎所有的先进工艺的CMOS集成电路产品都面临了这个难题。另外CMOS集成电路的静电放电防护能力的标准并不会因为利用了先进工艺而降低集成电路的静电放电防护能力的标准。

制作ESD培训课程内容:

为了让更多从事集成电路相关工作的工程师了解集成电路ESD电路设计的内容,EETOP了解到温德通老师会在2018年11月9日有个职业空窗期,所以邀请温老师录制了《集成电路ESD电路设计与工程应用》系列培训课程。

ESD培训课程主要内容:

通过介绍ESD的概念、产生静电的方式、ESD的模式和测试(HBM、MM和CDM)、ESD电路设计窗口、ESD器件物理分析、ESD基本保护电路和全芯片ESD电路设计等,让从事集成电路相关工作的工程师快速理解ESD的原理、ESD电路设计要求和ESD分析方法,从而提高自己解决ESD相关问题的能力。

免费预览课程大纲

长按二维码参与学习

共20讲 :

第一讲的主要内容:(ESD概述)

1.介绍静电的概念、特点和产生静电的方式。解释了ESD静电会产生瞬间的强大的尖峰脉冲电流损伤物体。

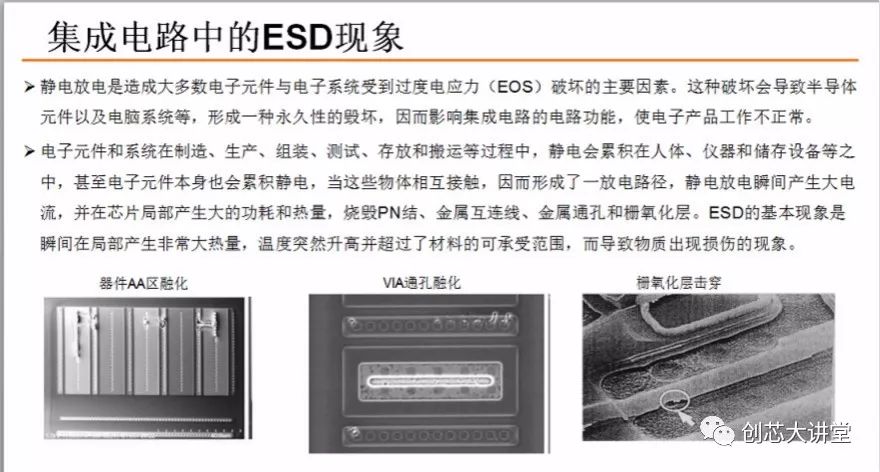

2.介绍集成电路中的ESD现象,例如导致器件AA区融化、VIA通孔融化和击穿栅氧化层等。

3.介绍先进工艺制程面临的ESD问题,LDD结构尖端放电、ESD的大电流会造成Salicide金属融化、栅氧化层厚度变小易被ESD击穿等。

第二讲的主要内容:(ESD放电模型)

1.介绍人体模型(HBM Human-Body-Model),人体如同一个电容,会储存静电,带电人体接触芯片,会造成芯片被ESD损伤。还介绍HBM的等电路和业界标准。

2.介绍机器模型(MM Machine-Model) ,机器是金属材料,也会储存静电,带电机器接触芯片,会造成芯片被ESD损伤。还介绍MM的等电路和业界标准。

3.介绍器件充电模型(CDM Charged-Device-Model) ,封装好的芯片内部也会累积大量静电,带静电的芯片直接接地会造成芯片被ESD损伤。还介绍CDM的业界标准。

第三讲的主要内容:(ESD测试)

1.介绍电源管脚之间的ESD测试,静电放电可能出现在芯片的电源管脚之间。对不同电源管脚之间、不同接地管脚之间、电源管脚与接地管脚之间进行ESD测试。任何外部带静电的人或者机器所带的静电电荷有可能是正的也有可能是负的,所以要对芯片的每一组电源管脚进行正负极性的两种ESD测试。

2.介绍IO管脚与相应电源管脚之间的ESD测试,静电放电可能出现在芯片的IO管脚到电源或者接地管脚之间,所以需要对IO管脚与相应电源管脚或者IO管脚与相应接地管脚进行ESD测试。任何外部带静电的人或者机器所带的静电电荷有可能是正的也有可能是负的,所以要对芯片的每一个IO管脚需要进行正负极性的两种ESD测试,同一个IO管脚有四种ESD测试组合。

3.介绍IO管脚与相应IO管脚之间的ESD测试,在模拟电路内常有差动放大器的输入级有两个用来消除输入端直流电压偏移的输入管脚,这两个输入管脚是ESD特别薄弱的位置,需要另外单独做静电放电测试,以验证这两个输入脚所连接的差动输入级会不会被静电放电所破坏。任何外部带静电的人或者机器所带的静电电荷有可能是正的也有可能是负的,所以要对芯片的差动输入级进行正负极性的两种ESD测试。

4.介绍CDM的ESD测试,对芯片VSS管脚进行静电充电,把静电电荷充入该芯片的衬底之中,冲电的过程中除了充电管脚,其它管脚都是悬空的,所以所有的静电电荷会储存在其衬底之中,为避免静电充电过程造成芯片损伤,静电充电电路必须串联一高阻电阻进行限流,电阻的阻值大于10MΩ。目前几乎所有的芯片都是P型衬底,所以这里只讨论P型衬底的芯片,芯片的接地管脚是直接连接到其衬底,因此对芯片的接地管脚进行静电充电。完成静电充电后,再对该芯片的其它所有管脚(包括输入,输出,输入/输出,以及VDD管脚)分别接地进行静电放电,从而完成CDM的静电放电测试。芯片内部所储存的静电有可能是正的,也有可能是负的,所以要对芯片的每一个管脚进行正负极性的两种ESD测试。

第四讲的主要内容:(额外的工艺在ESD方面的应用)

1.介绍改善先进工艺制程ESD问题的方式,利用SAB工艺或者ESD IMP工艺改善器件的ESD性能。

2.介绍Salicide工艺的优缺点,优点是在MOS管的栅和源漏有源区表面形成低阻的Salicide,降低栅极的电阻和源漏的等效电阻Rd及Rs,从而提高MOS管的速度,达到改善整个芯片的目的。缺点是ESD电流会通过漏极表面低阻的Salicide流动,并产生高温烧毁器件。

3.介绍SAB工艺,通过SAB工艺可以形成Non-Salicide的区域,从而改善Salicide工艺在ESD中的问题。

4.介绍LDD结构的优缺点,优点是改善HCI效应。缺点是LDD的结深大概只有0.02μm,它们相当于在漏极与源极的两端形成了两个"尖端",如果把这种具有LDD结构的器件用于输出级,NMOS很容易被ESD通过"尖端放电"破坏。

5.介绍ESD IMP工艺,有两种类型的ESD IMP工艺,一种是N型ESD IMP工艺,一种是P型ESD IMP工艺。

6.介绍ESD IMP的作用,ESD IMP可以降低PN结的击穿电压。

第五讲的主要内容:(ESD保护电路的设计窗口)

1.介绍传输线脉冲技术(TLP)分析方法,业界通常利用TLP机台分析器件的ESD TLP IV,从而了解器件的ESD性能。

2.介绍ESD器件的二次击穿电压,二次击穿就是热击穿,器件从热平衡状态变为非热平衡状态,当器件进入热击穿状态后会因为发热而被烧毁。

3.介绍ESD保护电路设计窗口,如何利用芯片电压VDD、栅氧化层击穿电压和器件的热击穿电压指导ESD设计。

4.介绍ESD保护电路设计的概念,(芯片正常工作时,ESD保护电路是工作在截止区。)等

第六讲的主要内容:(电阻和二极管)

1.介绍电阻的物理分析,电阻主要是起限流作用,用于输入端口,如何理解电阻的电流饱和理论以及雪崩击穿。

2.介绍二极管的物理分析,把二极管用在输入\输出管脚,做ESD保护电路。

3.介绍二极管电流集边效应和改善二极管电流集边效应的方法。

4.介绍二极管的有源区边角形成Salicide下冲尖端问题,以及改善方法。

5.介绍二极管电路的实例应用。

第七讲的主要内容:(NMOS)

1.介绍雪崩倍増效应的原理。

2.介绍NMOS的有源区边角形成Salicide下冲尖端问题,以及改善方法。

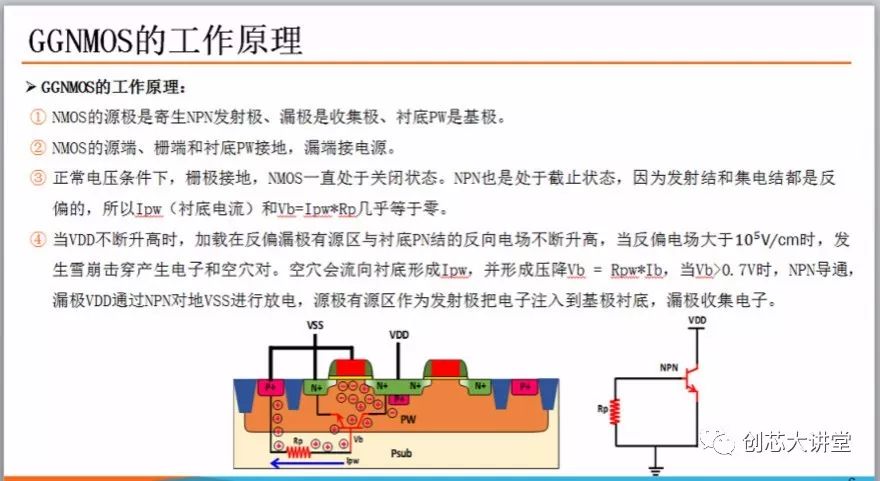

3.介绍GGNMOS的工作原理,它是利用寄生的BJT NPN进行静电放电。

4.介绍GGNMOS的TLP IV曲线,如何去理解它的物理机理。

5.介绍改善ESD NMOS寄生NPN的ESD鲁棒性的方法,ESD NMOS设计规则的物理机理。

6.介绍ESD NMOS寄生NPN非均匀导通的问题,以及改善方法。

7.介绍如何利用ESD NMOS寄生N-diode做ESD设计。

8.介绍ESD NMOS的实例应用。

第八讲的主要内容:(PMOS)

1.介绍GPPMOS的工作原理,它是利用寄生的P-diode和BJT PNP进行静电放电。

2.介绍GPPMOS的TLP IV曲线,如何去理解它的物理机理。

3.介绍提高ESD PMOS的ESD保护能力的方法,ESD PMOS设计规则的物理机理。

4.寄生ESD PMOS的应用实例

第九讲的主要内容:(SCR结构)

1.介绍SCR的基本结构,SCR是由PNP和NPN通过耦合阱电阻形成的。

2.介绍SCR的工作原理,SCR具有两种不同的状态:

3.介绍SCR TLP IV曲线,如何去理解它的物理机理。

4.介绍SCR闩锁效应,当电源电源VDD大于SCR的自持电压时,会发生闩锁效应。

5.介绍改善SCR的ESD鲁棒性的方法。

6.介绍SCR应用实例

第十讲的主要内容:(二极管电路)

1.介绍典型的二极管ESD保护电路,用作输入\输出ESD保护电路。

2.介绍二极管ESD保护电路工作原理,ESD静电放电路径。

3.介绍二极管电源钳位保护电路,地与地之间或者电压与电压之间的ESD保护电路。

4.介绍二极管电源钳位保护电路的工作原理,ESD静电放电路径。

第十一讲的主要内容:(NMOS和PMOS保护电路)

1.介绍NMOS和PMOS ESD保护电路,用作输入\输出ESD保护电路。

2.介绍GGNMOS和GPPMOS ESD保护电路的连接方式和工作原理。

第十二讲的主要内容:(RC栅触发NMOS保护电路)

1.介绍RC栅触发NMOS保护电路的工作原理,它是由ESD检测电路和ESD NMOS组成,通过ESD NMOS寄生BJT NPN放电。

2.介绍改善ESD NMOS寄生NPN非均匀导通的原理。

3.介绍通过增大NMOS栅电压Vg减小源漏穿通电压的原理。

4.介绍RC栅触发NMOS保护电路应用实例。

第十三讲的主要内容:(栅耦合NMOS保护电路)

1.介绍栅耦合NMOS ESD保护电路的工作原理,通过寄生的BJT NPN进行静电放电。

2.介绍改善ESD NMOS寄生NPN非均匀导通的原理。

第十四讲的主要内容:(衬底触发NMOS保护电路)

1.介绍衬底触发NMOS ESD保护电路的工作原理,通过衬底电流触发寄生的BJT NPN进行静电放电。

2.介绍提高衬底触发NMOS保护电路ESD鲁棒性的方法。

第十五讲的主要内容:(SCR保护电路)

1.介绍改善SCR的ESD鲁棒性的方法。

2.介绍SCR的TLP IV曲线,如何去理解它的物理机理。

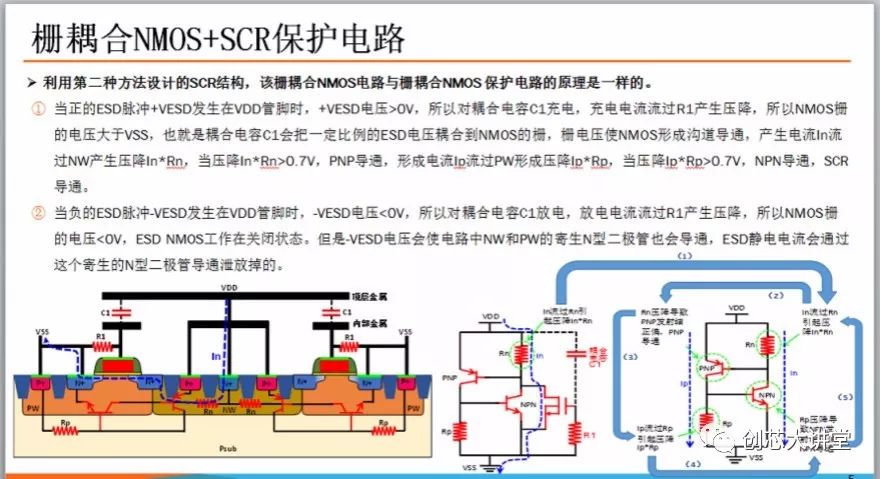

3.介绍栅耦合NMOS+SCR保护电路的工作原理和物理机理。

4.介绍栅耦合NMOS+SCR的TLP IV曲线。

第十六讲的主要内容:(电源管脚之间的ESD防护)

1.介绍常规的双电压电路的特点。

2.介绍电源管脚之间的ESD防护电路的设计要求。

3.介绍电源管脚之间的ESD防护的工作原理。

第十七讲的主要内容:(IO管脚与相应电源管脚之间的ESD防护)

1.介绍IO管脚与相应电源管脚之间的ESD防护的原则。

2.介绍IO管脚与相应电源管脚之间的ESD防护的电路。

3.介绍IO管脚与相应电源管脚之间的ESD防护的原理。

第十八讲的主要内容:(IO管脚与相应IO管脚之间的ESD防护)

1.介绍IO管脚与相应IO管脚之间的ESD防护的原理。

2.介绍IO管脚与相应IO管脚之间的ESD防护电路。

3.介绍IO管脚与相应IO管脚之间的ESD防护的工作原理。

第十九讲的主要内容:(CDM ESD防护)

1.介绍CDM放电造成输入级电路的栅极被击穿。

2.介绍HBM ESD保护电路无法改善CDM静电放电。

3.介绍CDM的ESD防护电路,通过二极管保护输入栅极。

第二十讲的主要内容:(全芯片ESD保护设计)

1.介绍全芯片ESD保护设计,必须保护电源之间、IO和CDM保护。

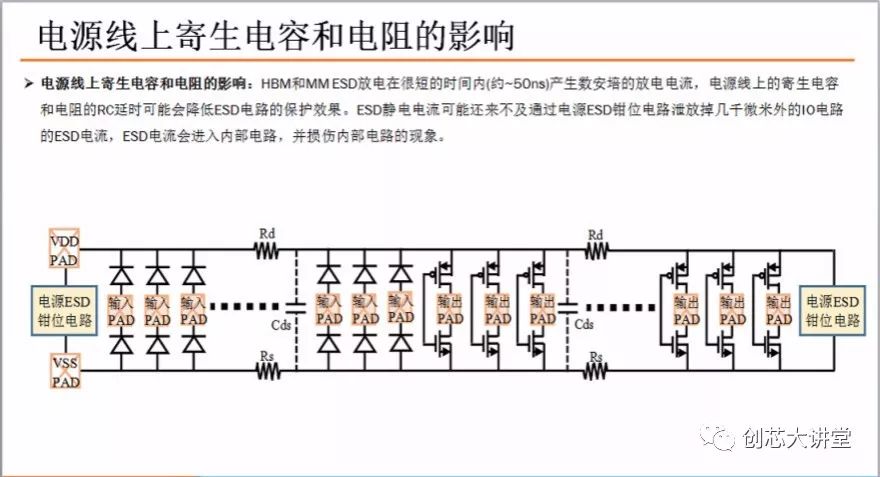

2.介绍电源线上寄生电容和电阻的对ESD保护电路的影响。

3.介绍改善电源线上寄生电容和电阻的影响的方法。

4.介绍电源线上寄生电容和电阻的影响实例。

适合人群:

工艺研发工程师(TD)

版图设计工程师

模拟电路设计工程师

ESD电路设计工程师

芯片失效分析工程师

讲师简介:

温德通,资深芯片设计工程师。畅销书《集成电路制造工艺与工程应用》的作者。毕业于西安电子科技大学微电子学院,曾供职于中芯国际集成电路制造(上海)有限公司,负责工艺制程整合方面的工作;后加入晶门科技(深圳)有限公司,负责集成电路工艺制程、器件、闩锁效应和ESD电路设计等方面的工作;2018年11月离开晶门科技。

版权申明:2018年11月10日温德通先生已经把视频内容授权EETOP全权负责

长按二维码或点击阅读原文参与学习

关于创芯大讲堂

创芯大讲堂是EETOP旗下在线教育平台,后续会推出一系列微电子行业在线课程。

EETOP是国内知名的半导体、微电子工程师社区。创芯大讲堂推出的课程会是围绕半导体集成电路全产业链,将会包括:从设计到制造,从前端到后端,从模拟、数字到混合集成电路等。希望通过我们的努力能为中国集成电路发展、人才培养等做出微薄之力。

作为一个大型电子工程师社区,当然我们也不仅仅只关注集成电路,后续我们也会推出硬件设计、嵌入式设计相关的各种课程。

>>点击阅读原文,查看更多课程!