集成电路制造工艺从入门到精通

如果你从事IC设计,学一些集成电路工艺及制造,对设计的提高应该很有帮助。如果你从事集成电路工艺及制造那么本文应该更加适合与你。

今天为大家推荐一门线上课程,可以在短时间内了解集成电路工艺以及工程应用,而对于已经有一定经验的行业从业者,则可以快速提高自己的专业水平。

本课程是基于《集成电路制造工艺与工程应用》一书内容,为了使视频更通俗易懂,还会加入作者编写书时的思路和想法,同时也会补充部分原书没有的内容。

创芯大讲堂今日推荐:温德通《集成电路制造工艺与工程应用》

(注:本课程可以独立于本书)

相关书籍《集成电路制造工艺与工程应用》可在京东商城上进行购买

(注:本课程可以独立与本书学习)

适用人群

工艺制程整合工程师 /工艺研发工程师 /工艺可靠性工程师/ 工艺客户工程师/ 器件设计工程师/ 版图设计工程师

集成电路制造工艺培训课程内容介绍:

介绍集成电路工艺技术逐步发展到CMOS的过程,也介绍了从CMOS衍生出来的特殊工艺(BCD、BiCMOS和HV-CMOS)的特点和应用,同时还包含储存工艺技术(DRAM工艺技术、Flash EEPROM工艺技术、EEPROM工艺技术)和储存器(OTP储存器、SRAM 储存器和ROM 储存器)的内容,还介绍了业界的先进工艺技术(应变硅技术、HKMG技术、SOI技术和FinFET技术)出现的原因,物理原理和工艺制程的实现过程。最后介绍典型工艺模块(STI、LOCOS、硬掩膜版、HCI效应和LDD IMP)的特点和物理机理。

本系列培训课程共分十六节内容

第一讲:崛起的CMOS工艺技术

第二讲:特殊工艺技术和储存器

第三讲:MOS晶体管的发展和面临的挑战

第四讲:应变硅技术物理机理

第五讲:应变硅技术的应用

第六讲:HKMG技术的原理

第七讲:HKMG技术的应用

第八讲:SOS技术和SOI技术

第九讲:PD-SOI和FD-SOI技术

第十讲:FinFET和UTB-SOI工艺技术

第十一讲:隔离技术-PN结隔离技术

第十二讲:隔离技术-LOCOS(硅局部氧化)隔离技术

第十三讲:隔离技术-STI(浅沟槽)隔离技术

第十四讲:硬掩膜版技术

第十五讲:漏致势垒降低效应和沟道离子注入

第十六讲:热载流子注入效应与轻掺杂漏工艺技术

希望通过学习本培训课程让工程师快速掌握以下内容:

1. 理解工艺技术的发展过程,CMOS崛起和占据主导地位的原因。

2. 掌握特殊工艺(BCD、BiCMOS和HV-CMOS)的特点和应用。

3. 了解储存工艺技术(DRAM工艺技术、Flash EEPROM工艺技术、EEPROM工艺技术)和储存器(OTP储存器、SRAM 储存器和ROM 储存器)的特点。

4. 熟悉先进的工艺技术(应变硅技术、HKMG技术、SOI技术和FinFET技术)出现的原因、物理原理和工艺实现过程。

5. 掌握典型工艺模块(STI、LOCOS、硬掩膜版、HCI效应和LDD IMP)的特点和物理机理。

希望通过本课程帮助从事集成电路相关工作的工程师构建一个完整的集成电路工艺知识体系,提高工程师利用工艺知识分析设计规则、芯片内部寄生效应、器件二级效应、芯片可靠性等的专业能力。

第一讲的主要内容:(崛起的CMOS工艺技术)

介绍早期双极型工艺技术,它是最早出现的集成电路制程技术,它功耗大,不能满足大规模集成电路的要求。

介绍早期NMOS和PMOS工艺技术,它的特点是集成度高,但是速度低。

NMOS和PMOS工艺技术的铝栅工艺存在套刻不齐问题。介绍多晶硅栅工艺技术的优势和特点。

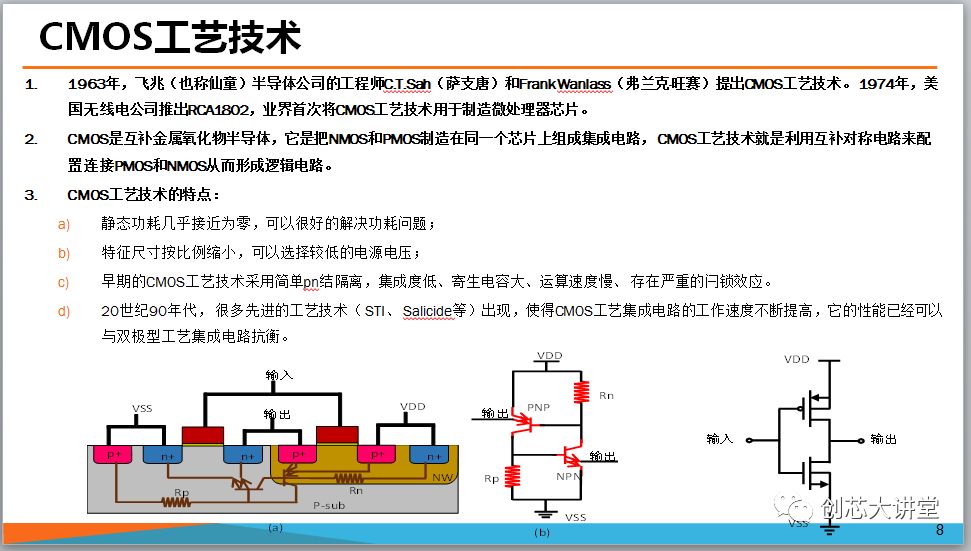

介绍CMOS工艺技术,集成度高,功耗低。随着技术发展,它是大规模集成电路的必然趋势。

介绍CMOS闩锁效应的物理机理,通过CMOS中寄生的NPN和PNP形成的等效电路的工作原理介绍闩锁效应的物理机理。

介绍早期SOS CMOS集成电路,制造在蓝宝石SOS上的集成电路可以防止闩锁效应。

第二讲的主要内容:(特殊工艺技术和储存器)

介绍BiCOMS工艺技术,BiCMOS是把BJT和CMOS器件制造在同一芯片上,综合BJT的高跨导、强驱动能力和CMOS器件的低功耗、高集成度的优点。

介绍BCD工艺技术,BCD是把BJT,CMOS和DMOS器件同时制作在同一芯片上,除了综合了BJT的高跨导和强负载驱动能力,以及CMOS的高集成度和低功耗的优点,它还综合了高压DMOS器件的高压大电流驱动能力。

介绍HV - CMOS工艺技术,HV-CMOS工艺技是把CMOS和DDDMOS/FDMOS制造在同一个芯片上,它是传统CMOS工艺制程技术向高压的延伸,可以支持高压信号输出。

介绍DRAM工艺技术,DRAM为动态随机存储器,它的一个单元仅需一个晶体管,密度高,DRAM的信息以电荷的形式存储在电容上。

介绍Flash EEPROM工艺技术,Flash EEPROM为闪存电可擦除可编程只读存储器,很多FLASH使用雪崩热电子注入方式来编程,通过隧穿原理(F-Ntunneling)电擦除存储的内容,它只能实现大块存储单元同时擦除,它没有字选择线,一个存储单元只有一个晶体管。

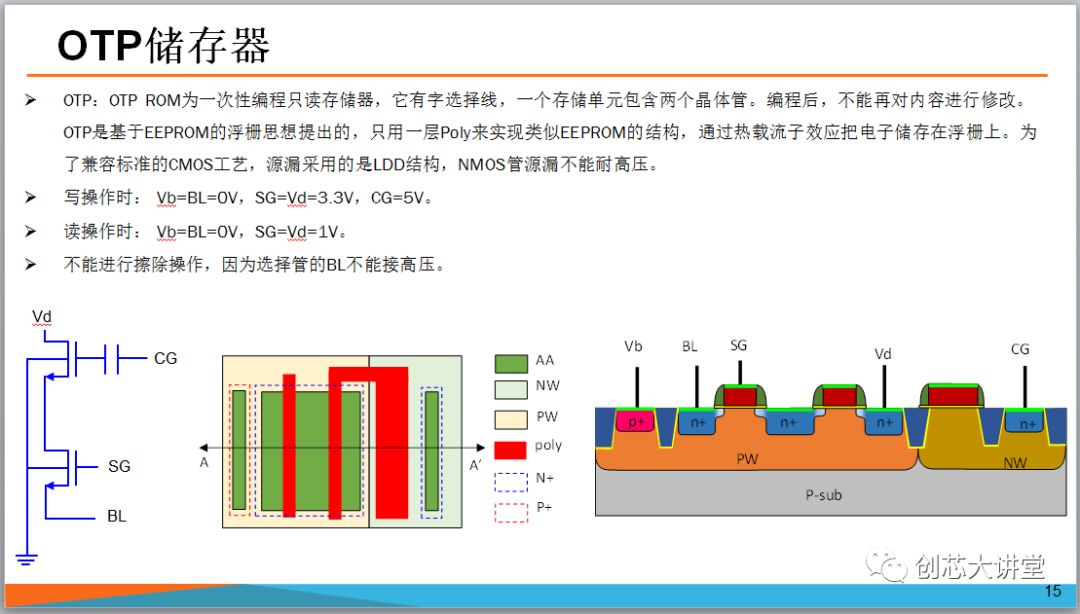

介绍EEPROM工艺技术,EEPROM为电可擦除可编程只读存储器,它编程和擦除的原理都是F-N tunneling, 它能实现对单个存储单元擦除,它有字选择线,一个存储单元包含两个晶体管。

介绍OTP储存器、SRAM 储存器和ROM 储存器等。

第三讲的主要内容:(MOS晶体管的发展和面临的挑战)

介绍铝栅和多晶硅栅(Polysilicon),MOS最初的栅极材料是铝,但是铝栅存在套刻不齐问题会影响集成度,后期利用多晶硅栅代替铝栅。

介绍栅极金属硅化物(Polycide),多晶硅栅的缺点是电阻率高,虽然对MOS器件的直流特性是没有影响的,但是它严重影响了MOS器件的高频特性,利用多晶硅和金属硅化物是双层材料代替多晶硅栅,降低栅极的电阻。

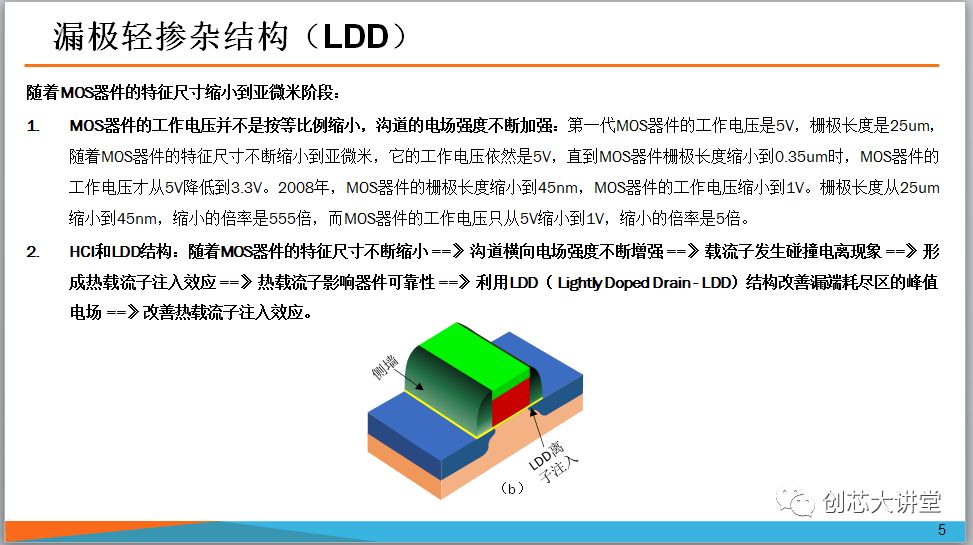

介绍漏极轻掺杂(LDD)结构,随着MOS器件的特征尺寸缩小到亚微米,沟道电场强度不断加强,出现严重的热载流子注入效应,为了改善这个问题引入LDD IMP工艺技术。

介绍自对准金属硅化物(Salicide),MOS器件的特征尺寸缩小到深亚微米以下,接触孔的尺寸不断缩小,导致接触电阻升高了(200ohm以上),利用金属硅化物(silicide)降低有源区的电阻和接触电阻。

介绍沟道离子注入和口袋离子注入,MOS器件的特征尺寸缩小到深亚微米,源漏之间的耗尽区相互靠近,导致DIBL,形成漏电流,为了改善这个问题,利用沟道离子注入和晕环/ 口袋离子注入增加沟道区域的离子浓度从而减小源漏与衬底之间的耗尽区宽度,改善漏电流。

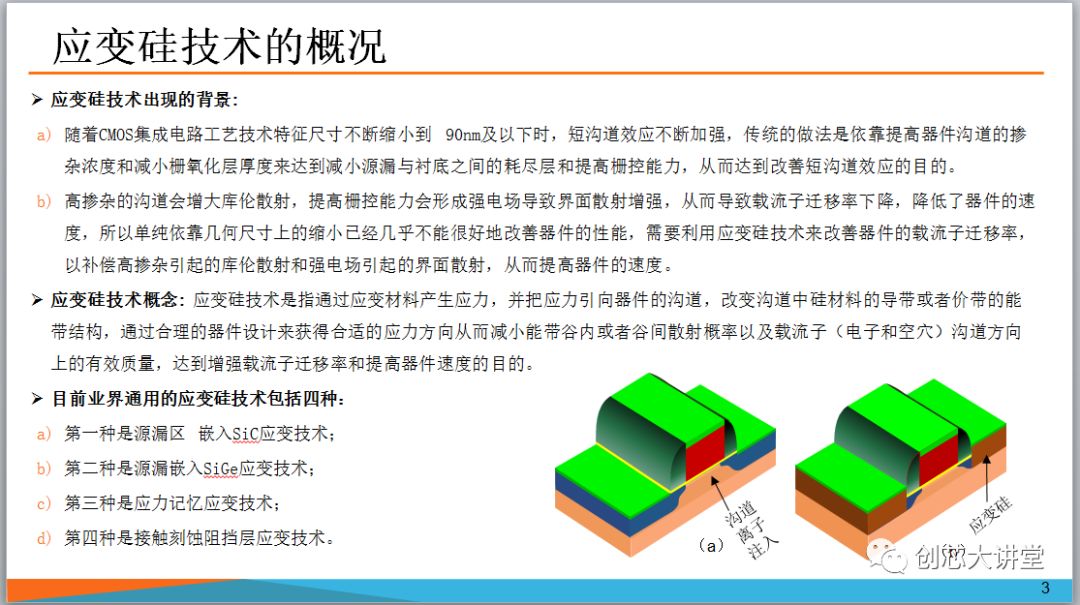

介绍应变硅和提高源漏(RSD),MOS器件的特征尺寸不断缩小到90nm及以下,为了抑制短沟道效应,从而提高沟道掺杂浓度,但是高掺杂的沟道会增大库伦散射,导致器件的速度降低。为了改善这些问题,利用RSD技术在源漏区嵌入应变材料,改善器件的速度。

介绍高K介质-金属栅(HKMG),MOS器件的特征尺寸不断缩小45nm及以下,栅氧化层的厚度减小到2nm以下,电子以波的形式越过栅氧化层,形成栅极泄漏电流。为了改善这个问题,引入HKMG技术。

介绍全耗尽 – FD-SOI(Fully DepletionFD-SOI),MOS器件的特征尺寸不断缩小22nm及以下,仅仅依靠提高沟道的掺杂浓度和降低源漏结深已不能很好的改善短沟道效应。

利用FD-SOI( Fully Depleted SOI 全耗尽)晶体管改善短沟道效应。

介绍鳍型场效应晶体管 –FinFET,MOS器件的特征尺寸不断缩小22nm及以下,采用三维立体型结构的体FinFET和SOI FinFET代替平面结构的MOSFET作为集成电路的晶体管改善短沟道效应。

第四讲的主要内容:(应变硅技术物理机理)

介绍应变硅技术的概况,包括应变硅技术出现的背景和应变硅技术概念。

介绍应变硅技术的发展,20世纪80年代,应变硅技术开始出现。2002年,Intel公司将应变硅技术应用于90nm CMOS工艺技术。

介绍电子电导有效质量,在硅衬底材料中,硅具有多能谷的能带结构,其导带由六个简并能谷构成,这六个简并能谷分别有六个导带极值。

介绍单轴压应力使导带分裂,对硅材料施加单轴压应力可以使导带底的六个简并能谷发生分裂,原有的六重简并的能谷分裂为两组:一组是能量较高的四重简并能谷即次能谷(Δ4);一组是能量较低的二重简并能谷即主能谷(Δ2)。

介绍单轴压应力改变声子散射几率,当硅受到单轴压应力时能谷分裂,Δ2能谷能量下降,而Δ4能谷能量上升,它们存在较大的能量差,从而减小能谷之间的声子散射几率。

介绍单轴张应力使导带分裂,对硅材料施加单轴张应力可以使导带底的六个简并能谷发生分裂,原有的六重简并的能谷分裂为两组:一组是能量较高的二重简并能谷即次能谷(Δ2);一组是能量较低的四重简并能谷即主能谷(Δ4)。

介绍单轴张应力改变声子散射几率,当硅受到张应力时能谷分裂,Δ2能谷能量上升,而Δ4能谷能量下降,它们存在较大的能量差,从而减小能谷之间的声子散射几率。

介绍单轴压应力使价带分裂,施加单轴压应力时,重空穴带和轻空穴带发生分裂,轻空穴带上升,重空穴带下降,空穴首先占据轻空穴带。施加单轴张应力时,轻空穴带下降,重空穴带上升,空穴首先占据重空穴带。

(可试看)

第五讲的主要内容:(应变硅技术的应用)

介绍源漏区嵌入SiC应变技术概述,源漏区嵌入SiC应变技术被广泛用于提高NMOS的速度,利用硅和碳晶格常数不同,从而对沟道产生应力,改变硅导带能谷的简并,降低电子的电导有效质量和散射几率。

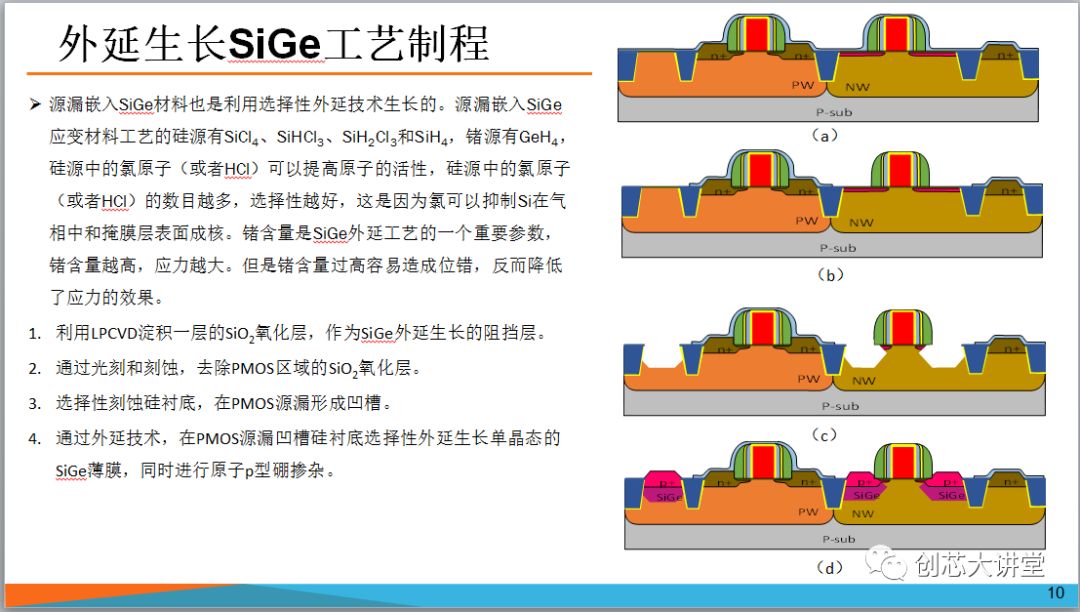

介绍选择外延技术,选择外延技术是利用外延生长的基本原理,以及硅在绝缘体上很难核化成膜的特性,在硅表面的特定区域生长外延层而其他区域不生长的技术。

介绍SiC材料外延生长工艺,通过CVD淀积和湿法刻蚀技术,进行多次淀积和多次刻蚀的方式来外延生长SiC应变材料。

介绍外延生长SiC工艺制程。

介绍源漏区嵌入SiGe应变技术概述,源漏区嵌入SiGe应变技术被广泛用于提高PMOS的速度,利用锗和硅晶格常数不同,从而对沟道产生单轴压应力,改变硅价带的能带结构,降低空穴的电导有效质量。

介绍外延生长SiGe工艺制程。

介绍应力记忆技术概述,包括应力记忆技术的概念和应力记忆技术遇到的问题。

介绍影响应力记忆技术的因素。

介绍应力记忆技术工艺制程。

介绍接触刻蚀阻挡层应变技术概述,接触孔刻蚀阻挡层应变技术的概念,NMOS单轴张应力CESL,PMOS单轴压应力CESL。

介绍淀积不同应力氮化硅薄膜的原理,接触孔刻蚀阻挡层SiON,张应力的Si3N4薄膜(NMOS),压应力的Si3N4薄膜(PMOS)。

介绍接触刻蚀阻挡层工艺制程。

第六讲的主要内容:(HKMG技术的原理)

介绍多晶硅栅极叠层结构的发展。

介绍Poly/SiON栅极叠层结构,纯二氧化硅栅介质层的漏电问题,解决栅极漏电的方案,SiON具有三方面的优点。

介绍栅氧化层的氮化工艺,炉管热处理氮化工艺,等离子氮化工艺。

介绍HKMG工艺技术出现的背景,45nm工艺面临的问题,HKMG工艺技术。

介绍衬底量子效应,对于MOS器件的尺寸减少到90nm以下,栅氧化层厚度也不断减小,栅氧化层的厚度小于2nm,载流子的物理特性不再遵从经典理论,其量子效应会变得非常显著,在栅电极下产生一个额外的串联电容。

介绍多晶硅栅耗尽效应,当器件反向偏置时,栅与衬底之间存在压差,它们之间存在电场,使多晶硅靠近氧化层界面附近的能带发生弯曲,并且电荷耗尽,从而形成多晶栅耗尽区。该耗尽区会在多晶硅栅与栅氧化层之间产生一个额外的串联电容。

介绍等效栅氧化层厚度,业界通常利用低频和高频的电容电压(C-V)特性曲线提取MOS器件栅介质的电学厚度。MOS器件的栅介质的电学厚度是栅极电荷质心与衬底电荷质心的距离。

介绍栅极泄漏电流,当SiON的厚度小于2nm时,它不再是理想的绝缘体,栅极与衬底之间的电子将出现量子化,它表现为波动性,载流子以波的形式绕过氧化层的势垒形成量子隧穿效应,在栅极与衬底之间形成栅极泄漏电流。

介绍高介电常数介质层。

第七讲的主要内容:(HKMG技术的应用)

介绍HfO2和HfSiON取代SiON作为栅氧化层的优点和引起的问题。

介绍解决不兼容的方法,半导体业界利用金属代替多晶硅作为器件栅极材料,在高K介质材料与衬底之间的界面插入一层极薄的SiON薄膜。

介绍先栅工艺遇到的问题,先栅工艺需要经历源漏离子注入高温退火激活工艺,对于大多数金属栅极材料,在经过高温退火后,功函数都会漂移到带隙中间,从而失去调节阈值电压的作用。

介绍淀积覆盖层的工艺,是原子层淀积(Atomic Layer Deposition,ALD)或物理气相淀积技术。

介绍高K介质材料面临的问题,解决方法和淀积HfSiON的方法。

介绍先栅工艺技术工艺制程,金属嵌入栅极工艺技术与传统的Poly/SiON工艺技术流程类似,只是多了在高K介质材料与多晶硅栅嵌入“覆盖层”的工艺步骤。

介绍后栅工艺技术。

介绍后栅工艺技术的优势,高K介质层和栅极金属材料是在高温热退火后形成的,性能要比后栅工艺的好。

介绍后栅工艺工艺制程。

介绍HKMG工艺技术存在的问题,虽然HKMG利用金属栅极和高K栅介质层解决了多晶硅耗尽问题和栅极漏电问题,但是它也在硅衬底和高K栅介质层引入了SiON界面层,SiON界面层的削弱了高K栅介质层对先进工艺的中栅极电容的贡献。另外,衬底沟道量子化的问题也会一直存在,在技术上也没办法改善它。

第八讲的主要内容:(SOS技术和SOI技术)

介绍SOS技术的概念和优点。

介绍SOS技术改善闩锁效应,SOS工艺集成电路对于这些宇宙粒子具有非常强的免疫力,新产生的电荷仅仅存在于PW或者NW,并不会导致闩锁效应。

介绍SOS技术面临的问题,形成位错、孪晶和堆垛层错等缺陷,导热性差,在硅中形成压应力等。

介绍SOI技术的概念和制造SOI晶圆的技术。

介绍注氧隔离(SIMOX)技术,制备SOI晶圆流程,优缺点。

介绍键合(BESOI)技术,制备SOI晶圆流程,优缺点。

介绍智能切割(Smart-Cut)技术,制备SOI晶圆流程,优缺点。

第九讲的主要内容:(PD-SOI和FD-SOI技术)

介绍PD-SOI技术,体CMOS 和SOI CMOS比较。

介绍PD-SOI器件的翘曲效应,翘曲效应对器件和电路的影响。

介绍PD-SOI器件中寄生双极晶体管效应。

介绍PD-SOI器件栅感应漏极漏电流,影响栅感应漏极漏电流的因素。

介绍PD-SOI器件自加热效应,BOX不但提供了电学隔离,同时也造成了热隔离。因为SiO2的热导率约为硅的1/100,在SOI器件工作时,它自身产生的热量不易传递出去,形成热量堆积,导致自加热效应。

介绍PD-SOI器件体接触,为了抑制浮体效应,通常把体接到一个固定的电位上,从而控制体电势的变化,这种方法称为体接触。体接触的三种类型:T型栅、H型栅和BTS(Body-Tied-to-Source)型栅。

介绍FD-SOI技术的概况,优点和应用。

介绍FD-SOI技术背栅偏置,FD-SOI器件的氧化埋层的厚度很薄,只有20nm,它如同FD-SOI的第二个栅氧化层,衬底就是栅极。

介绍FD-SOI工艺流程。FD-SOI的工艺技术与MOSFET平面工艺制程是兼容的,FD-SOI的工艺技术的前段工艺制程采用了先栅HKMG和应变硅技术,后段依然是大马士革结构的铜制程。

第十讲的主要内容:(UTB-SOI和FinFET技术)

介绍FinFET的发展概况。

介绍FinFET和UTB-SOI的原理。

介绍SADP工艺技术。

介绍FinFET工艺技术流程。

(可试看)

第十一讲的主要内容:(隔离技术-PN结隔离技术)

介绍隔离技术,对半导体集成电路里的器件进行电性隔离,保证器件之间不产生相互干扰,并且每个器件的工作都是独立的,从而实现电路的功能。

介绍PN结隔离技术,是利用反偏的PN结漏电流非常小的原理,在集成电路中利用反偏的PN结实现器件间的相互电性隔离。

介绍双极型工艺技术的流程。

介绍穿通问题,相邻的两个NPN集电区之间会发生穿通问题,当它们相互逐渐靠近时,它们的耗尽层也相互逐渐靠近,势垒高度开始逐渐降低,电子就更容易越过这个势垒形成漏电流,那么相邻的NPN的集电极相互之间就会形成微弱的漏电流。

介绍改善PN结穿通的方法,增大P+保护环的宽度和提高P+保护环的掺杂浓度。

介绍寄生场效应管,当金属线在两个NPN之间P+保护环的上方横向跨过时,会形成寄生的场效应晶体管NMOS,相邻的两个NPN的集电区为该寄生NMOS的源和漏,金属线是栅。

第十二讲的主要内容:(隔离技术-LOCOS(硅局部氧化)隔离技术)

介绍LOCOS隔离技术的概念,是通过热氧化技术在器件有源区之间嵌入很厚的氧化物,从而形成器件之间的隔离,这层厚厚的氧化物称为场氧。

介绍LOCOS隔离技术工艺流程。

介绍鸟嘴效应,生长LOCOS场区氧化层的过程中需要消耗掉大约44%的硅,氧原子横向扩散与Si3N4掩膜下硅反应生产成氧化物,进入Si3N4掩膜下的氧化物会逐渐变薄形成鸟嘴的形状,所以横向延伸凹入有源区的现象被称为鸟嘴效应。

介绍白带效应,LOCOS场区氧化层是在高温的湿氧的环境下反应生长的,同时在Si/SiO2界面与Si反应形成Si3N4,这些Si3N4在有源区的边缘形成一条白带,这种效应称为白带效应。

介绍穿通问题,NMOS漏端与NW之间相互靠近时,它们之间的势垒高度开始减小,电子越过这个势垒形成漏电流,那么相邻的NMOS漏端与NW之间就会形成漏电流。

介绍寄生场效应管,当金属引线从NMOS的漏端与NW之间的PW上方跨过时,会形成寄生的场效应晶体管NMOS,NMOS漏端n型有源区是源端,NW是漏端,金属互连线是栅极。

介绍场区离子注入工艺流程。

第十三讲的主要内容:(隔离技术-STI(浅沟槽)隔离技术)

介绍STI隔离技术的概念,是利用各向异性的干法刻蚀技术在衬底隔离区域刻蚀出一定深度的浅沟槽,然后利用CVD淀积氧化物,从而形成器件之间的浅沟槽隔离。

介绍STI工艺技术的流程。

介绍穿通问题,NMOS的漏端与NW之间也会发生穿通问题,PMOS漏端与PW也会有穿通问题。

介绍寄生场效应管,当金属引线从NMOS的漏端与NW之间的PW上方跨过时,也会形成寄生的场效应晶体管NMOS。

介绍场区离子注入工艺流程。

介绍STI隔离技术存在的问题。

介绍LOD效应的概念,在利用STI隔离技术制造的CMOS集成电路中,STI沟槽中填充的是氧化硅,由于硅衬底和氧化硅的热力膨胀系数不同,导致硅会产生压应力挤压邻近MOS的有源区,引起器件的电参数发生变化,这种效应称为STI应力效应。

介绍改善LOD效应的方法,增大STI到有效器件栅极的距离。例如增加伪器件或者直接增大STI到器件栅极的距离。

第十四讲的主要内容:(硬掩膜版技术)

介绍湿法刻蚀和干法刻蚀。

介绍干法刻蚀的分类。

介绍硬掩膜版工艺技术。

介绍硬掩膜版工艺技术的应用。

第十五讲的主要内容:(漏致势垒降低效应和沟道离子注入)

介绍漏致势垒降低效应,随着漏极的电压不断升高时,漏端的电力线会沿着沟道向源极延伸,当源极和漏极的耗尽区层约等于器件的沟道长度时,源极与衬底之间的自建势垒高度开始降低,势垒高度降低导致漏极的电子很容易越过这个势垒到达源极从而形成漏电流。

介绍晕环离子注入,为了抑制短沟道器件的DIBL效应,在LDD结构中使用晕环(Halo,或者称口袋Pocket)离子注入来提高衬底与源漏交界面的掺杂浓度,从而降低源漏耗尽区的宽度,达到抑制短沟道器件的DIBL效应。

介绍浅源漏结深,源和漏结深与DIBL效应成正比,可以通过减小源和漏有源区结深改善DIBL效应。

介绍倒掺杂阱,包含阱离子注入、沟道离子注入和阈值电压离子注入。

介绍阱邻近效应,靠近阱边缘的器件的电特性会受到器件沟道区域到阱边界距离的影响,这种现象称为阱邻近效应(Well Proximity Effect - WPE)。

介绍反短沟道效应,在经典的理论里,对于短沟道器件,器件的阈值电压会随着沟道长度变小而变小,而饱和电流会随着沟道长度的变小而增大。但是,在实际的工艺中引入了晕环离子注入,器件的阈值电压并不会随着沟道长度变小而变小,而是出现先增大后变小的效应,业界称这个效应为反短沟道效应。

第十六讲的主要内容:(热载流子注入效应与轻掺杂漏工艺技术)

介绍热载流子注入效应,载流子被沟道的强电场加速形成热载流子,并与晶格发生碰撞电离,碰撞电离会产生一群能量非常高的热电子和热空穴,热电子越过Si/SiO2界面的势垒形成栅电流,热空穴会流向衬底形成衬底电流Isub,这种现象就是热载流子注入效应。

介绍热载流子导致器件的阈值电压漂移和致势垒降低(DIBL)效应。

介绍热载流子导致NMOS寄生的NPN导通。

介绍热载流子导致闩锁效应。

介绍双扩散漏(DDD)工艺技术。

介绍轻掺杂漏(LDD)工艺技术。

介绍侧墙(SpacerSidewall)工艺技术。

介绍轻掺杂漏离子注入和侧墙工艺技术的工程应用。

课程内容摘选

讲师简介:

温德通,资深芯片设计工程师。畅销书《集成电路制造工艺与工程应用》的作者。毕业于西安电子科技大学微电子学院,曾供职于中芯国际集成电路制造(上海)有限公司,负责工艺制程整合方面的工作;后加入晶门科技(深圳)有限公司,负责集成电路工艺制程、器件、闩锁效应和ESD电路设计等方面的工作;2018年11月离开晶门科技。

版权申明:2018年11月10日温德通先生已经把视频内容授权EETOP全权负责

长按二维码或点击阅读原文参与学习

(可试看)

关于创芯大讲堂

edu.eetop.cn

创芯大讲堂是EETOP旗下在线教育平台,后续会推出一系列微电子行业在线课程。

EETOP是国内知名的半导体、微电子工程师社区。创芯大讲堂推出的课程会是围绕半导体集成电路全产业链,将会包括:从设计到制造,从前端到后端,从模拟、数字到混合集成电路等。希望通过我们的努力能为中国集成电路发展、人才培养等做出微薄之力。

作为一个大型电子工程师社区,当然我们也不仅仅只关注集成电路,后续我们也会推出硬件设计、嵌入式设计相关的各种课程。

>>点击阅读原文,获取更多精品课程!