集成设计新思路 提升芯片制造能力——三维集成技术使得超越摩尔定律成为可能

最近一系列事件再次表明,制约中国芯片产业发展的主要因素已集中到制造能力。如何快速提升制造能力,推动芯片产业发展?只有不断地研发和创新。

在芯片界,摩尔定律一直占据统治地位。

摩尔定律接下来是终结还是延续,已成为过去十年芯片界热议的话题。

摩尔定律自1965年发明以来,一直引领着世界半导体产业向实现更低的成本、更强的性能、更高的经济效益的目标前进。然而,随着半导体技术逐渐逼近硅工艺尺寸极限,原摩尔定律导出的“IC的集成度约每隔18个月翻一倍,而性能也将提升一倍”的规律将受到挑战。

半导体制造工艺的两种演进路线图

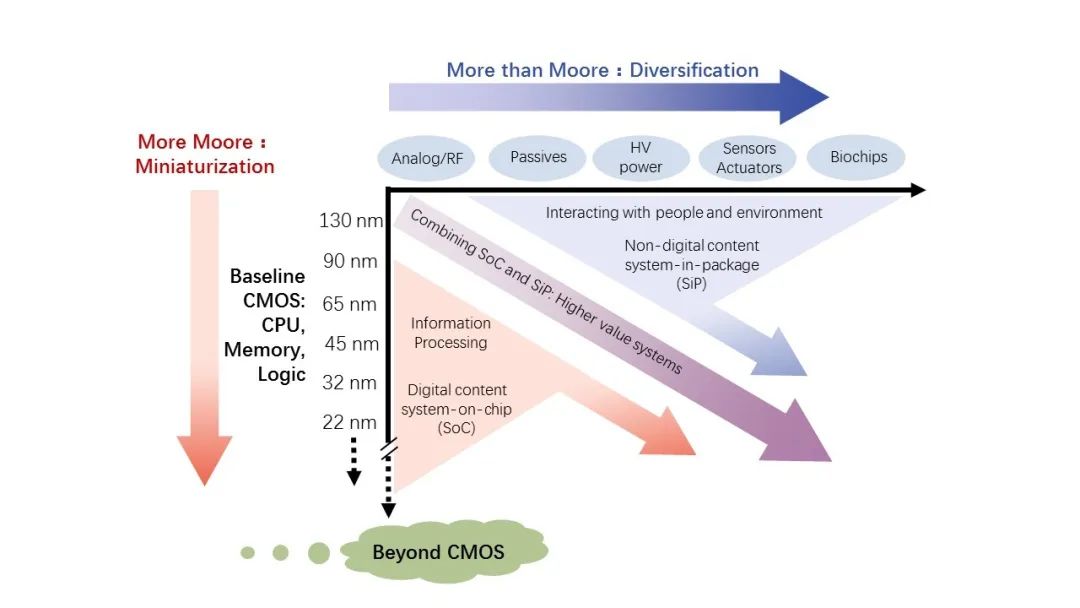

为此, ITRS组织针对半导体产业中远期发展的挑战,在技术路线制定上,提出选择两种发展方式(如图1):一是继续沿着摩尔定律按比例缩小的方向前进,专注于硅基CMOS技术;二是按“后摩尔定律”的多重技术创新应用向前发展,即在产品多功能化(功耗、带宽等)需求下,将硅基CMOS和非硅基等技术相结合,以提供完整的解决方案来应对和满足层出不穷的新市场发展。

图1 半导体技术的发展路线

使用先进节点的好处很多,晶体管密度更大、占用空间更少、性能更高、功率更低,但挑战也越来越难以克服。

极小尺寸下,芯片物理瓶颈越来越难以克服。尤其在近几年,先进节点走向10nm、7nm、5nm,问题就不再只是物理障碍了,节点越进化,微缩成本越高,能担负巨额研发费用并实现盈利的设计公司越来越少。

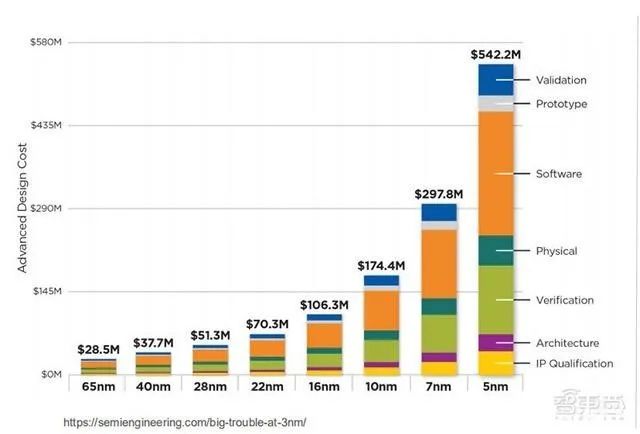

图2 随着制程节点进化,芯片成本快速增长

根据公开报道,28nm节点设计成本约为5000万美元,而到5nm节点,设计总成本已经飙高到逾5亿美元,相当于逾35亿人民币。先进工艺如果只能提升性能,无法有效降低甚至守住成本,选择最先进工艺的客户将变得越来越有限。

幸运的是,每当摩尔定律被唱衰将走到尽头,总会激发出科学家和工程师们创新构想,提出力挽狂澜的突破性技术,将看似走向终结的摩尔定律以“后摩尔定律”的形式延续下去。

“后摩尔定律”的实质是,它除了会延续摩尔定律对集成度、性能的追求外,还会利用更多的技术,例如模拟/射频、高压功率电源、MEMS传感器、生物芯片技术及系统级封装(SiP)等三维集成技术,以提供具有更高附加值的系统。

ITRS指出,在“后摩尔定律”范畴,随着新兴应用不断出现,智能化微系统芯片将会进入三维集成时代。

三维集成技术概览和两条主要的工艺路线

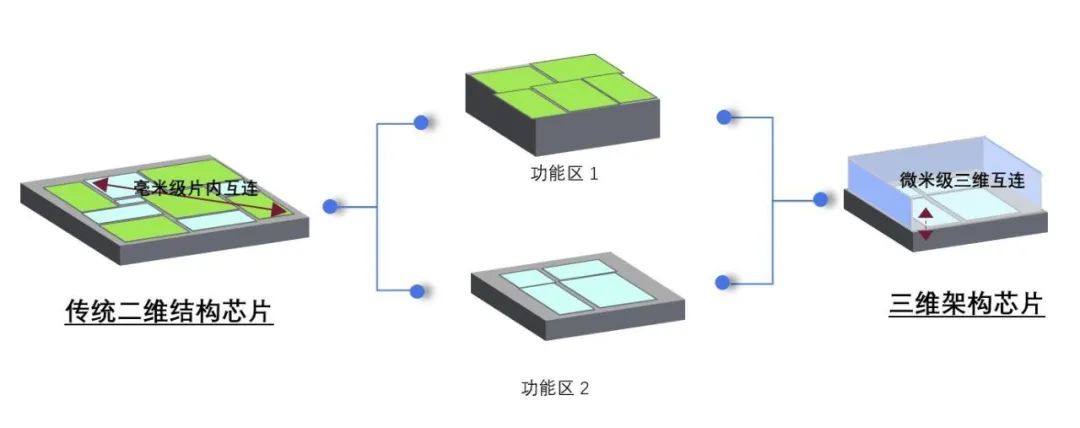

三维集成电路又称立体集成电路,是集成电路从传统平面集成方式向垂直方向立体集成方式延伸的产物。三维集成电路的优势在于:多层器件重叠结构使芯片集成度成倍提高;TSV和混合键合工艺使芯片间互连长度大幅度缩短,提高传输速度并降低了功耗;多种工艺混合集成,使集成电路功能多样化;减少封装尺寸,降低设计和制造成本。

三维集成技术可将多层集成电路芯片或晶圆堆叠键合,通过三维互连实现多层之间的电信号连接。三维集成技术能实现异质芯片互连结合,发挥出最高系统性能水平,是其独特的最大优势。

图3 三维集成技术示意图

经过十来年的发展,三维集成技术逐渐形成两条主要的工艺路线:晶圆间三维堆叠和封装厂主导的芯片间三维互连。

通过键合堆叠和连通孔工艺的持续改进满足芯片对更大带宽、更小功耗的要求。其工艺目前主要用于图像传感器的生产,近些年,随着物联网、人工智能和5G对更大带宽、更小功耗和更低延时等特性产品的要求,晶圆级三维集成开始应用于大容量存储、存算一体、高性能计算等领域。代表厂家有Intel、TSMC、Samsung、SONY等。

芯片级三维集成,主要追求芯片间凸点(Bump)连接小型化,来提高集成度和芯片性能。其技术特点依托于封装打线(Wire bond)和凸点(bump)为基础,把不同功能的芯片通过毫米级的封装工艺连接。代表厂家主要为半导体制造领域的后端封装厂,如Amkor、SPIL、ASE、长电、华进等。

二者互有优劣,晶圆间堆叠工艺精度高、互联密度大;但相较芯片间互连,其良率相对较低、对芯片尺寸匹配度要求高。

国内晶圆级三维集成技术平台代表:武汉新芯

从2012年起,紫光集团旗下的武汉新芯就开始研发第一代晶圆级三维集成制造工艺,并于2013年成功实现背照式影像传感器的量产,并同步开始第二代晶圆级三维集成技术的研发,2014年硅通孔堆叠技术实现量产。

经过多年的发展和积累,武汉新芯的三维集成制造工艺水平与业界第一梯队公司TSMC,索尼,三星等相当,产品已打入国际知名手机品牌以及国内知名品牌终端。在上两代技术的基础上,武汉新芯于2016年完成第三代三维集成技术的研发,成功研制出晶圆级混合键合技术,并成功应用于长江存储64层3D NAND产品上,其技术能力已达到世界顶尖水平。

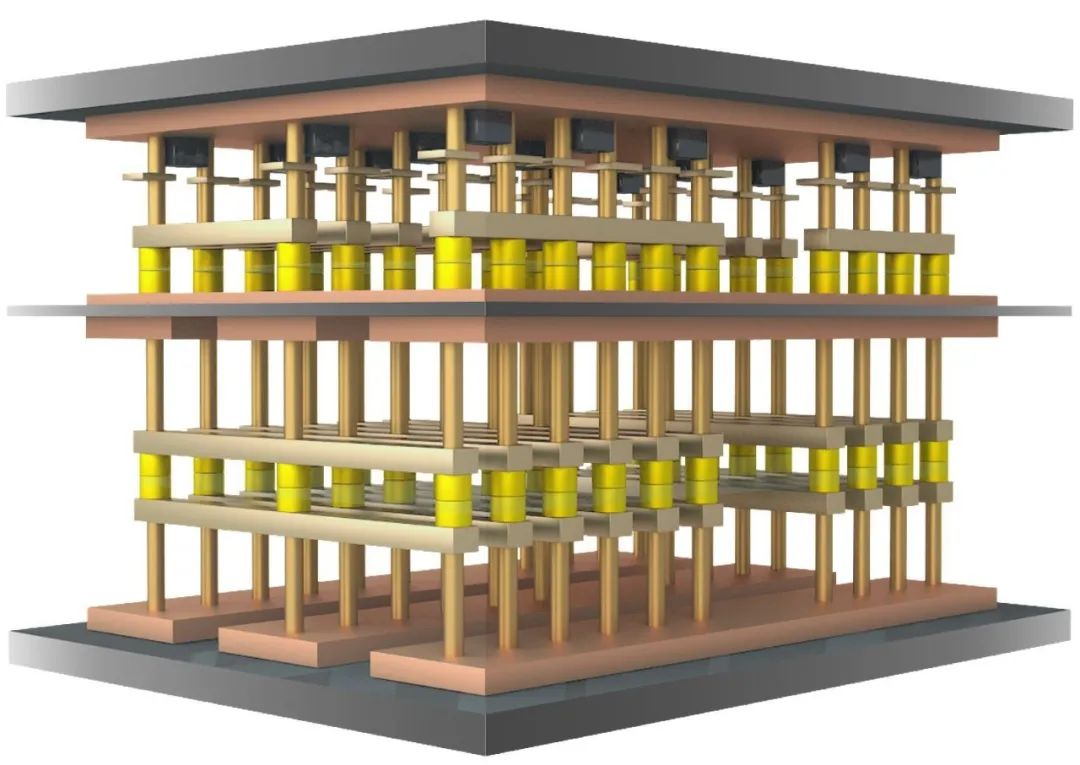

2018年,武汉新芯启动第四代三维集成技术—多晶圆堆叠技术研发,并于2018年底完成工艺验证,成功迈入多晶圆垂直整合领域。未来还将深耕三维集成领域,开发异质集成技术,目标成为国内一流的12寸三维集成技术工艺生产平台。

图4 武汉新芯多片晶圆堆叠结构示意图

通过自身半导体三维集成技术研发和产品拓展,武汉新芯将带动上下游企业共同发展。在目前工艺条件下,提供更小的芯片面积,以及更高的集成度,力主获得具有自主知识产权的核心技术体系和成套工艺解决方案,并将之应用于芯片的开发和生产,实现我国集成电路产业的局部突破和升级,使我国集成电路产业在三维集成技术这一领域,缩小与世界先进水平的差距。