IWAPS 2020 特邀嘉宾:斯坦福大学H.-S. Philip Wong教授

第四届国际先进光刻技术研讨会(International Workshop on Advanced Patterning Solutions)将于11月5~6日在四川成都举办,本次会议特别邀请到了斯坦福大学H.-S. Philip Wong教授做特邀报告。

(International Workshop on Advanced Patterning Solutions)

会议详情请点击进入 IWAPS 2020

第四届国际先进光刻技术研讨会由中国集成电路创新联盟与中国光学学会联合主办,由中国科学院微电子研究所、中国科学院光电技术研究所、中科微电子产业技术西南研究院以及四川省经济合作局承办。IWAPS研讨会专注于高端光刻技术,为来自国内外半导体工业界、学术界的资深技术专家和优秀研究人员等提供了一个技术交流平台,参会者可以就材料、设备、工艺、测量、计算光刻和设计优化等主题分享各自的研究成果,探讨图形化解决方案,研讨即将面临的技术挑战。

H.-S.Philip Wong 博士于 2004 年加入斯坦福大学 (Stanford University),担任电气工程教授,并在工程学院获得 Willard R. 和 Inez Kerr Bell 教授职位。2018 年-2020年,他在全球最大半导体代工厂台积电 (TSMC) 公司担任研究副总裁,负责探索新一代半导体技术。1988 年至 2004 年,他在 IBM T.J. Watson 研究中心任职,负责制定和执行 IBM 在纳米科学技术以及探索性硅器件和半导体技术方面的战略。H.-S. Philip Wong 博士是 IEEE 会士,曾担任 IEEE Transactions on Nanotechnology 主编 (2005–2006),ISSCC 的小组委员会主席 (2003–2004),IEDM 的总主席 (2007),目前是 IEEE Executive Committee of the Symposia of VLSITechnology and Circuits 执行委员会主席。他是斯坦福大学非易失性存储器技术研究计划 (NMTRI) 的系主任,也是斯坦福 SystemX 联盟的创始系主任。

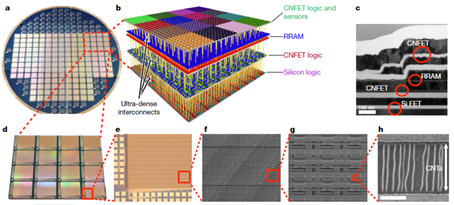

图1. 3D纳米系统结构.

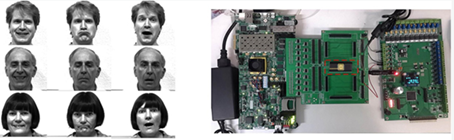

图2. 类脑计算示意图.

图3. 用于识别人脸图像和测试系统示意图. (图片来源: 清华大学新闻网[2])

关于H.-S. Philip Wong教授的更多研究内容请见:

https://web.stanford.edu/~hspwong/

参 考 资 料

[1] M. M. Shulaker et al., "Three-dimensionalintegration of nanotechnologies for computing and

data storage on a single chip," Nature. 547, 74 –78 (2017).

[2] 清华大学新闻网:https://news.tsinghua.edu.cn/info/1007/54066.htm.

[3] P. Yaoet al., "Face classification using electronic synapses," NatureCommunications. 8, 15199 (2017).