基于板载FPGA的5G基站芯片的低成本测试方案

关注并标星我们,获取最新资讯

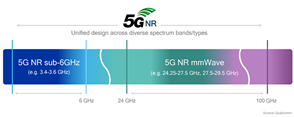

随着人们对高速无线数据传输需求的不断增长,也由于现有网络的带宽和速度无法满足更为前沿的需求,5G通信标准应运而生。

最新发布的5G通信标准中的SUB-6G频段以更高的载波频点,更宽的带宽以及相对成熟的技术,发展迅猛。而5G商用元年的到来,5G基站作为5G通信的基础设施,率先覆盖了世界的各个角落。

基站芯片作为基站中远程射频单元的核心,用以连接核心网络与终端网络。其开发和测试也在保证高可靠性的基础上,尽可能得实现高效率与低成本。

+

关于5G基站芯片

相较于5G的终端芯片,基站芯片拥有更复杂的功能及更强的性能,主要包括以下几点:

数字信号传输接口的传输速率更快,芯片的内部包含了高速串列解串器作为数字信号传输接口,用来接收数字IQ信号,通常可以达到16Gbps以上,最高可达到112Gbps。

数字信号传输接口的数量更多,通常有4对以上的发送和接收端,最高可达到16对以上。

集成了针对SUB-6G频段的射频单元及数字和模拟基带,在芯片内部就可以对数字IQ进行转换,并加载到对应频点,输出射频信号。

射频通道发送和接收的信号的带段更宽,支持的频点更多。

集成了更复杂的数字逻辑及存储单元。

+

5G基站芯片的测试需求

针对如下几点严苛的测试需求,爱德万测试(ADVANTEST)提出了一套基于V93000 自动化测试平台的完整的硬件与软件的测试方案,以提升测试效率及降低测试成本。

01

对应于芯片极高的数据传输速率,测试方案需要有发送及接收高速信号的能力,并能对芯片发送的信号质量及接收能力进行表征。同时,芯片需要一个高精度的时钟源进行参考。

02

对应于芯片的射频信号的极宽的带宽及众多频点,测试方案需要完全覆盖芯片输出的频域,并通过提高并行度,以实现较短的测试时间。

03

对应于芯片内部复杂的数字逻辑及数量众多的功能模块,测试方案需要能够高效得对芯片进行配置。

+

基站芯片的测试解决方案

01

针对于芯片极高的数据传输速率的测试需求

首先,高精度的时钟源不可或缺。然而,使用高精度的时钟板卡(LPN)将在一定程度上增加测试成本。因此,ADVANTEST提供了一种板载的模块,JAM(Jitter Attenuator Module)。通过降低PS1600数字通道的抖动,使通用的数字通道成为高精度的时钟源,从而减少用于产生高精度时钟所需要的测试成本。

JAM(Jitter Attenuator Module)

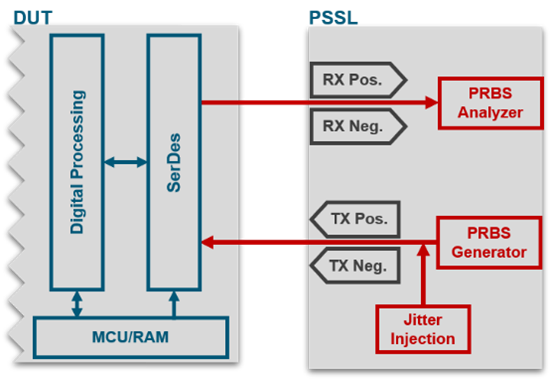

针对芯片数据传输速率为16Gbps以下的数字信号,ADVANTEST提供了一款高速数字板卡,PSSL,可对与芯片数据传输性能进行表征。PSSL板卡内的伪随机序列分析模块被用来测试芯片输出端的眼图。而PSSL板卡内部的抖动注入模块也被用来测试芯片接收端的抖动容忍度 。

Test Approach Demonstration via PSSL

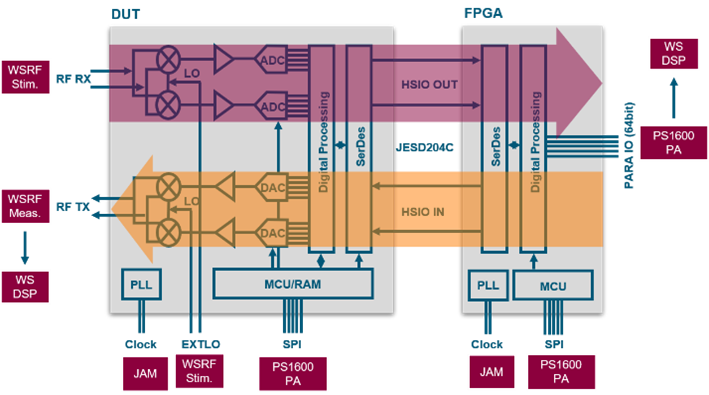

针对芯片高达32Gbps数据传输速率的数字信号,ADVANTEST和客户紧密合作,提出了通过板载可编程门阵列(FPGA)作为高速串列解串器,将64bit并行数据转换成为最高32Gbps的串行数据,差分输出,反之亦然。实现了高达32Gbps数据传输速率的全速测试。

Test Approach Demonstration via On-Board FPGA and JAM

该方案中,所以的高速节点的连接都是通过同轴信号线缆。这在增加了测试灵活性的同时,降低了测试板的设计难度。

02

针对于芯片射频信号的多频点、大带宽的测试需求

ADVANTEST发布的新一代射频板卡WSRF可以很好得满足5G通信标准中所包含的SUB-6G频段,200MHz以上的带宽以及更复杂的调制解调方式。多端口数也可以很好得满足高并行度测试的需求

03

针对于需要对芯片进行高效配置的测试需求

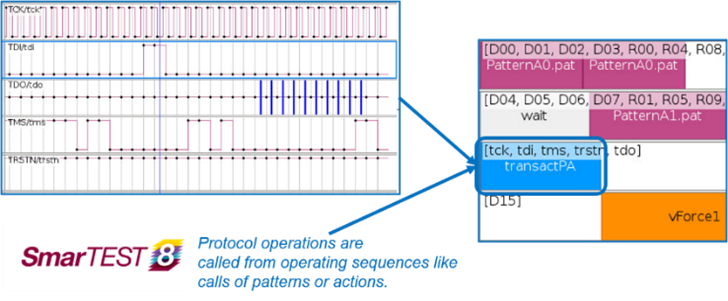

ADVANTEST全新发布的SmarTest8操作系统中,集成了针对通用协议的Bottom-up式的解决方案,同时也支持客制化。这使得测试程序的编写更加便捷。在降低了工程师的工作量的同时,也降低了后期维护的难度。

SmarTEST8 Protocol Aware Function

基于V93000平台的板载FPGA低成本测试方案,不仅实现了高精度,高可靠性与高效率的测试验证。其高灵活性的特性,使其可以被推广到所有高集成度的高速-射频芯片的表征与量产测试中,助力5G技术的高速发展和广泛应用。

作者:MJ Tang

站在专业的视角安利着高价值的产品