来源:内容由半导体行业观察(ID:icbank)编译自「IMEC」,谢谢。

在本周举办的IEDM 2020上,IMEC展示了一种新颖的动态随机存取存储器(DRAM)单元架构,该架构实现了两种铟镓锌氧化物薄膜晶体管(IGZO-TFT),并且没有存储电容器。

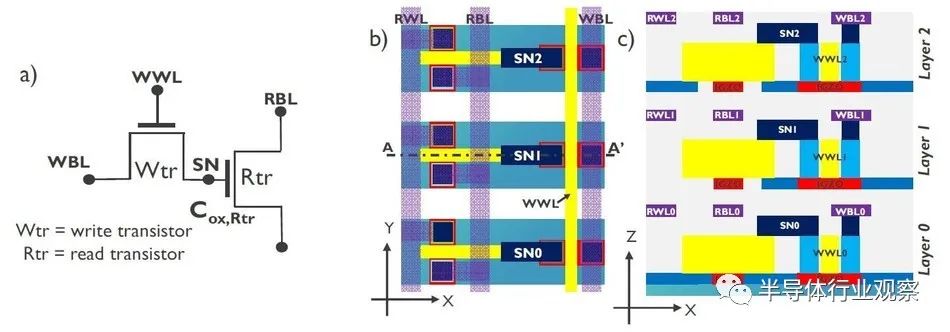

对于不同的单元尺寸,这种2T0C(2晶体管0电容器)配置的DRAM单元显示的保留时间超过400s –显着降低了存储器的刷新率和功耗。在BEOL中处理IGZO-TFT的能力减少了CELL的占地面积,并为堆叠单个CELL提供了可能性。这些突破性成果为低功耗和高密度单片3D-DRAM存储器铺平了道路。(a)2T0C DRAM单元的示意图,其中存储元件是读取晶体管的氧化物电容Cox;(b)2T0C DRAM阵列在单个平面上的示意性俯视图示例。A-A'截面方向表示,可以通过(c)堆叠2T0C单元的几层来增加阵列密度。将传统的1T1C(一个晶体管一个电容器)的DRAM扩展到超过32Gb的裸片密度面临着两个主要挑战。首先,基于Si的阵列晶体管缩放的困难使得在减小单元尺寸的同时保持所需的关断电流和world line resistance 具有挑战性。其次,3D集成和可扩展性(通向高密度DRAM的终极途径)受到对存储电容器需求的限制。Imec提出了一种新颖的DRAM体系结构,可以应对这两个挑战,从而提供了一条通往低功耗高密度3D-DRAM存储器的扩展路径。新架构实现了两个IGZO-TFT,它们以极低的关断电流而闻名,并且没有存储电容器。在这种2T0C配置中,读取晶体管的寄生电容用作存储元件。由于3x10 -19 A / µm的极低(抽出)关断电流,所得DRAM单元的保留时间> 400s 。这些突破的结果是在300mm晶圆上加工的优化规模IGZO晶体管(栅极长度为45nm)上获得的。优化旨在抑制氧和氢缺陷对电流和阈值电压的影响-这是开发IGZO-TFT的主要挑战之一。imec计划总监Gouri Sankar Kar表示,除了保留时间长之外,基于IGZO-TFT的DRAM单元还具有超越当前DRAM技术的第二个主要优势。与Si不同,IGZO-TFT晶体管可以在相对较低的温度下制造,因此,与BEOL处理兼容,这使我们能够将DRAM存储器单元的外围移动到存储器阵列下方,从而显着减少了存储器裸片的占位面积;此外,BEOL处理还开辟了通往堆叠单个DRAM单元的途径,从而使3D DRAM体系结构成为可能。IMEC的突破性解决方案将有助于拆除所谓的内存墙,使DRAM内存在要求苛刻的应用(例如云计算和人工智能)中继续发挥关键作用。

★ 点击文末【阅读原文】,可查看本文原链接。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2526内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

ICCAD2020|存储|晶圆|华为|汽车芯片|联电|高通|射频|封测

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!