【科普】DDR5 vs DDR4的不同点

以下文章来源于信号完整性 ,作者蒋修国

本公众号由蒋修国于2014年创办 1、分享信号/电源完整性(SI/PI)、电磁兼容性等方面的知识/行业信息 2、不定期举办各类公益活动 3、帮助工程师学习高速电路、RF、EMC和PCB的设计 出版过《ADS信号完整性仿真与实战》等书籍

EETOP专注芯片、微电子,点击上方蓝字关注我们

编者注:关于DDR5的内容揭秘的还不是非常多,但是随着规范的release,会有越来越多的相关内容会出来,本文主要是针对本人理解的几个点来做介绍,并不是最完善的,欢迎大家添砖加瓦。

前面也给大家分享了DDR5的仿真与测试,由于规范没有发布,所以很多时候看得并不是很理解。随着DDR5规范发布脚步的越来越近,JEDEC规范的会员到时候就能拿到全文内容。

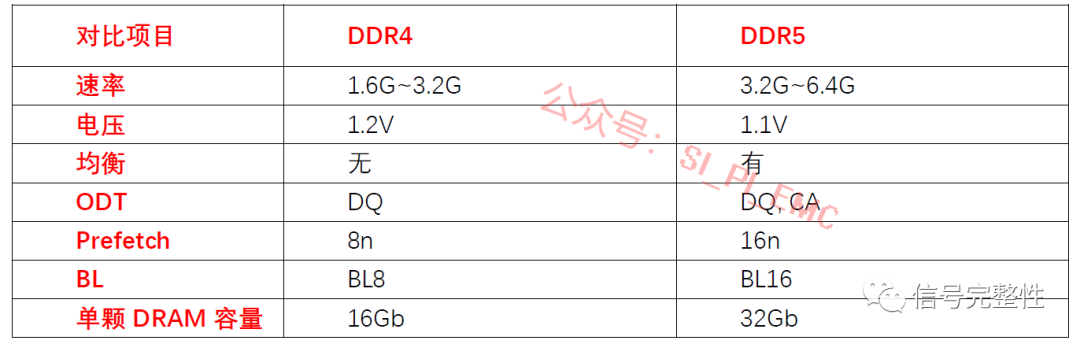

为了让大家简单而快速的有一些印象,本文只是对DDR5和DDR4不同点的做了一个简单对比:

下面分别介绍下这表中列举的7个显著不同点:

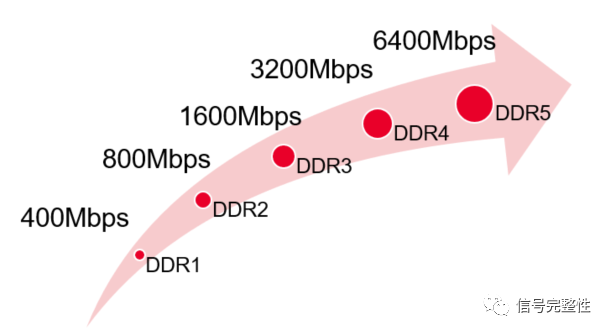

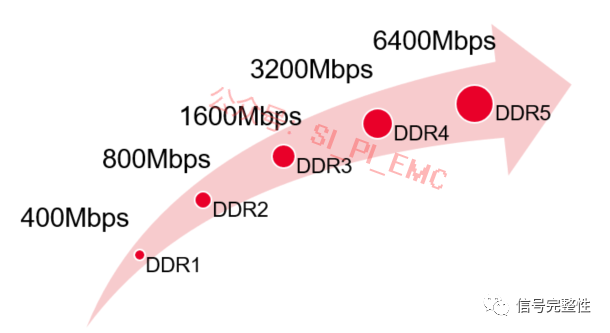

1、速率

速率是变化是每一代总线必不可少的一部分。DDR5的最高速率可以达到了6.4Gbps,与以往的总线发展一样,在开始阶段6.4Gbps的规范其实还没有完全定义好,看到有些厂商也只做到了4.8G。速率的提升使时序裕量越来越小,给信号完整性设计带来极大的挑战。

2、电压

电压从1.2V将会变到1.1V,下降了8.3%,这是几代DDR总线以来下降比例最少的一次。说明电子技术的发展,对于低功耗的设计难度越来越大。这么低的电压,其抗干扰设计就会更加的难。对于电源完整性和信号完整性的设计要求就越来越严苛。

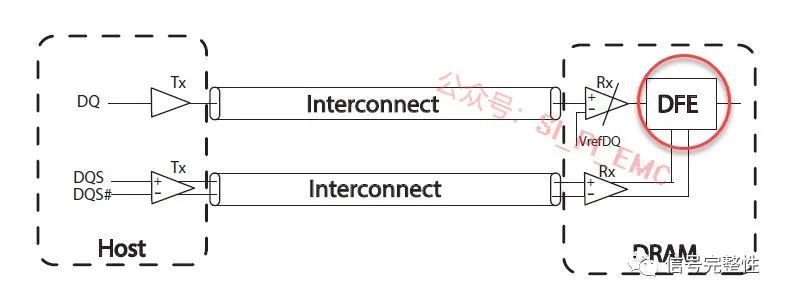

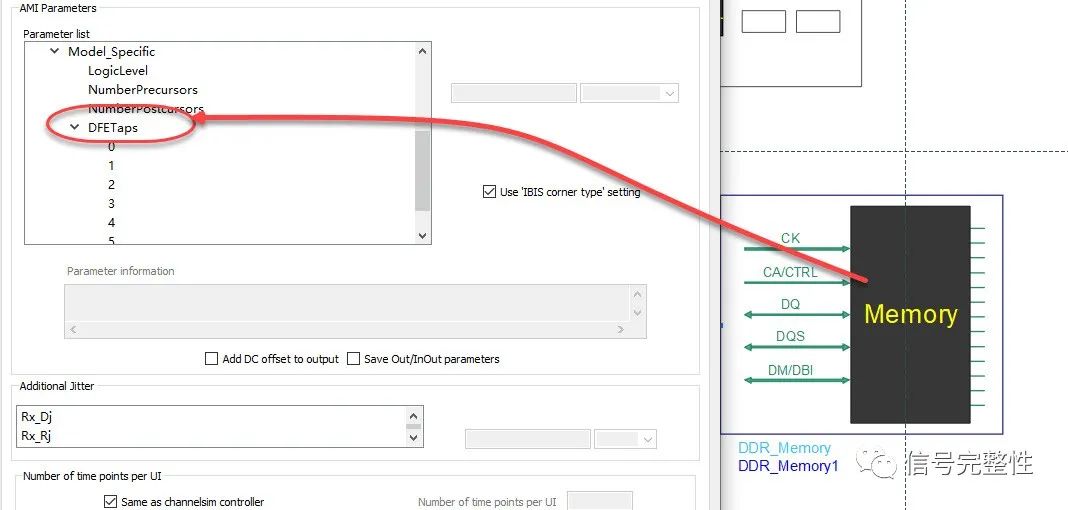

3、均衡

虽然在DDR4的设计中有一些场景也有使用均衡,但是常规芯片中并没有使用DFE的均衡技术。但是DDR5的速率提升,已经达到了惊人的6.4Gbps,使信号的ISI、串扰、抖动等都会变得更加严重,需要通过均衡技术来调整信号的质量。但是均衡也会导致功耗变大。

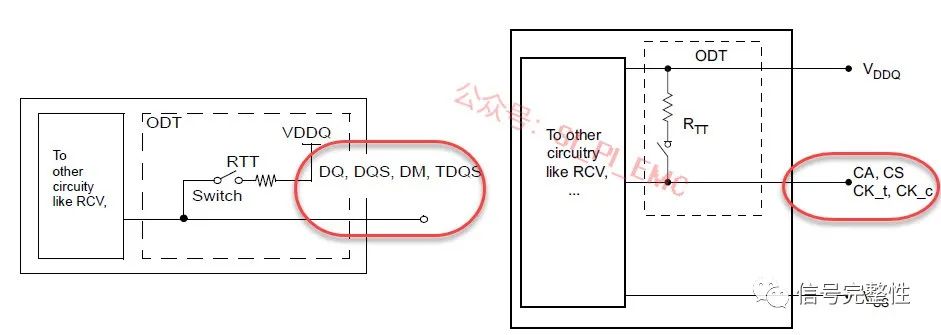

4、ODT

DDR5很大的一个变化来自于ODT。这与ODT的应用传统是一样的,在DDR4时,只有DQ/DQS/DM作为接收端时有使用ODT,而在DDR5这一代总线中,DQ/DQS/DM继续保有ODT功能,在CA这类信号中也使用了ODT。这样在多拓扑结构设计时就更简单啦。

5、容量变大

单颗DRAM的容量变得更大,DDR5的单颗容量可以达到32Gb。

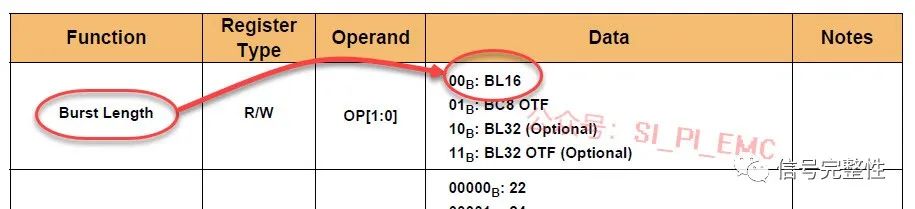

6、Burst length

Burst length变长, DDR4的burst length为8,而DDR5达到了16。这就使得DDR5的并发性在DDR4的基础上提升了一倍,这一技术也使得信号更高效的传递。

7、Prefetch

从DDR3到DDR4这一代总线的发展,prefetch是没有变化的,不知道是不是当时有些问题没有突破,但是DDR5这一代总线,依然借助于prefetch来提升信号传递的速率。

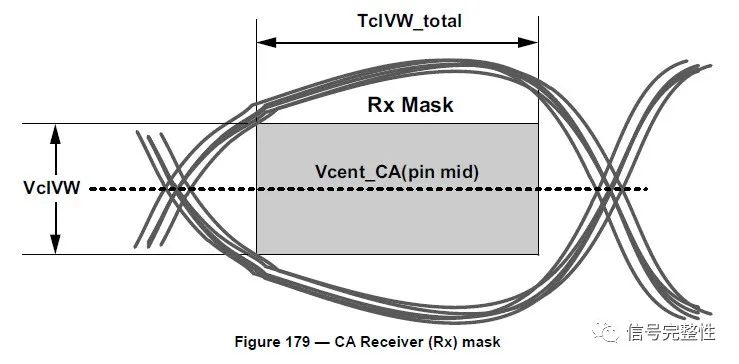

虽然本文只介绍了这7个不同点,实际上从现在的DDR5规范来看,还是有非常多的变化,比如增加了CA的眼图要求,等等,DDR5规范的内容都比之前增加了100多页。