【21届春招 社招】中科集团海光公司,国产CPU"HYGON"设计者,CPU设计/验证、模拟/FPGA多岗位,校招社招同步开始!

以下文章来源于IC集友圈 ,作者IC集友圈

IC集友圈成立于2020年,由飞姐与多位IC业内资深前辈创立。集友圈专注于IC行业内推求职、精英直聘和信息交流,致力于打造互助互惠的IC行业圈,为推动中国IC行业环境优化而努力。

IC集友圈成立于2020年,由飞姐与多位IC业内资深前辈创立。集友圈专注于IC行业内推求职、精英直聘和信息交流,致力于打造互助互惠的IC行业圈,为推动中国IC行业环境优化而努力。

我们不只有行业的深度,还有圈子的温度。在集友圈里有前辈们知无不言,有后浪们蜂拥而至,还有业内巨擎AMD、Intel等进行招聘内推。现已有数千ICer加入我们,集友圈正在等待你的加入!

投递说明:

将公众号设为星标不迷路,获取更多内推信息、专业知识和行业新闻哦!

加入内推群可及时获取后期招聘动态,更多岗位请扫码进集友圈查看每日更新哦!

公司介绍

海光信息技术股份有限公司有干人规模的研发团队,吸引了大批有成就的优秀科技人才,其中具有博士、硕士学位的人员占员工总数的80%以上,涵盖了CPU/DCU关键技术研究、处理器核心和SoC芯片研发、定制与模拟电路、生产工艺、封装测试、基础软件及系统研发等各个环节。海光也极其注重公司文化建设,“拼搏创业、团结协作、锐意创新、结果导向”是我们的核心价值观,如果你愿意为芯片国产化贡献力量。

公司性质:国资+外企合资

薪酬福利

热招职位

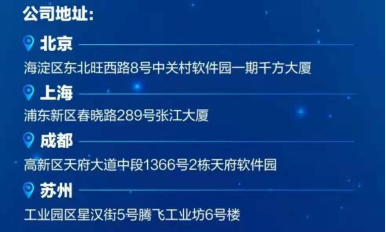

○工作地点:上海、北京、成都、苏州

○内推岗位:CPU设计/验证、模拟、FPGA、固件/软件

○岗位信息:

· 【校招/社招】DCU验证工程师

工作地点:北京/上海/成都

岗位职责

1、根据设计规格,提取功能点和测试点,设计和编写测试用例,完成验证计划编写

2、理解芯片和模块功能,开发直接和随机测试激励,开发各种monitor和checker ,BFM以及assertion

3、调试各种testench和testcase 失败案例,与设计工程师一起修复并验证bug

4、执行验证计划,进行回归测试,确保代码覆盖率和功能覆盖率达到tape out要求

5、 维护并改善testbench和验证流程,评估或采用最新工具和方法

6、协助软、硬件设计人员开展软、硬件相关调试工作

任职要求

1、电子工程、微电子或相关专业

2、熟练掌握Verilog, SV, C/C++, SystemC等语言

3、熟悉testbench结构和验证方法学,比如UVM,OVM或VMM

4、熟悉ASIC验证流程和常用EDA仿真、调试工具

5、较强的script能力,比如Perl, Python, Ruby,Unix Shell,或相关语言

6、参与过大规模并行运算验证,大型Server级芯片验证,多核CPU,GPU或AI芯片验证经验者优先

7、熟悉performance verification, power verification 优先8、较强的解决问题能力,良好的沟通能力和团队协作能力

· 【校招/社招】CPU设计工程师/RTL设计工程师

工作地点:北京/上海/成都/苏州

岗位职责

1、研发高性能服务器CPU core

2、制定处理器模块微结构设计规范

3、对性能、功耗、面积进行分析和权衡,选取优化设计方案

4、开发处理器模块RTL

5、与验证团队协作验证设计正确性

6、与物理设计团队协作实现时序收敛和功耗优化

7、与性能团队协作开发性能/功耗模拟器、模型和测试集

任职要求

1、计算机科学、计算机工程或电子工程等相关专业学位

2、有以下至少一项经验:计算机体系结构知识、CPU微架构知识、浮点运算算法、PU周期精准性能模拟器、Cache coherence、power management、 security等领域知识

3、有工业界处理器研发经验者优先

【校招/社招】CPU验证工程师

工作地点:北京/上海/成都/苏州

岗位职责

1、开发处理器核、多核以及模块级验证环境

2、制定验证计划

3、开发/运行/调试测试用例以及功能覆盖点

4、使用多种验证工具、平台,例如形式化验证工具,Emulator

5、开发/维护仿真测试平台基础设施

任职要求

1、计算机科学、计算机工程或电子工程等相关专业学位

2、有以下至少一项经验:计算机体系结构知识、验证环境开发,如UVM/OVM、编写测试用例,开发检查器,覆盖率分析,错误调试,错误原因分析、形式化验证、指令集模拟器、汇编语言编程,随机指令序列生成器,系统底层软件

3、熟悉以下至少一种编程语言:C/C++, Perl, Python, Ruby

【校招/社招】FPGA/EMU工程师

工作地点:成都

岗位职责

1. Emulation平台验证,移植RTL代码到Emulation平台验证

2. 建立并维护Emulation 平台

任职资格:

1. 计算机,微电子等相关专业研究生在读

2. 熟悉Emulation及其基本原理

3. 熟悉Verilog,SV等语言

4.熟悉Linux下面工作环境,掌握VCS、Modelsim、NC等仿真工具

5. 有实际FPGA项目开发,验证,调试经历更佳

· 【校招/社招】混合信号/模拟电路工程师

工作地点:苏州/上海

岗位职责

1、负责HSIO (PHY),Digital PLL,LDO , ADC 等IP电路规格定义、设计、仿真、验证等工作

2、指导Layout工程师完成版图设计工作

3、负责IP EDA View Model (LEF/Lib/.v等) 生成以及验证工作

4、协助SOC前后端工程师完成IP 集成以及验证等工作

5、负责IP 测试芯片设计、硅后测试以及相关报告编写工作

任职要求

1、电子/信号通讯等工程相关专业硕士毕业

2、模拟、混合信号电路设计经验优先

3、有MATLAB建模经验优先

4、有Verilog/VerilogA 经验优先

5、有Finfet工艺经验优先

· 【校招/社招】软件工程师

工作地点:上海

岗位职责

1、负责公司相关产品的软件开发移植、适配、性能评测和调优工作

2、针对公司相关用户提供相应的解决方案,引导和指导用户推广公司产品

3、对公司相关用户在OS、上层软件等方面提供相应的设计指导、调试支持,解决客户所反馈问题

4、能有效收集、分析、提取客户对产品的改进意见、客户支持要求

5、负责公司相关产品的OS和上层应用软件等相关代码、文档的编写、维护工作

任职要求

1、本科以上学历,计算机相关专业

2、熟练使用linux或window OS和上层软件开发和调试中使用的各种软件工具

3、具备较强的沟通与协调能力,能够与其他部门良好互动合作

4、具有较好的英语读写能力

5、能够承受较大的工作压力,具备较好的团队合作精神

· 【校招/社招】DCU/SOC设计工程师

工作地点:北京/成都

岗位职责:

1. 负责SoC系统级/模块级 Design spec/mas的定义和编写

2. 负责SoC系统/模块的RTL设计和集成

3. 负责SoC系统/模块的performance/power的分析和优化

4. 配和验证团队, FPGA验证平台团队以及硬件加速平台团队,完成系统级、模块级的验证工作

5. 配和FEINT团队, 完成SDC约束,Lint check, 时序收敛等工作

岗位要求:

1. 熟悉ARM或X86的计算机体系架构

2. 熟悉ASIC/SoC设计开发流程,熟悉SoC架构

3. 具有ASIC/SoC 设计集成经验

3. 熟悉Verilog, C, C++, 及验证语言 (SystemVerilog等)

4. 熟悉IC设计相关的EDA工具者优先,比如DC, PT, NCSIM, VCS 等

5. 熟悉脚本语言,包括perl,shell, tcl等

6. 工作积极主动,有良好的分析问题,解决问题的能力

· 【校招/社招】CPU架构师

工作地点:北京/上海/成都/苏州

工作职责:

1. CPU微架构性能模拟器开发

2. 系统级性能模拟器开发

3. 基准测试程序性能分析和研究

4. 面向微架构的基准测试程序开发

任职资格:

1.熟悉CPU微架构

2.了解计算机体系结构

3.了解linux kernel

4.具备一定编译器和指令集知识

5.熟练C/C++以及python开发

· 【校招/社招】固件工程师

工作地点:成都/北京

岗位职责:

1. 负责海光的SoC芯片固件的设计,开发和维护工作

2. 编写测试用例保证软硬件正常工作

3. 设计和开发调试和验证工具,支持芯片的Pre-Silicon仿真和post-silicon验证工作

4. 调试和验证固件,以支持硬件仿真平台和真实芯片。

任职资格:

1. 3年以上驱动和固件开发工作经验,有ARM系统开发/调试经验者优先

2. 熟悉固件开发工具,如编译工具,调试工具,开发环境等。

3. 熟悉C/C++/汇编/脚本语言

4. 对工业协议有较好理解(DDR/PCIE/I2C/SATA......)者优先

5. 良好的沟通技巧和团队协作能力,工作积极主动

6. 良好的书面英语沟通能力

· 【社招】DFX设计工程师

工作地点:北京/上海/成都/苏州

岗位职责

SoC DFX (DFT design for Test/DFD design for debug)架构设计、前端设计、代码集成

任职要求

1、3年以上大规模数字集成电路架构规划经验、复杂功能设计经验

2、具备SoC或者模块级验证经验

3、熟悉计算机体系结构

4、熟悉常见总线协议(如AMBA)和外部接口

5、熟悉IC设计流程和数字设计前端工具

6、熟悉DFT测试原理、JTAG相关协议优先

7、有CPU相关设计经验,总线相关、以及HSIO相关设计经验优先

8、有SoC级Debug相关设计经验<coresight等>的优先

9、了解CPU 体系结构,微指令等优先

10、了解Firmware或有基于UART/JTAG等的系统验证工具使用经验的优先

· 【社招】DCU AI芯片架构师

工作地点:上海/成都

职责描述:

1. 熟悉目前流行的AI 网络算法,协同硬件工程师编写model (c/c++/python 任意一种)

2. 验证c/c++ or python model。

3. 协同硬件工程师,完成性能分析。

4. 跟踪AI发展趋势.

· 【社招】DCU Kernel Mode Driver(KMD)工程师

工作地点:上海/成都

工作内容/职位描述:

--设计,实现,维护DCU Kernel Mode Driver

--与硬件组合作完成新一代芯片的KMD bringup工作

--分析KMD的各方面性能,提出有效的改进方案

--支持客户需求,解决KMD相关的bug

任职要求:

--计算机,电子工程,通信或相关专业,本科及以上

--3年及以上工作经验(主管工程师5年及以上工作经验)

--有较强的解决问题能力和良好的沟通能力

--精通C/C++语言

--熟悉Linux driver开发,如内存管理,任务调度等

--具备以下至少一个知识或能力:

--具有GPU Kernel Model Driver开发经验

--具有ROCm GPU计算平台开发经验优先

--熟悉X86体系架构或PCIe总线等

--熟悉GPU架构或计算机图形学

· 【社招】 Full Chip Timing Engineer

工作地点:北京/上海/成都/苏州

岗位职责

1、分析CPU/GPU full chip timing,并负责最终的时序收敛(timing/DRV/noise等)

2、分析不同功能/DFT clock 结构,给full chip clock的balance提供指导

3、约束跨时钟域的电路,并检查跨时钟域电路可能存在的timing风险

4、检查一些IP/设计存在的特殊的时序要求并signoff5、协助前端验证SDC存在的问题。协助signoff guideline team指定最终STA相关signoff 标准

任职要求

1、2年以上数字后端工作经验

2、熟练使用数字后端流程相关EDA工具,如DC/PT/ICC2等

3、深入理解时序收敛的相关知识,比如SDC定义,OCV, signal integrity, signoff corner等

4、了解基本的DFT设计,比如scan shift/capture/bist等

5、了解前端设计的一些基本结构,比如跨时钟域设计/reset设计等

6、熟悉python/perl/tcl/shell一种或多种脚本语言

7、拥有钻研精神和良好的沟通能力

· 【社招】 物理实现工程师

工作职责

1. Implements block level physical design, including floorplan, placement, CTS , routing, parasitic extraction, STA, Power analysis, Xtalk analysis, physical verification and ECO.

2. Solves block level timing, congestion, and IR/EM issues

3. Work with full chip engineers to achieve timing closure for both partition and full chip level

任职要求

1. Bachelor or Master Degree in Engineering (Microelectronics, Electronics)

2. 2+ years of hands on experience in large scale ASIC chip physical design

3. Experienced with common EDA tools flow, ie: ICC/Innovus/Prime Time/Calibre

4. Successful tape out experience is a plus

5. Good teamwork and communication skills

6. Familiar with scripting/programming (TCL, Perl, shell script, C)

7. Language: Good English read/write

投递方式

简历投递操作流程:

登录研分网→注册→分类选择就业信息→选择企业内推→挑选企业与职位→上传附件并进行备注→投递成功

注:以企业-姓名-学校-岗位(期望城市)命名 如:海光-小明-清华大学-模拟电路工程师(上海)。岗位信息与所投岗位名称一致,并且在备注一栏备注与简历命名一样的信息,防止上传简历出错。

如果您是企业HR或员工,有招聘和内推需要请扫描下方二维码与我联系: