Ding~“芯”闻时间! 芯闻第二十二期直通车来啦!

![]() 戳上面的蓝字关注我们哦!

戳上面的蓝字关注我们哦!

资讯导航

ISSCC 2021关注

近日, ISSCC 2021以线上形式举行。本次大会的主题为“集成智能是系统的未来(Integrated Intelligence is the Future of Systems)”,分为创新(Innovation)、探索(Exploration)、教育(Education)等三部分,包括205场技术报告,6场论坛,12个短课程。

本次会议清华大学分别在“从云到端的机器学习处理器(ML Processors From Cloud to Edge)”“用于通讯和雷达的毫米波收发器(mm-Wave Transceivers for Communication and Radar)”“用于深度神经网络的存内计算处理器(Compute-in-Memory Processors for Deep Neural Networks)”“高性能VCOs(High-Performance VCOs)”及“离散时间ADC(Discrete-Time ADCs)”等细分领域发表六篇论文。以下是论文的简要介绍:

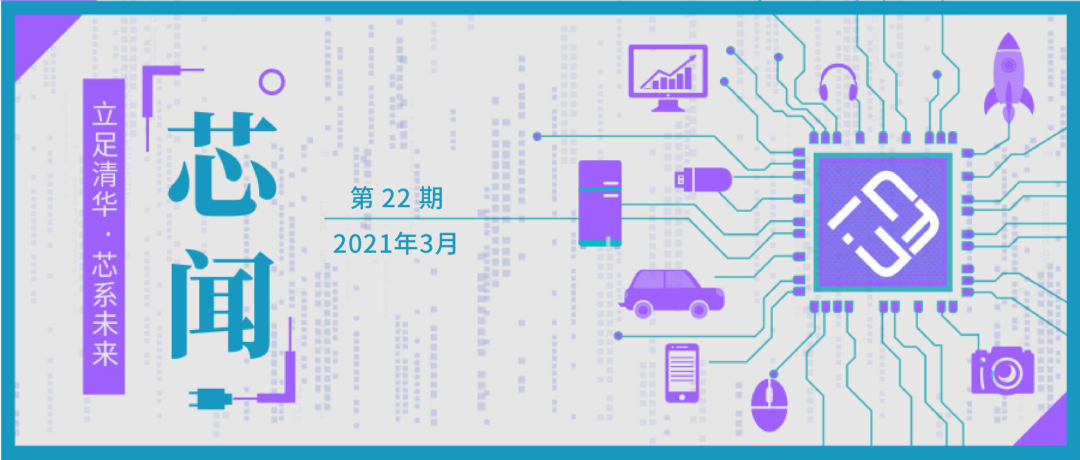

量化卷积神经网络(CNN)加速芯片——QNAP

魏少军、刘雷波教授等发布了一款量化卷积神经网络(CNN)加速芯片——QNAP,通过挖掘量化后CNN模型权值大量冗余的特征,提出一种能够显著减少冗余权值造成冗余乘操作的优化方法,降低了硬件功耗;同时,还提出了一种减少ReLU激活函数造成冗余乘加操作的预测方法,显著提升了CNN硬件的运行性能;此外,针对广泛使用的残差结构,提出了一种专用的流水结构,减少了残差结构中大量的片外访存操作。

基于TSCM 28 nm工艺,QNAP芯片仅消耗1.9 mm2的面积就实现了高达12.1 TOPS/W的能效,显著优于已有结果。本工作相关成果以“A 28nm 12.1TOPS/W Dual-Mode CNN Processor Using Effective-Weight-Based Convolution and Error-Compensation-Based Prediction”为题发表,第一作者为微纳电子系博士生莫汇宇。

QNAP芯片及其硬件指标

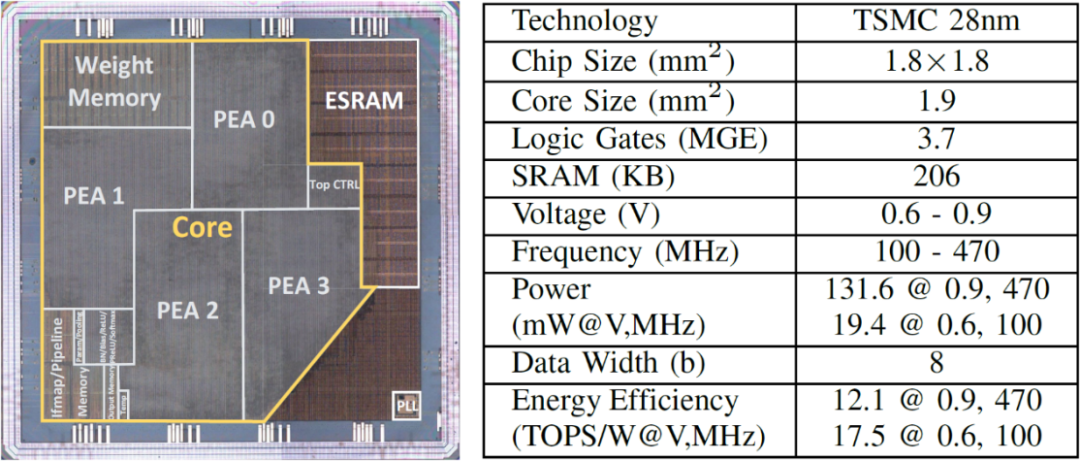

王燕教授等针对毫米波段相控阵收发机前端芯片面临的收发开关插入损耗过大,移相器和衰减器的分辨率受限,移相器/衰减器的附加增益/相位变化过大等三大挑战展开研究,提出一种全新的适用于毫米波以及更高频段的各模块电路实现方式,发布了一款能支持毫米波频段通信,雷达以及成像等应用的高性能双向W-band相控阵收发机前端芯片。该芯片采用低成本的65nm CMOS工艺实现,在国际上首次实现了W-band的收发开关,移相器和衰减器的全集成,同时实现了国际已发表工作中最高的8.9-bit移相位数,6-bit增益控制位数以及9.5dBm单通道输出1dB压缩点和12.3%的峰值功率附加效率。相关成果以“A 1V W-Band Bidirectional Transceiver Front-End with <1dB T/R Switch Loss, <1°/dB Phase/Gain Resolution and 12.3% TX PAE at 15.1dBm Output Power in 65nm CMOS Technology”为题发表,第一作者为微纳电子系博士后朱伟。

高性能双向W-band相控阵收发机前端芯片显微照片

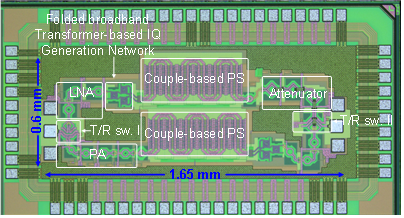

存内计算神经网络处理器芯片

杨华中、刘勇攀教授等针对传统存内计算架构计算资源浪费、系统性能损耗严重等挑战发布了一款利用TSMC 65nm工艺流片的存内计算神经网络处理器芯片。该芯片的关键技术包括:组相联分块结构化稀疏跳零架构,将神经网络模型的权重训练为分组分块的结构化稀疏形式,并编译组织为非零数据和索引值,芯片依据索引值动态决定计算位置,自动跳过零值数据对应的计算,实现同时节省功耗、存储空间并加速计算;乒乓存内计算电路结构采用两组存储单元共用一组存内计算电路的方式,在一组存储单元用于计算的同时,另一组存储单元用于权重更新及下一次计算任务的执行,从而隐藏更新权重所需的额外时间,提升系统效率。此外,处理器的高能效存内计算核心不仅实现了乒乓电路结构,而且可以利用数字电路预测器判断输出结果所需的ADC精度,动态调整ADC采样精度模式而降低功耗。该芯片实现了对于Cifar-10和ImageNet数据集上多种网络模型的支持,及最高370TOPS/W的核心峰值能效和最高75.9TOPS/W的系统峰值能效,较当前国际领先的存内计算系统芯片能效提升了6.35倍,相关成果以“A 2.75-to-75.9TOPS/W Computing-in-Memory NN Processor Supporting Set-Associate Block-Wise Zero Skipping and Ping-Pong CIM with Simultaneous Computation and Weight Updating”为题发表,第一作者为电子工程系博士生岳金山。

存内计算神经网络处理器芯片及硬件指标

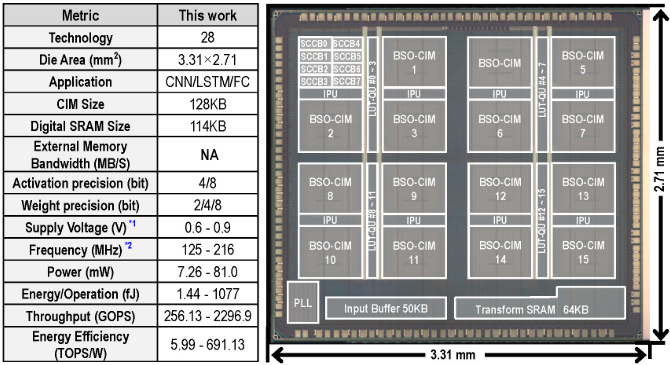

利用位级稀疏和量化优化的张量链存内计算芯片

魏少军、尹首一教授等对当前神经网络模型通常超过片上存储容量而引入的片外访存所导致CIM 处理器重现“存储墙”瓶颈这一现象,采用“计算换存储”思想,应用张量链分解算法(tensor-train, TT)将三维卷积核分解成若干个规整的四维TT核,从而将模型全部压缩、存储在CIM宏阵列中。该工作将四维TT核高效地映射入二维CIM架构,通过优化计算数据流来调度CIM的高计算并行度、减少计算过程的乘法操作;将TT核的元素进行1、2补码混合编码而增加其位级稀疏度,对应地设计了位级稀疏优化的CIM宏单元来降低其模拟计算功耗;将激励数据量化为4/8-bit两种表达,从而缩减CIM单元对多比特激励的位串行计算周期,对应地设计了基于查找表的量化单元取代高位宽乘法器来降低量化操作功耗。芯片在TSMC 28nm工艺上成功流片,通过将完整的神经网络固定在CIM宏阵列而避免了片外、片上的权重访存,显著地提升了能效。相关成果以“A 5.99-to-691.1TOPS/W Tensor-Train In-Memory-Computing Processor Using Bit-Level-Sparsity-Based Optimization and Variable-Precision Quantization”为题发表,第一作者为微纳电子系博士生郭瑞琦。

TT@CIM芯片及其硬件指标

TT@CIM芯片及其硬件指标

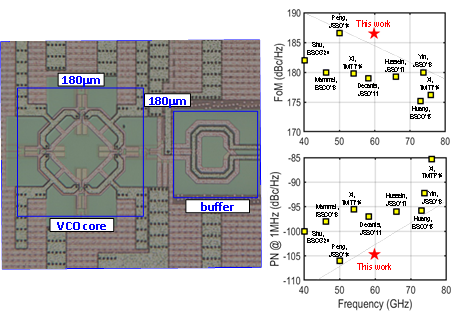

高性能CMOS基频振荡器

王志华、池保勇教授等针对当前基频振荡器的相位噪声性能受限于硅基工艺晶体管的有限增益和片上电感的插入损耗,难以满足5G毫米波通信中高阶数字调制需求的挑战,深入分析了高频片上电感的品质因子降低机理,针对性地提出环状的电感结构,消除了小尺寸电感内径负耦合,大大提高了电感的品质因子。同时,采用三线圈变压器将4个振荡器核耦合在一起,使相位噪声得到额外6dB的降低。团队发布的振荡器采用65nm的CMOS工艺设计和制造,振荡在60GHz,在1MHz频偏处的相位噪声为-104.7dBc/Hz,是目前文献中工作在类似频段的相位噪声性能最好的CMOS基频振荡器,由于其设计简洁、面积小、性能优异,该振荡器结构有望在5G毫米波通信中得到广泛应用。工作成果以“A 60GHz 186.5dBc/Hz FoM Quad-Core Fundamental VCO Using Circular Triple-Coupled Transformer with No Mode Ambiguity in 65nm CMOS”为题发表,第一作者为微纳电子系助理教授贾海昆。

振荡器的芯片以及与世界先进水平的对比

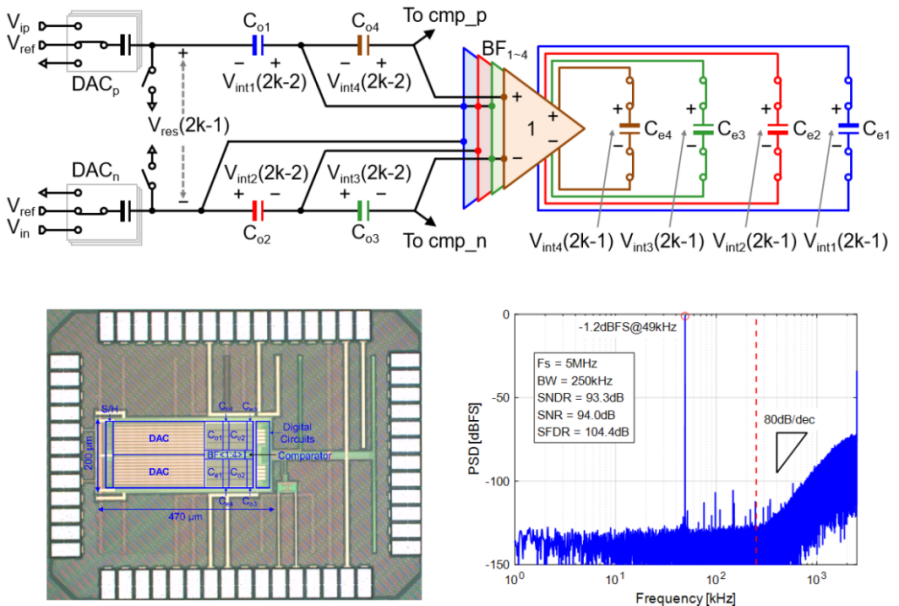

四阶噪声整形SAR ADC芯片

孙楠教授等提出了一种全新的离散时间积分器技术,通过电容叠加和动态缓冲实现积分,有效地避免了无源积分导致的信号衰减问题,并且不需要运算放大器等电路。与现有的几种积分器相比,该技术具有PVT鲁棒性高、信号损耗小、电路实现简单、高阶扩展性好等优点。基于该积分器实现的一款四阶噪声整形SAR ADC芯片,在250kHz带宽内达到了93dB的SNDR,功耗为340uW,能效品质因数为182dB。该芯片是目前首款实现90dB以上精度和100kHz以上带宽的噪声整形SAR ADC芯片。相关成果以“ A 250kHz-BW 93dB-SNDR 4th-Order Noise-Shaping SAR Using Capacitor Stacking and Dynamic Buffering ”为题发表,第一作者为电子工程系博士后刘佳欣。

ADC芯片架构图(上)、照片(左下)及测试频谱(右下)

ADC芯片架构图(上)、照片(左下)及测试频谱(右下)

在ISSCC2021会议的开幕演讲中,台积电董事长刘德音以“揭秘创新未来”为主题,谈及许多引领芯片发展的创新技术,尤其是半导体工艺节点不断推进的关键技术。

针对芯片技术进步正在放缓的观点,刘德音表示,根据台积电的产品数据,在相同速度或速度增益、相同的功耗和逻辑密度下,功耗降低的速度保持不变。台积电3nm进展顺利,甚至比预期进度超前。与目前最先进的商用5nm芯片相比,3nm芯片的逻辑密度将提高75%,效率提高15%,功耗降低30%。3nm芯片将于今年晚些时候试产,预计将在2022年下半年开始商业化生产。

实际上,台积电半导体制造能够引领业界得益于众多技术的不断创新,包括EUV、新晶体管、新材料、芯片封装、小芯片、系统架构等。在演讲中刘德音提到,台积电在5nm节点引入一种高迁移率沟道(high mobility channel,HMC)晶体管,将锗整合到晶体管的鳍片(Fin)中,而导线也利用钴与钌材料来持续挑战物理极限;在3nm制程之后,台积电将在其2nm制程中采用更复杂的环绕栅极晶体管(gate-all-around,GAA)的纳米片(nanosheet)结构,提供相较FinFET更强的载流能力,持续优化芯片性能和功耗。与前几代技术相比,纳米片晶体管实现了减少漏端引入的势垒降低(DIBL效应)和更好的亚阈值摆幅(subthreshold swing),以提高电路性能,为SRAM带来更低的供电电压,可提供0.46V的可靠快取操作。

除此之外,刘德音也在报告中展示了台积电在EUV电源功率、技术设计协同优化、低维半导体材料、小芯片、SoIC等方面的进展。

点击文末“阅读原文”,前往“芯闻”网页版:)

长按下方二维码,关注官方微信。

未来芯片高精尖中心

微信号:THU-ICFC