EETOPEETOP半导体社区-国内知名的半导体行业媒体、半导体论坛、IC论坛、集成电路论坛、电子工程师博客、工程师BBS(150万论坛会员)。 www.eetop.cn bbs.eetop.cn edu.eetop.cn

528篇原创内容

公众号

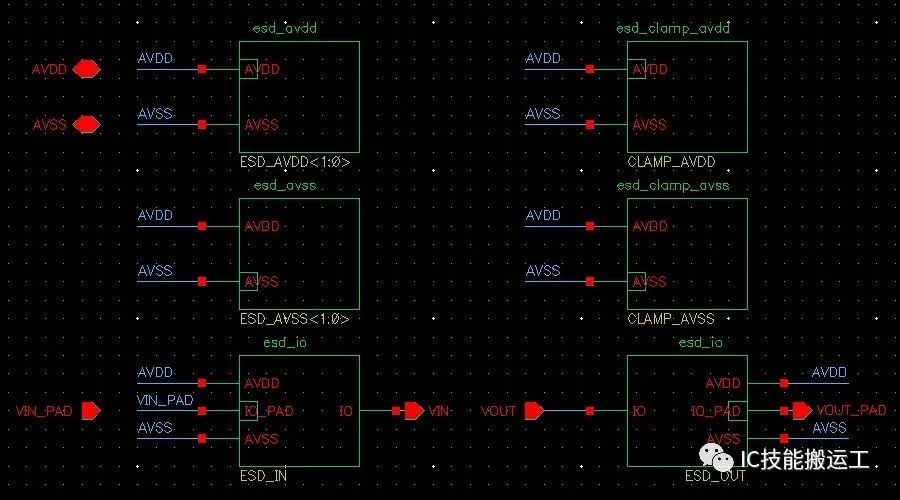

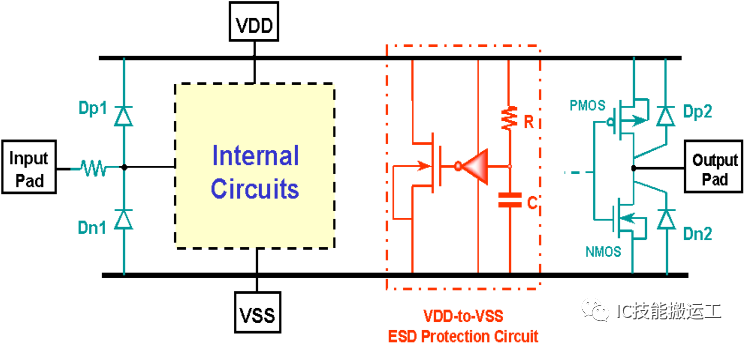

上面图(a)中是最常见的ESD保护电路,在很多场合都有见到过;图(b)中是CMOS工艺中最常见的ESD保护电路,这种接法叫做GGNMOS(Gate Grounded NMOS),利用寄生的BJT实现ESD保护功能;图(c)中是利用可控硅实现ESD保护功能;图(d)与图(b)中原理一致。

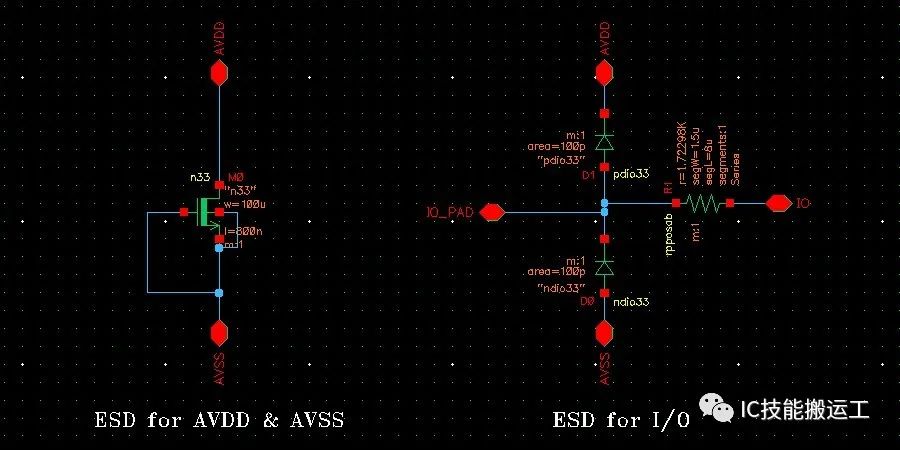

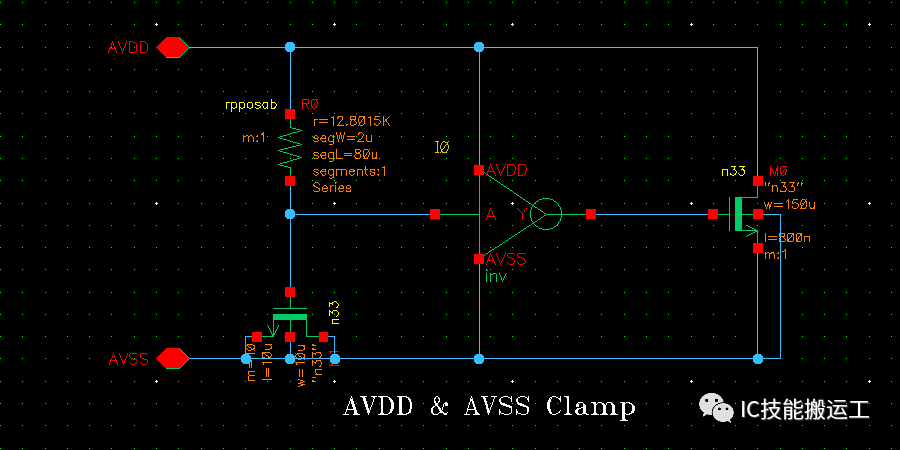

除了I/O中ESD保护电路外,电源和地也需要相应的保护电路,电源和地之间需要clamp电路,为了安全,也会搭配GGNMOS作为保护。

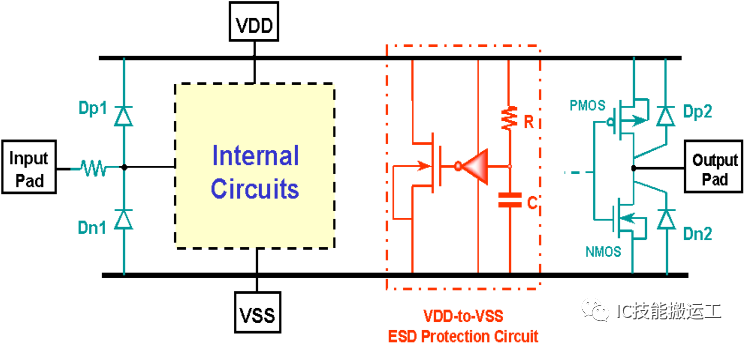

上图是全芯片ESD保护电路的一种,其中红色虚线标注的是电源clamp电路,在设计时需要根据具体的ESD要求选择RC网络的时间常数以及ESD泄放管子的尺寸。

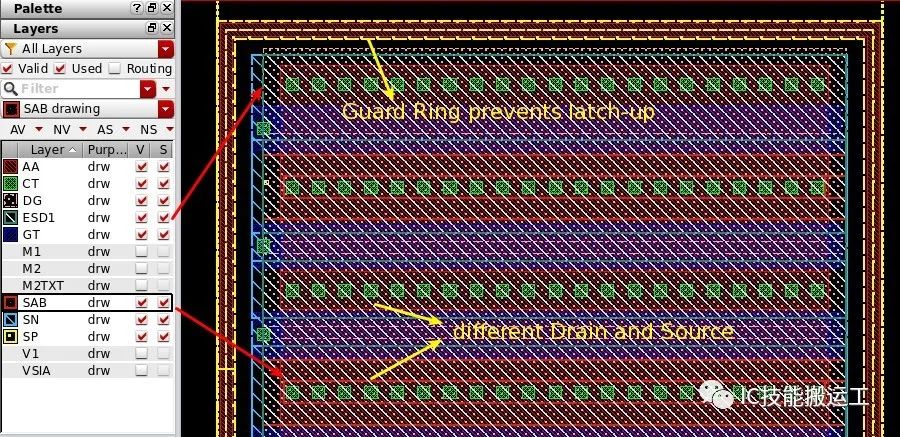

以上电路中使用的器件都是专门的ESD器件,通常PDK中也应该包含ESD设计专用的器件,这些器件针对ESD防护功能做了工艺处理,相比于非ESD器件具有更好的抗ESD能力,而且仿真模型与普通器件也会有区别。如果使用的PDK内没有专门的ESD器件,那么在电路版图设计中需要特别留意,ESD器件因为加工中与普通逻辑器件有一些工艺上的不同,所以相比于逻辑器件会多一些工艺层,这些在版图设计中需要考虑到。

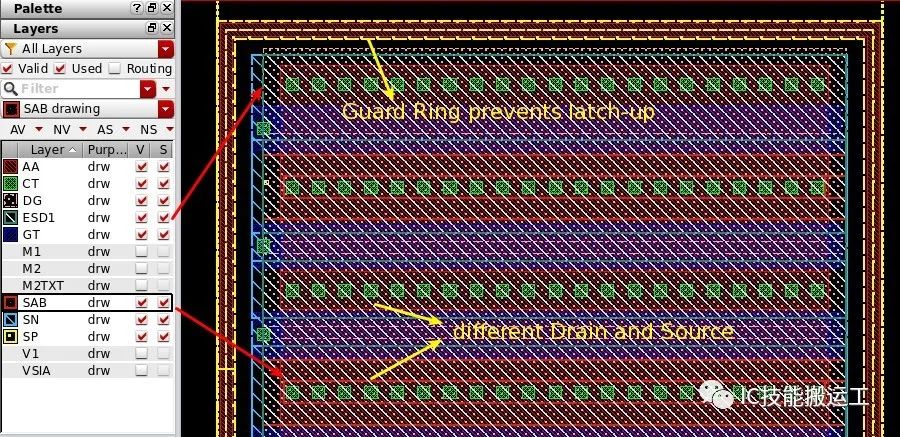

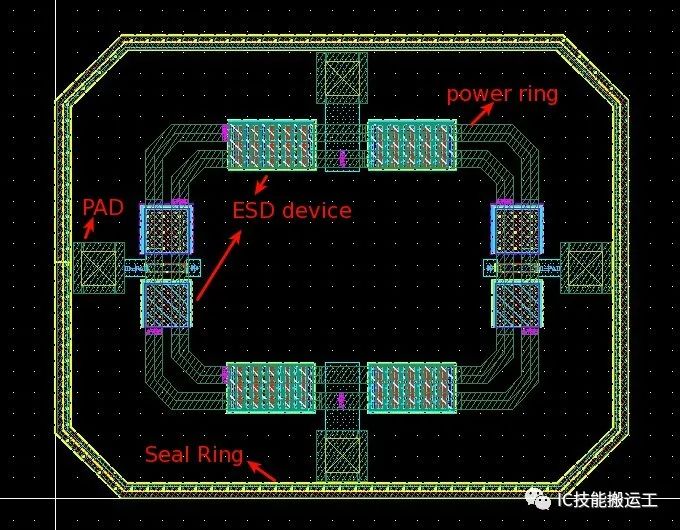

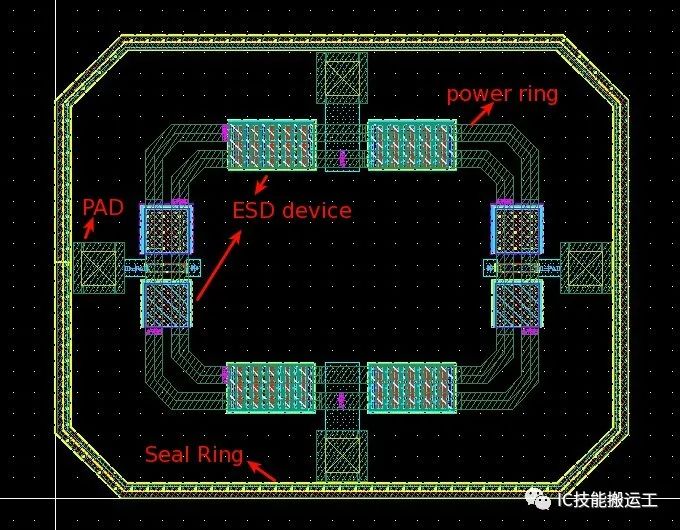

以上是小目同学使用的工艺中用来做ESD保护的NMOS实现需要用的版图层,不同工艺可能有不同的实现方法,在有些工艺中还可以添加标识层实现LDD工艺等。由于ESD器件尺寸都很大,很容易导致闩锁效应(latch-up),为了防止latch-up产生,对于单个ESD器件的尺寸有一定限制,同时版图中最好加上有效的隔离环,或者采用隔离阱将ESD器件放在单独的阱中。上图中是作为演示,小目同学设计的简单ESD电路图。ESD保护电路在电路设计时被划分在PAD Ring模块,该模块包含所有与PAD有关的电路设计,在版图上该部分包含芯片电源网络的设计以及封装方式的考虑。

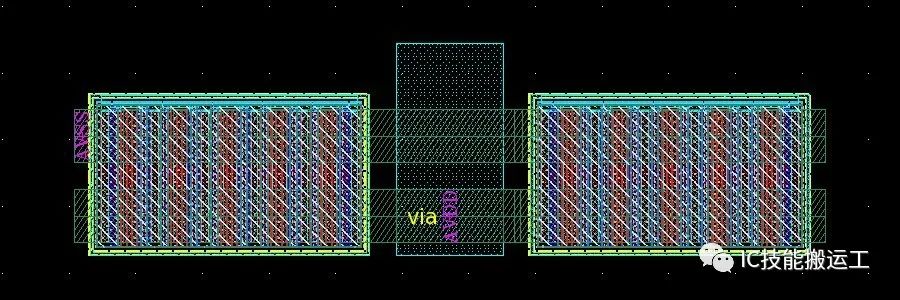

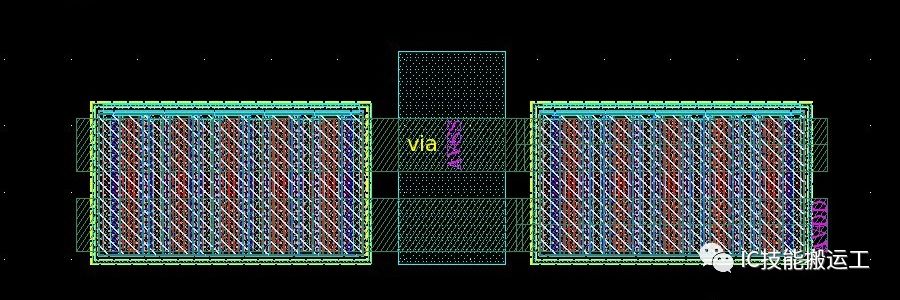

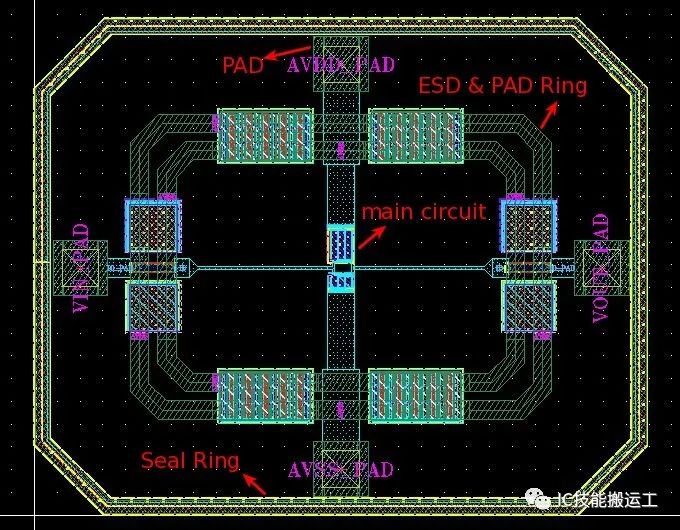

下图中是对应原理图的版图部分,由于时间问题,电源clamp电路的版图并没有给出具体实现,基本上与其他电路一致,只需要注意ESD泄放路径的规划即可。ESD保护电路设计完成之后,就是PAD规划和芯片电源网络规划,这一部分需要根据设计需求灵活变通,良好的PAD规划一方面可以节省芯片面积,另一方面也可以减少电路互连难度。

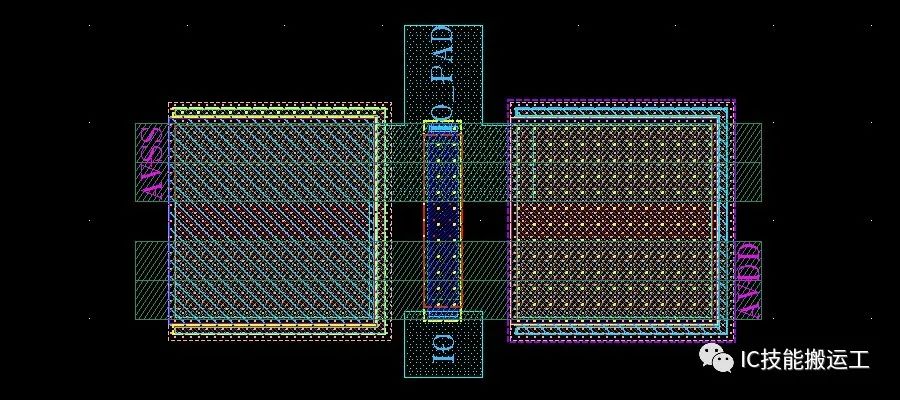

以上版图实现只是为了做演示,并没有经过仔细的仿真和验证,所以器件尺寸请大家不要过于纠结。并且为了容易观察,上面版图中PAD尺寸也没有按照要求来画,实际电路中,PAD尺寸都有严格要求。PAD Ring部分在设计项目中十分重要,包括整个芯片的电源网络都在这部分完成,因此也会占据很大一部分芯片面积。在先进工艺设计中,核心电路的尺寸可能一直在减小,但是由于电源线宽、PAD尺寸、ESD保护电路尺寸等限制,PAD Ring的尺寸并没有按比例减小。在很多设计中为了节省PAD Ring面积,会把PAD放在某些电路上面,以节约一部分芯片面积,具体PAD Ring的实现与设计规则、封装方式等都密切相关。

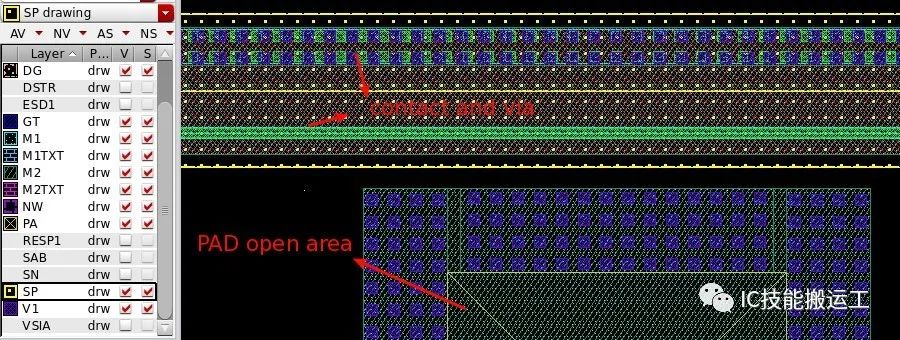

在整个芯片的外围,一般还要求放置一圈Seal Ring,它的最根本也是最主要的作用就是防止芯片在切割的时候受到机械应力损伤,如果把Seal Ring接地,也可以起到屏蔽芯片外干扰的作用,另外Seal Ring可以防止潮气从侧面断口侵入芯片,对静电保护也有一定的作用。Seal Ring是一种氧化、钝化层结构,在版图上Seal Ring是一个由离子注入、过孔、金属等各层按照一定的规则叠加实现的。特别是过孔在Seal Ring上的实现可能和其它电路中不一致,所以大部分工艺针对Seal Ring有相应的设计规则。设计人员可以根据自己的需要在版图外围添加Seal Ring,有些代工厂也可以为版图添加Seal Ring.下图中是PAD的版图设计和Seal Ring中长条形过孔设计,根据不同工艺有不同的设计方法。由于反相器电路十分简单,所以可以看到实际反相器电路只占整个芯片版图的很少一部分,下图中芯片版图看着可能有些失调,但却是一个完整的模拟电路芯片版图。当然,以上只是为了作为演示作用,实际芯片设计中尺寸需要根据封装提前确定方案,对于核心电路尺寸极小的电路,PAD Ring尺寸并不会太小,否则无法完成芯片封装,那么设计也没有意义。对于大面积空白的芯片,DRC结果无法通过,因为工艺加工对整个芯片的各个层密度有一定要求,这时候可以在空白处添加MOS电容,作为片上电容使用,也可以使用脚本或者手动添加dummy图形,直到DRC满足规则要求。完成芯片的所有电路、版图、规则检查以及后仿工作之后,电路设计工作就到此结束了,剩下的工作就是和工艺厂沟通tapeout.

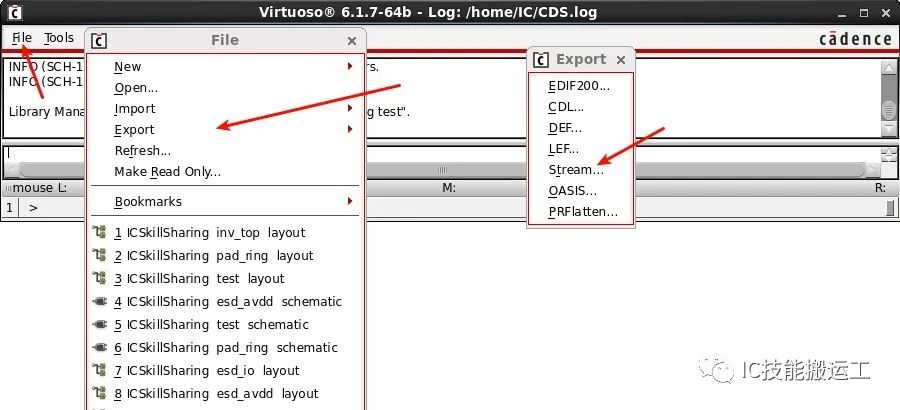

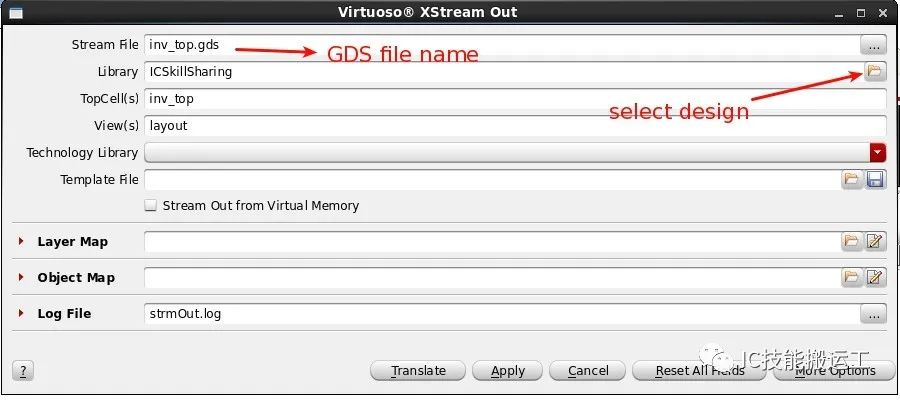

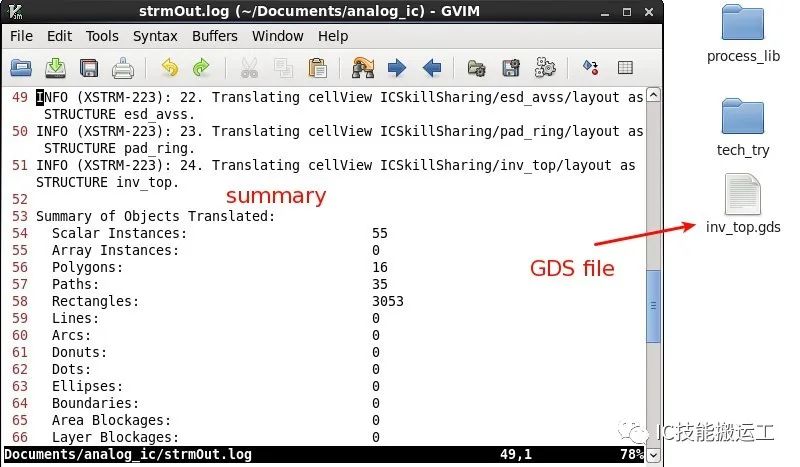

集成电路设计中项目提交并非是原理图或者版图文件,而是GDS(Graphic Data System)文件,在Cadence平台设计完版图后,可以直接导出GDS文件以交付给代工厂,具体步骤如下所示。在CIW界面,选择:File->Export->Stream, 之后会弹出对话窗口,点击Library一栏处索引按钮,找到对应设计的Library, Cell, View并正确填写生成文件的名称,然后开始版图转换。运行完毕会在Cadence工作路径下生成相应的GDS文件,tapeout时只需要按照要求将相应的GDS文件交付给代工厂即可。终于,关于模拟集成电路设计流程系列的分享结束了,其中有很多不详细的地方还望各位同学在阅读的过程中多加注意。

模拟集成电路的设计内容博大精深,仅仅凭几次的分享很难也不可能涵盖很多,希望以上分享能起到抛砖引玉的作用,更多内容只有在项目实践中慢慢体会,期待大家一起学习、一起进步,如有问题及时反馈。相关阅读: