先进封装,看这一篇就够了!

国际半导体技术路线图(ITRS)明确提出未来集成电路技术发展的两个方向:一是More Moore(延续摩尔定律),二是More than Moore(拓展摩尔定律)。沿着拓展摩尔定律方向发展的技术路线,更关注将多种功能芯片集成在一个系统中。

业界普遍认为,先进封装会成为下一阶段半导体技术的重要发展方向。随着摩尔定律发展趋缓,通过先进封装技术来满足系统微型化、多功能化成为了集成电路产业发展的新引擎。

谈到先进封装技术,我们先了解一下什么是封装

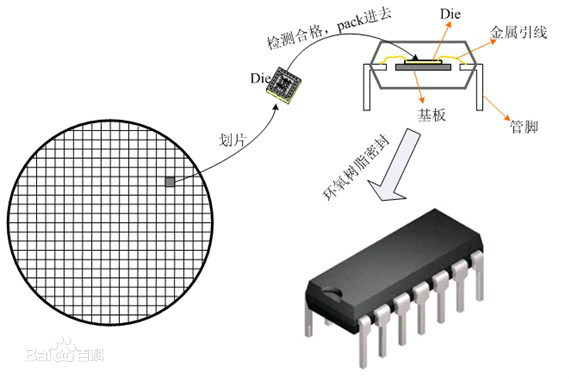

封装,简而言之就是把晶圆厂(Foundry)生产出来的集成电路裸片(Die)放到一块起承载作用的基板上,用引线将Die上的集成电路与管脚互连,再把管脚引出来,然后固定包装成为一个整体。它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。因此,封装对CPU和其他大规模集成电路而言,非常重要。

封装技术是伴随集成电路发明应运而生的,主要功能是完成电源分配、信号分配、散热和物理保护。而随着芯片技术的发展,封装技术也在不断革新。

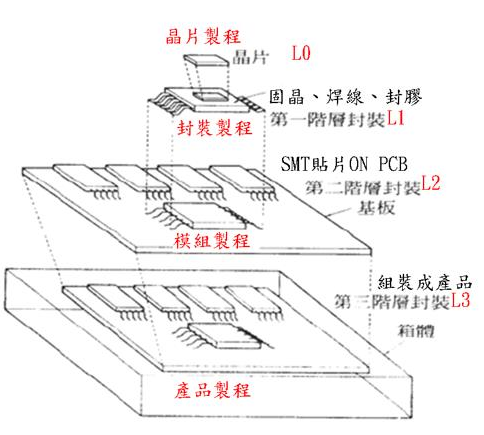

封装的分级

封装一般可以分为芯片级封装(0级封装)、元器件级封装(1级封装)、板卡级封装(2级封装)和整机级封装(3级封装)。本文中介绍的封装主要是指1级封装。

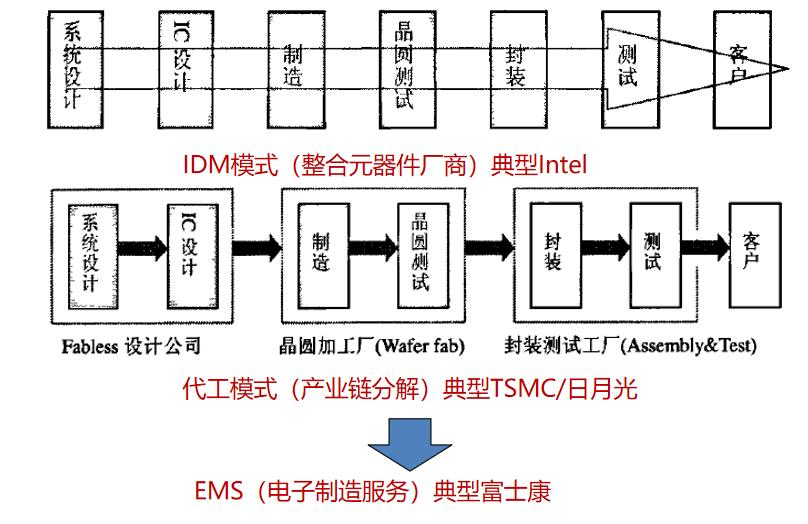

全球封装测试业的主要运营模式

按照实际运营情况,全球封测企业主要分为两类,第一类是从属于IDM(垂直整合器件制造商)的封测厂,第二类是独立的封测代工厂。IDM公司拥有自己的集成电路产品,所属的封测厂通常为自有集成电路产品服务;封测代工厂完全没有自己的集成电路产品,纯粹为其他公司提供封装和测试服务。

IDM制造商自身具有从集成电路设计、制造到封装测试的完整产业链,而封测代工厂则需要通过与Fabless公司(无生产线的集成电路设计企业)和晶圆代工厂形成完整的产业链,从而实现自身的运营。

然而,IDM自有的封测厂也有可能为其他设计公司或晶圆制造厂提供代工服务。就在3月23日,美国半导体巨头——英特尔新任CEO——基辛格(Pat Gelsinger)宣布,英特尔将在美国亚利桑那州斥资近200亿美元打造2座芯片工厂。数月前,英特尔还在研究芯片委外代工,改变设计与生产不分家的做法,如今却宣示要切入晶圆代工,策略180度大转变,实际上是要抓住芯片需求大爆发的商机,在全球芯片短缺、芯片生产炙手可热之际,展开晶圆代工事业。

传统封装

先进封装是相对传统封装所提出的概念。因此在介绍先进封装之前,首先要介绍传统封装。

传统封装,通常是指先将圆片切割成单个芯片,再进行封装的工艺形式。主要包含SIP、DIP、SOP、SOT、TO、QFP、QFN、DFN、BGA等封装形式。传统的封装形式主要是利用引线框架作为载体,采用引线键合互连的形式。

SIP

(Single In-line Package,单列直插封装)

DIP

(Duel In-line Package,双列直插封装)

SOP

(Small Outline Package,小外形封装)

SOT

(Small Outline Transistor,小外形晶体管封装)

在市场需求的推动下,传统封装不断创新、演变,出现了各种新型的封装结构。随着电子产品及设备的高速化、小型化、系统化、低成本化的要求不断提高,传统封装的局限性也越来越突出,需求数量在不断下降,但由于其封装结构简单、制造成本较低,目前仍具有一定的市场空间。

先进封装

先进封装是指处于当时最前沿的封装形式和技术。目前,带有倒装芯片(Flip Chip,FC)结构的封装、圆片级封装(Wafer Level Package,WLP)、2.5D封装、3D封装等被认为属于先进封装的范畴。

倒装芯片结构封装(Flip Chip,FC)

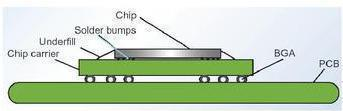

带有倒装芯片结构的封装是先在芯片上制作金属凸点,然后将芯片面朝下利用焊料直接与基板互连,通常会使用底部填充(Under Fill)树脂对热应力进行再分布来提高可靠性。其优点是封装面积小,引线互连长度缩短,I/O端口数量增加。

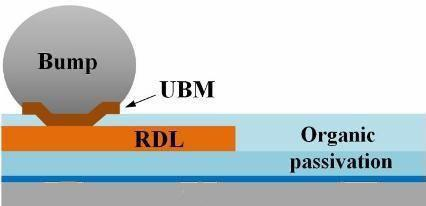

圆片级封装(Wafer Level Package,WLP)

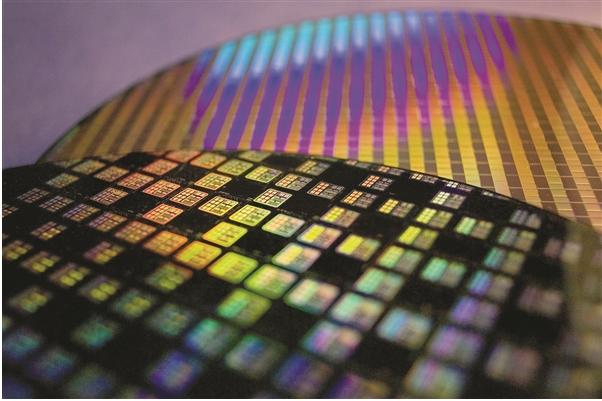

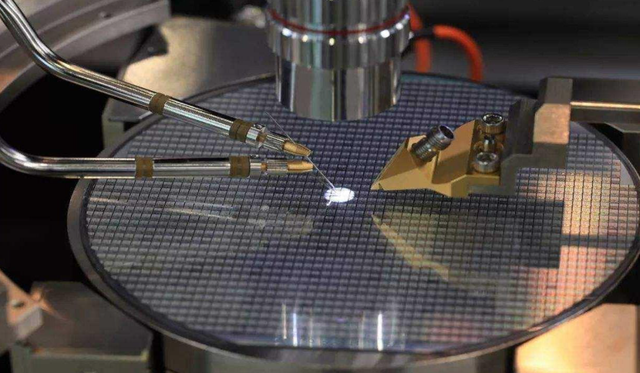

圆片级封装是直接以圆片为加工对象,同时对圆片上的众多芯片进行封装及测试,最后切割成单颗产品,可以直接贴装到基板或PCB上,是当前封装领域的热点之一。其优点是封装产品轻薄短小,信号传输路径更短。目前多用于低引脚数的消费类可携式产品(包括模拟/混合信号、无线连接、汽车电子等),可满足超薄大尺寸的存储类芯片的特性需求,在生产方面可大大提高加工效率,降低成本。

2.5D结构封装和3D结构封装

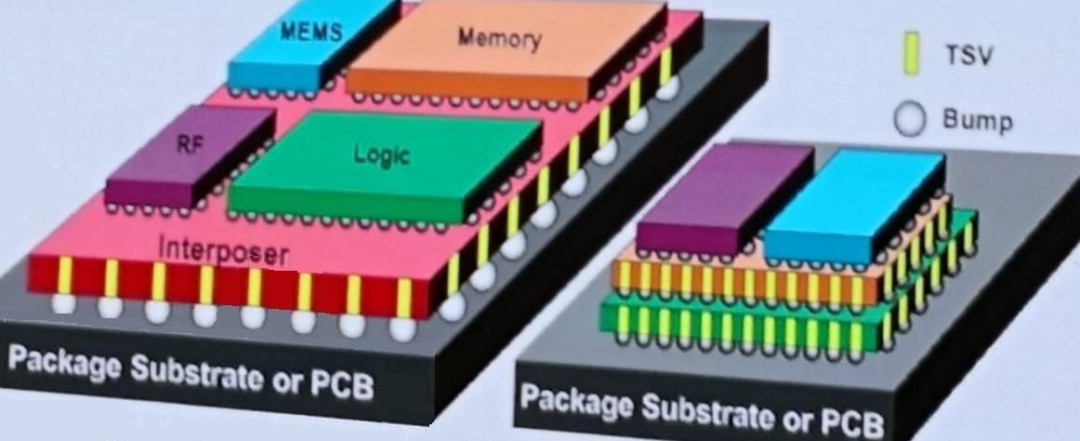

2.5D结构封装是在2D封装结构的基础上,在芯片和封装载体之间加入了一个硅中介转接层,该中介转接层上利用硅通孔(Through Silicon Via,TSV)连接其上、下表面的金属,多采用倒装芯片组装工艺。由于采用了中介转接层,其表面金属层的布线可以使用与芯片表面布线相同的工艺,使产品在容量及性能上比2D结构得到巨大提升。

3D结构封装是将芯片与芯片直接堆叠,可采用引线键合、倒装芯片或二者混合的组装工艺,也可采用硅通孔技术进行互连。3D结构进一步缩小了产品尺寸,提高了产品容量和性能。目前,散热较差、成本较高是制约TSV技术发展的主要因素。

2.5D结构封装(左)和3D结构封装(右)

先进封装已被广泛应用于计算机、通信、消费类电子、医疗、航空航天等领域,推动着封装技术以及整个电子行业向前发展。目前,倒装芯片、2.5D封装、3D封装主要用于存储器、中央处理器(CPU)、图像处理器(GPU)等;圆片级封装主要应用于功率放大器、无线连接器件、射频收发器等。

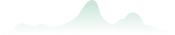

关于先进封装采用什么样的工艺流程和关键技术,以及使用哪些互连材料,我们将在后续内容中进行详细介绍。欢迎大家关注微纳互连公众号,了解更多信息。

*图片来自铟泰(Indium Corporation)

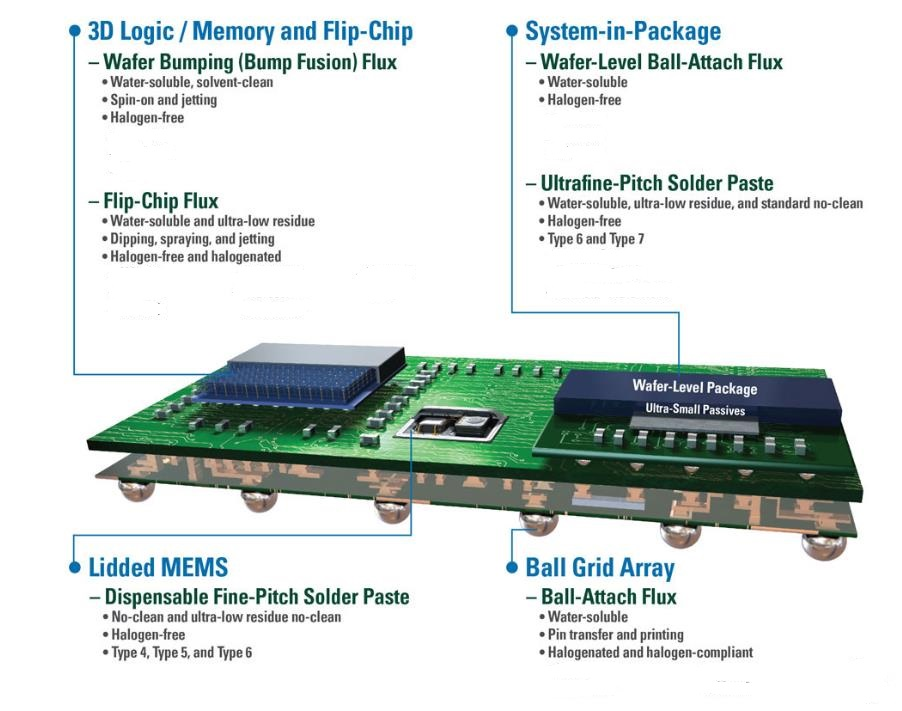

1947年,美国电报电话公司(AT&T)贝尔实验室发明了第一个晶体管,开启了电子封装时代。20世纪50年代,封装外壳以3个引脚的晶体管外形(Transistor Outline,TO)金属-封装外壳为主,之后发展为各类陶瓷、塑料封住外壳。

1958年,美国TI公司推出了世界上第一个集成电路,由此催生了多引脚封装外壳的出现。20世界60年代,出现了双列直插封装型(Dual In-line Package,DIP)陶瓷-金属引脚封装;到了70年代,DIP已经成为中小规模IC封装的系列主导形式;随着塑封DIP的出现,这种封装在大量使用的民品中被广泛应用。

20世纪70年代,IC技术飞速发展,在一个硅片上可集成211~216个晶体管,出现大规模集成电路(Large Scale Integration,LSI)。元器件集成度大幅增加,芯片尺寸不断扩大。

20世纪80年代,随着表面贴装技术的出现,各类贴装元器件封装技术日益成熟,四面引线扁平封装(Quad Flat Package,QFP)已实现标准化批量生产。随着环氧树脂材料性能的不断提升,使IC封装密度进一步提高,引脚间距越来越小、成本降低,更适于批量规模生产;塑料四面引线扁平封装(Plastic QFP,PQFP)成为80年代IC的主导封装类型。小规模IC和引脚数较少的LSI芯片采用小外形封装(Small Outline Package,SOP),成为DIP的“变形”封装形式。

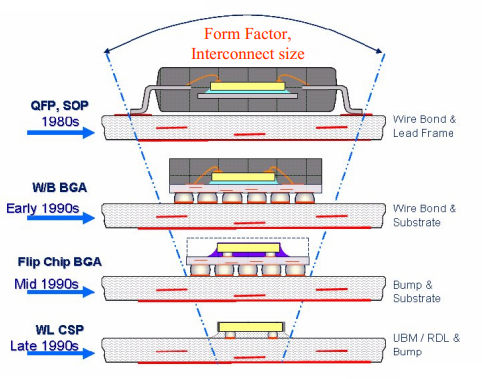

80年代至90年代,随着IC特征尺寸的减小和集成度的提高,芯片尺寸不断增大,IC发展到超大规模集成电路(Very Large Scale Integration,VLSI),在一个硅片上可集成216~222个晶体管。原有的QFP及其他类型的封装已经无法满足VLSI的要求,封装引脚由周边排列型发展成矩阵分布型。20世纪90年代,美国开发出球栅阵列封装(Ball Grid Array,BGA),其封装面积与芯片面积之比不大于1.2,因此解决了芯片小而封装大的根本矛盾。90年代末,倒装芯片技术(Flip Chip,FC)的使用,再次引发了封装技术的更迭。

进入21世纪,随着半导体技术逐渐逼近硅工艺尺寸的极限,半导体技术进入“后摩尔定律”时代,从过去着力于圆片制造工艺技术节点的推进,转向系统级设计制造封装技术的创新,先进封装技术快速发展。

封装技术及外形的发展紧跟半导体芯片制造技术进程,每一代芯片都有与之相匹配的封装技术与外形。随着电子器件朝着更短、小、轻、薄,且功能更多、集成度更高的方向发展,封装在半导体产业中的重要性将越发突出。

*免责声明:本文仅代表作者个人观点,不代表本公众号立场。本公众号转载此图文仅出于传播更多资讯之目的,如有侵权或违规请及时联系我们,我们将立刻予以删除。

投稿或推广合作:wintech@wintechm.cn