走“芯”整理 | eKnowledge知识划重点

前几期的eKnowledge集锦收获了很多小伙伴的好评。本期,让我们继续回顾有趣有料的eKnowledge文章,让您轻松get干货,助力您高效完成工作。

温馨提示:点击图片,即可跳转到对应文章哦~

ATE上单调非线性数据的二分法Trim查找算法优化

毋庸置疑,对于符合单调性的数据,二分查找法是测试工程师的首选。但是在某些情况下,测试时间成为一个备受关注的问题。例如测试芯片有多个参数需要校准,校准参数位数多;量产的芯片容量大。时间即金钱,为了较低测试成本,我们需要一个更快的校准方法。

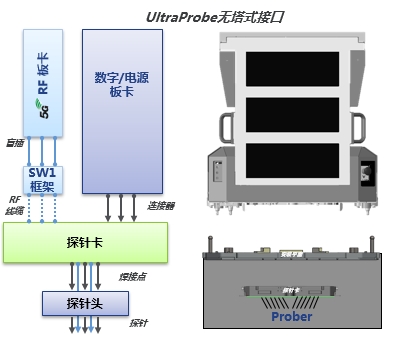

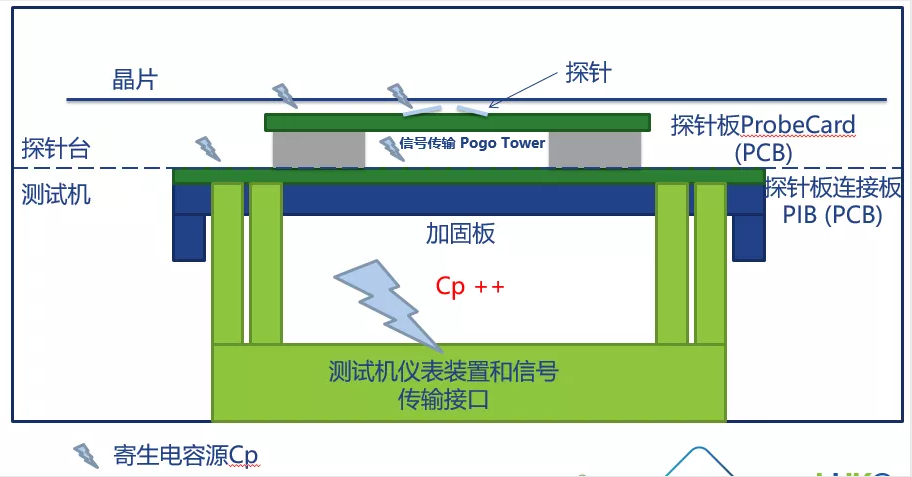

5G 毫米波半导体晶圆探针测试解决方案

数十亿5G集成芯片不仅可用于内部连接和控制设备、目标或者芯片,并且可以以超低延时和超大容量传送高达几G赫兹的信号,以获得一致的用户体验。随着实现5G无线网络的产品复杂度增加,客户因此需要高质量的测试系统和更块地量产导入。

伴随大量的RF和SOC芯片转到探针测试,因此寻找更加精准的测试接口成为晶圆测试中更快量产导入的关键因素。这篇文章中,将会介绍工业验证的5G晶圆测试的探针接口方案,包括每种探针接口方案的连接,信号质量和探针卡技术。

最大化质量监控工具的效率以加强对量产环境的支持

大批量生产环境中的测试程序可能容易受到各种妨碍生产因素的影响,例如突然的程序崩溃、测试时间的逐渐增加以及导致异常结果的编程更改。泰瑞达通过IGXL™中内置的统计分析功能提供质量监控服务,该功能收集有用的信息并监视IGXL™进程的运行状况。统计分析功能会生成两个文件“进程日志”和“事件日志”。本文将分享如何从QM日志文件中提取有价值的信息,并将STDF记录信息映射到QM日志时间戳,以确定故障期间发生了什么IGXL事件,帮助消除逐渐增加的测试时间。

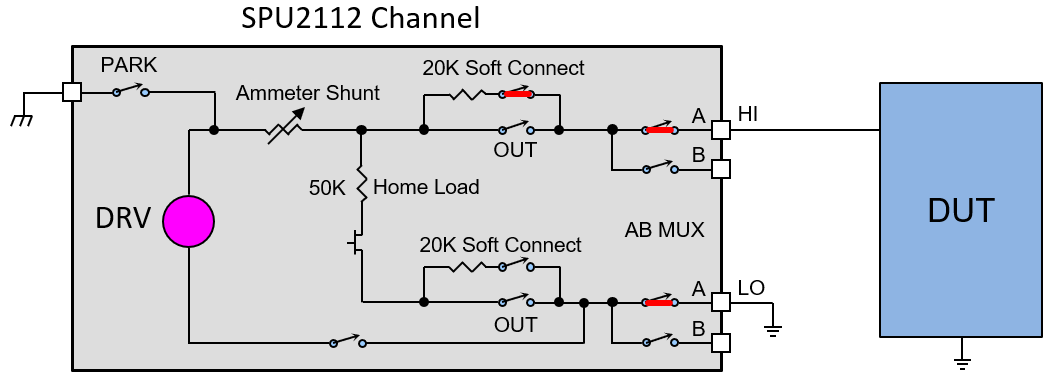

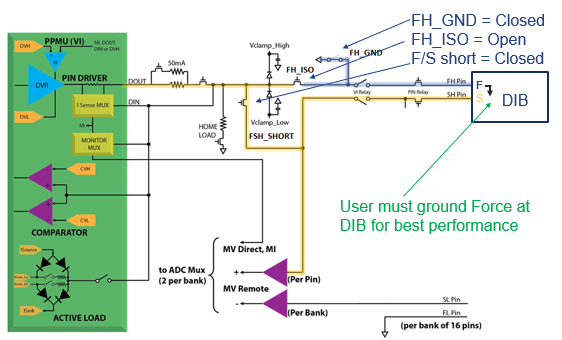

ETS-800仪器测序最佳实践

设备的复杂性和更高的站点数量正在推动越来越复杂和更高密度的ATE系统,以及越来越复杂的DUT接口板(DIB)硬件设计。这对于采用排序仪器的最佳实践来保护DUT,DIB硬件和整个测试系统变得尤为重要,因为更高的复杂性和密度意味着出现问题的可能性更大。

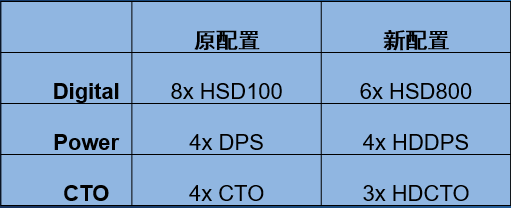

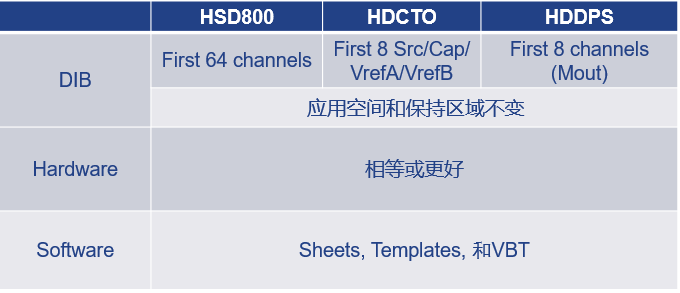

在半数板卡配置的J750EX-HD机台上使用J750探针卡

设想一下:“如果一个客户买了一台 J750Ex-HD, 但是他们最初只买了四块HSD800,三块HDCTO,两块HDDPS的板卡配置,而不是八块HSD800,四块CTO,四块DPS的板卡配置,这样导致他们无法测试当前程序。那该怎么办呢?“

本次我们将介绍一种通过有效地重整合信号线,合理利用额外密度的“反向兼容PIB”方法;通过这种方法,用户可以用一半的板子测试两倍的管脚数量;同样地,即使用户只有少量的板卡,测试人员也可以在J750上测试现有的产品。

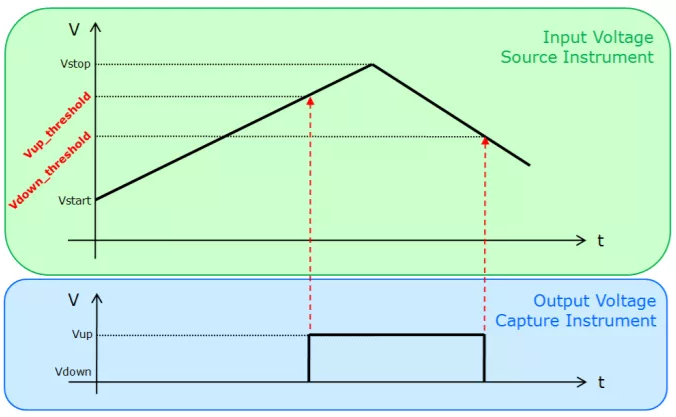

ETS-800 阈值测试项测试方法总结

阈值测试项在芯片测试中是非常常见的。阈值测试有很多种方法,比较广为人知的两种是步寻法和二分法。

这篇报告主要描述在ETS-800上,对同一个阈值测试项用,几种不同的步寻法去寻找阈值。并从测试时间,PTE,复用性,编程难度和调试难度等方面进行比较。最后我们将对ETS-800上的二分法进行简单的介绍。

本篇报告可以帮助ETS-800的使用者,在面对不同的阈值测试项时,选择合适的测试方法,并提供一些代码示例来节省开发时间。

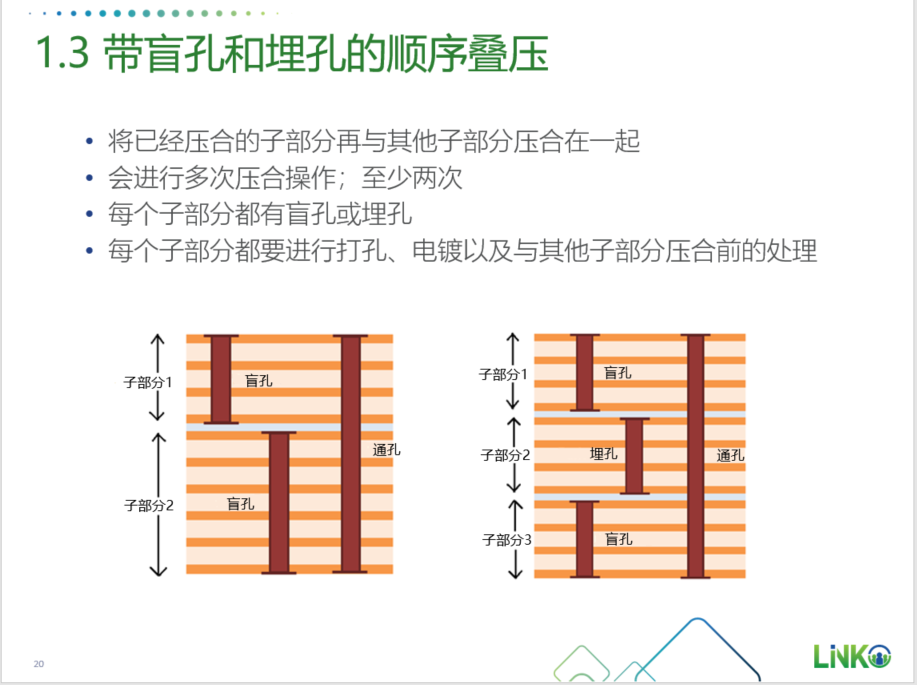

为UltraFLEX测试板选择正确的PCB叠层技术

ATE测试工程师在开发具有多site的测试板时,会面临如何选择PCB叠层技术的问题。除了经常使用的一般通孔外,还有很多更加复杂的叠层技术,例如带背钻的通孔、带翻钻的通孔、带有盲孔和埋孔的顺序叠压,带有微过孔和埋孔的密集互连叠层。

选择适合的叠层技术要考虑PCB生产中的硬件测试花费、制造周期、性能表现,还要明确所选择的叠层技术是否适配特定类型的待测芯片,如数字类、模拟类、混合信号类,电源管理类和射频类。这里会对上述四种叠层技术进行说明,并对UltraFLEX平台在板厚选择方面的灵活性进行介绍。

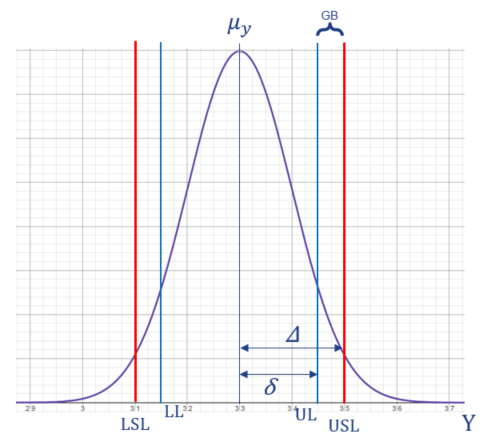

通过Guardband来设定Limit是如何影响生产质量和生产成本——Guard Banding

每次测量都会受到误差的影响:系统的和随机的。通过校准进行修正能够减少系统误差。更准确地说,重复测量(减少随机误差)并不会减少误差,但其平均值会更好地贴近实际值,从而减少偏差。

UPD64 数字回路 (DR) 模式

相较于已有方案,UPD-64(Universal Pin Digital)提供了多种新特性。本文章会选取几个重要特性加以介绍,包括D/R(DIGITAL_RETURN)模式,一种独特的信号传输策略。此特性为用户提供了两种不同的路径到DUT, 一种路径适用于高电流和模拟并得以优化,另外一种适用于高带宽数字信号。D/R模式也附带引入其它特性,包括:同步进行per-pin开尔文测量;使用VI,PPMU和时间触发器时可以选择force线还是sense线。这些特性,结合高压数字性能,使得UPD-64成为汽车电子和线性电源测试中强有力的工具。

在本文中,提到了一个案例:一个客户的待测芯片无法驱动超过10pF的电容,然而他们想要用HSD1000测试晶圆。由于容值过高,需要在多个sites上缓冲多个待测芯片IO。

使用PhotoMos和一个特殊的缓冲器,开发了一个DIB解决方案,用来缓冲或不缓冲每个待测芯片IO。该方案设计的目的是最小化DIB空间限制,并且利用数字信道来控制路径,该解决方案可以在所有测试平台上重复利用。

随着5G技术和市场的逐渐发展,个人数据传输量成倍增长,通信频率和带宽的提高,毫米波的应用场景也越来越广泛。在Sub-6G场景下,泰瑞达的Uwave24板卡可以很好的实现客户需求。而在6G以上的工作频段,为了满足5G毫米波测试的复杂需求,泰瑞达推出了全新的Uwave24扩展模块-MX44。

以上是今天的分享,希望简单小合集,能够让您有大收获。欢迎大家继续关注我们对eknowledge相关问题的解读!