关于JTAG口的知识!

1、边界测试

2、JTAG引脚

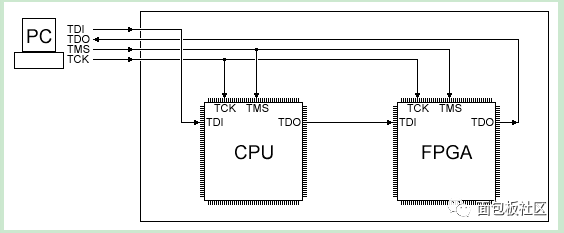

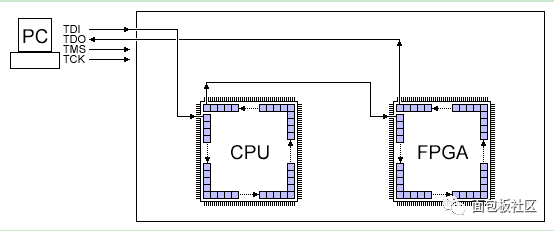

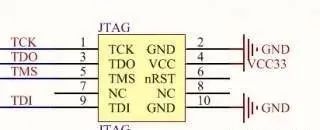

TDI:测试数据输入,数据通过TDI输入JTAG口; TDO:测试数据输出,数据通过TDO从JTAG口输出; TMS:测试模式选择,用来设置JTAG口处于某种特定的测试模式; TCK:测试时钟输入; TRST:测试复位。

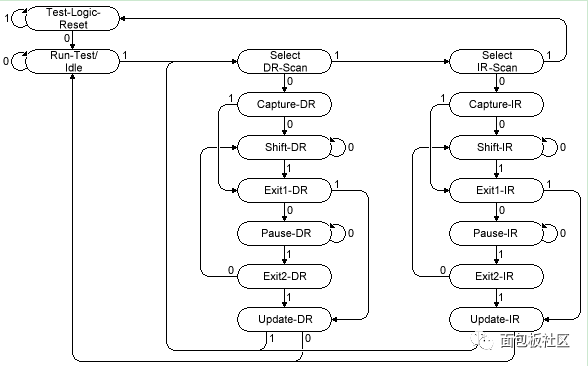

3、JTAG如何工作

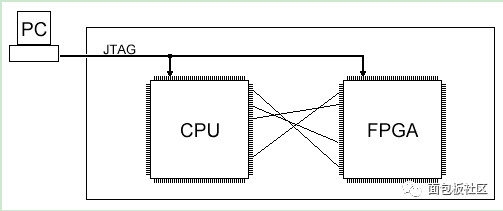

4、JTAG链相关疑问

5、边界扫描:

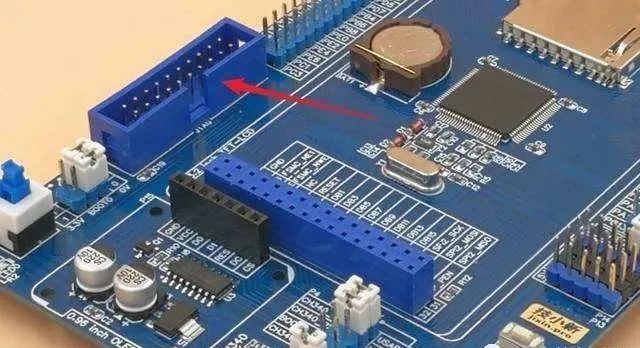

1.在FPGA开发板及相关设备断电的前提下,插上JTAG下载线接口; 2.插上USB Blaster或者ByteBlasterII的电缆; 3.接通FPGA开发板的电源。

1.断开FPGA开发板及相关设备的电源; 2.断开USB Blaster或者ByteBlasterII的电缆; 3.拔下JTAG下载线接口,并放置适宜地方存储。

—END—

ittbank

让电子库存因技术创造需求而改变的ITT模式电商平台。以共享经济理念的创客及工程师为核心、以开放用户生成的数据为基础,为其提供高性价比的应用解决方案和及时精准的供求信息,快速提高产品开发周期和生产直通率、提升电子器件的应用附加值。

公众号