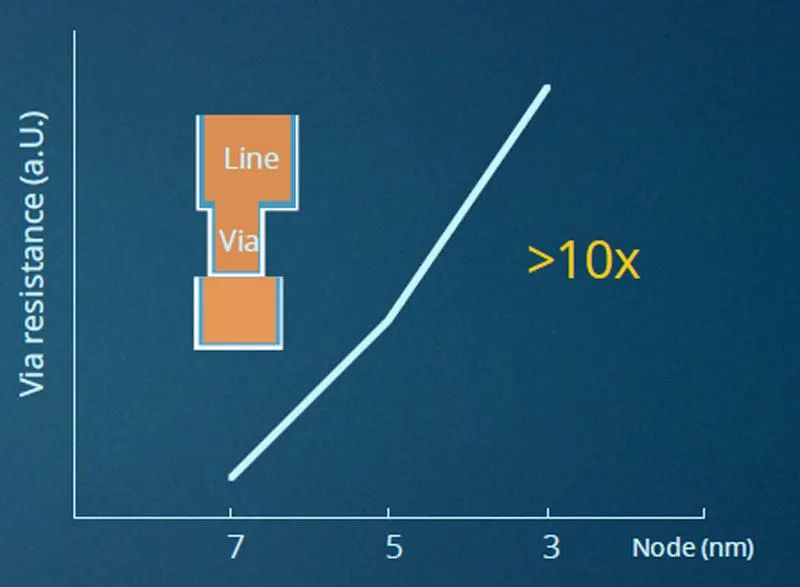

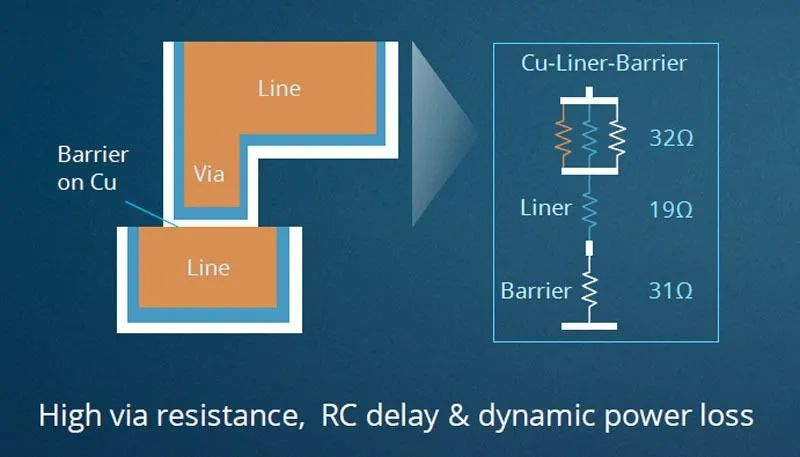

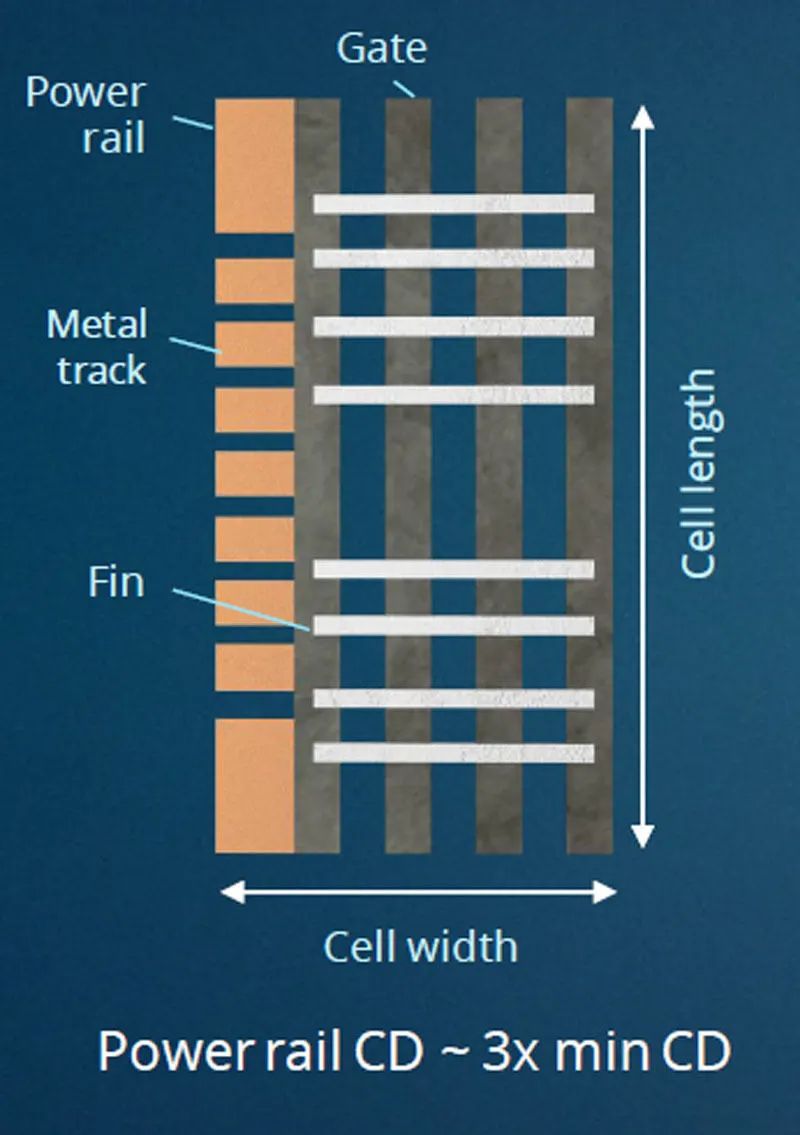

3nm制程的布线挑战和应对之策

来源:内容编译自「mynavi」,谢谢。

摩尔芯闻

您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

公众号

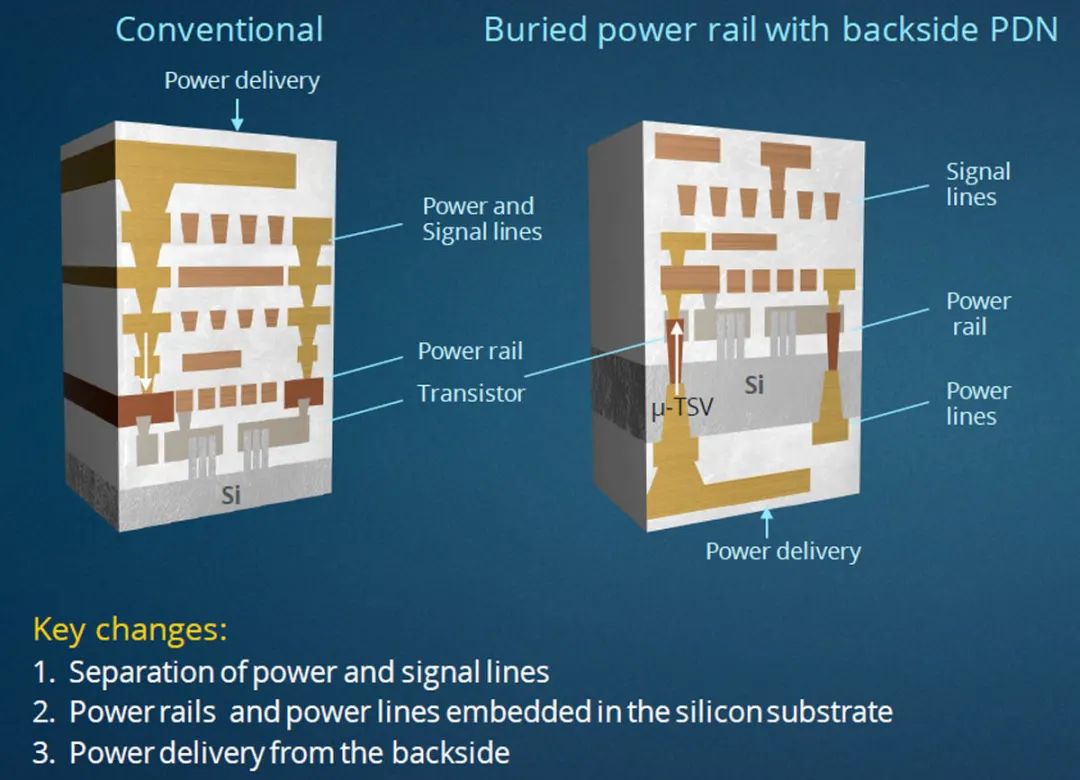

全新架构带来进一步突破

总结

摩尔芯闻

您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

公众号