半导体厂商如何做芯片的出厂测试?

▼

一

芯片测试概述

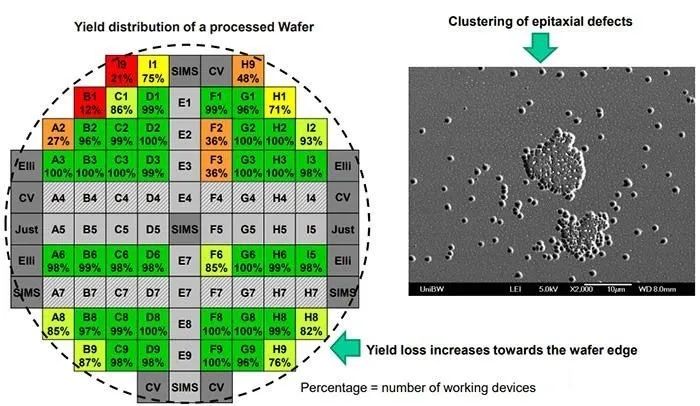

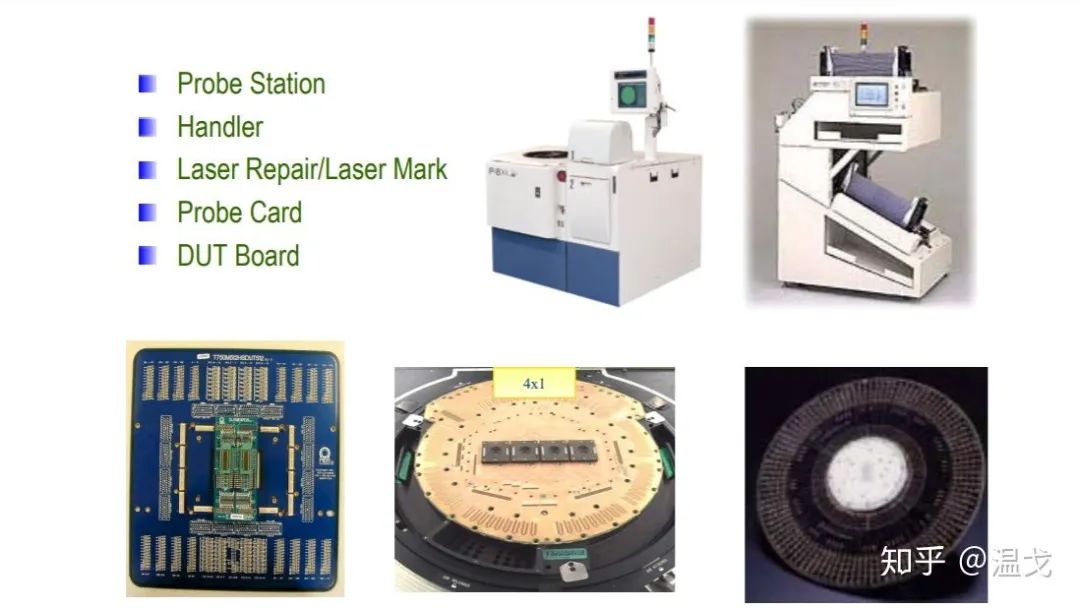

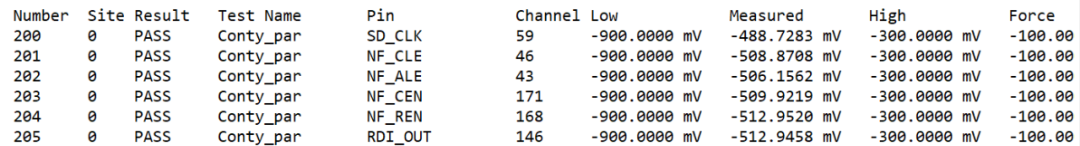

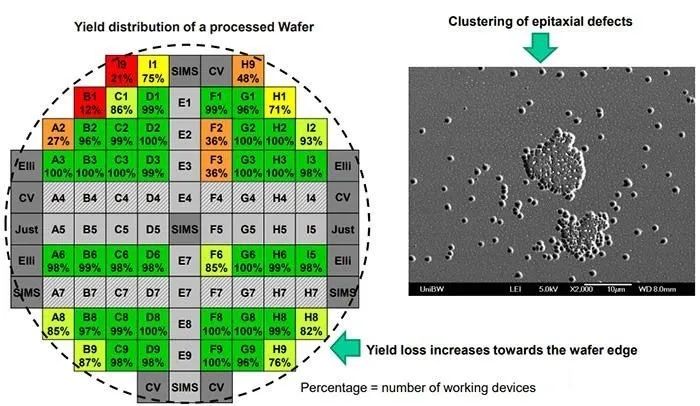

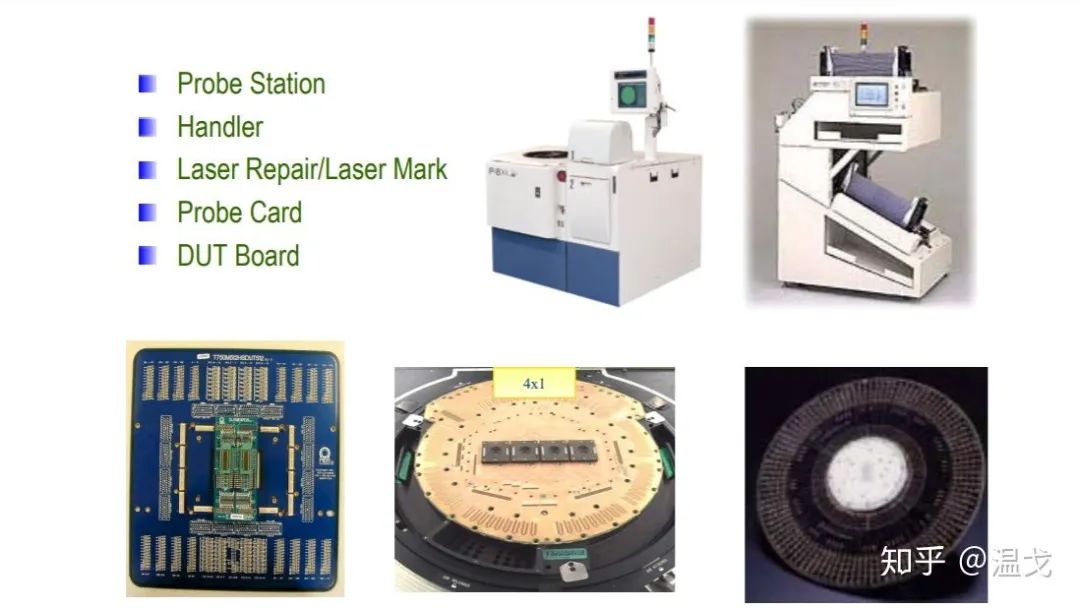

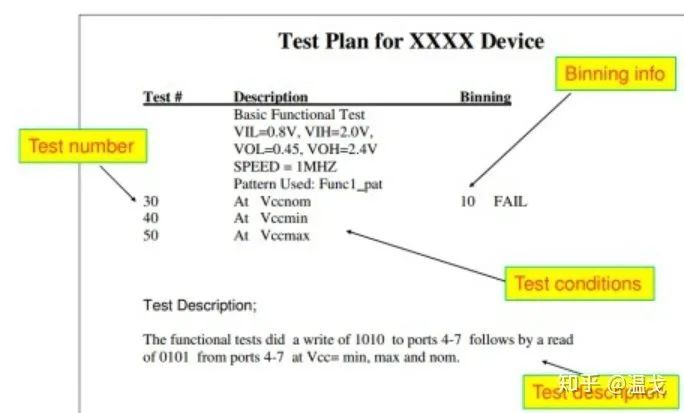

芯片测试分两个阶段,一个是CP(Chip Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。

二

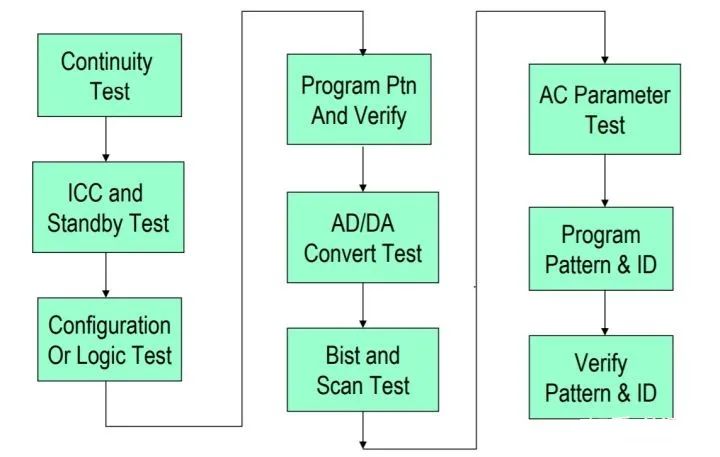

芯片测试流程

三

两个问题

四

写在最后

滤波器

欢迎滤波器+微波射频行业人士关注! 掘弃平庸,学习更专业的技术知识!

公众号

|推荐阅读|

© 滤波器 微信公众号

▼

一

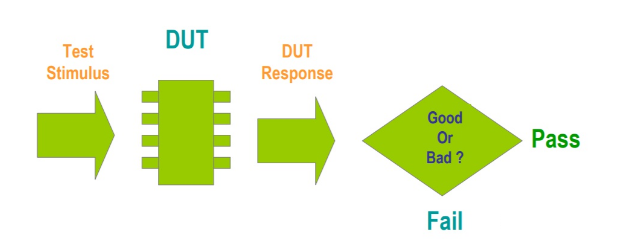

芯片测试概述

芯片测试分两个阶段,一个是CP(Chip Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。

二

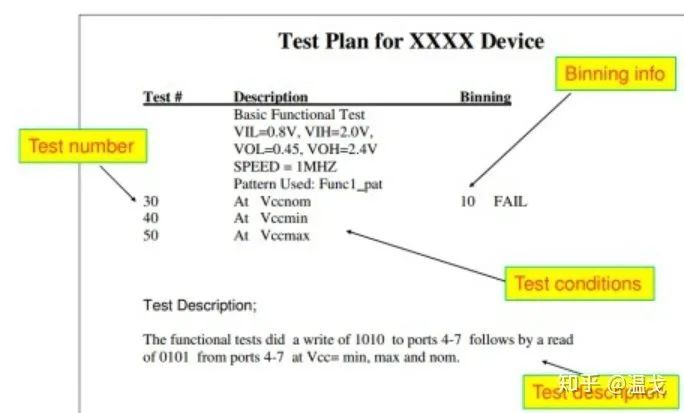

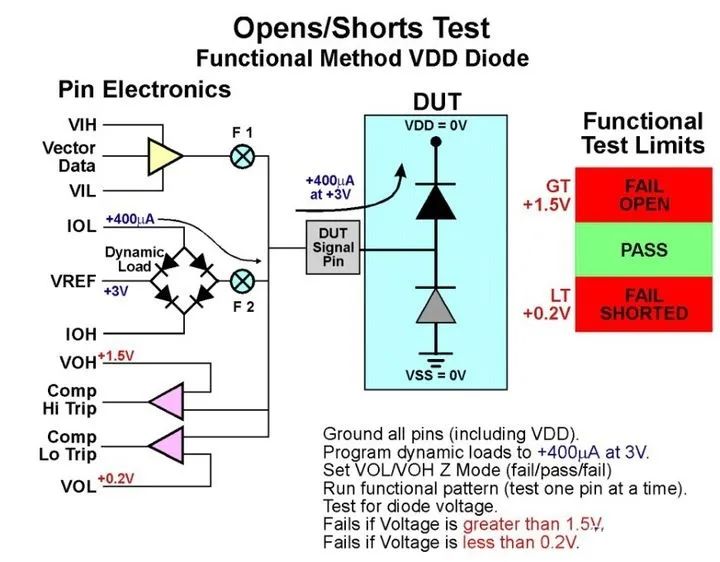

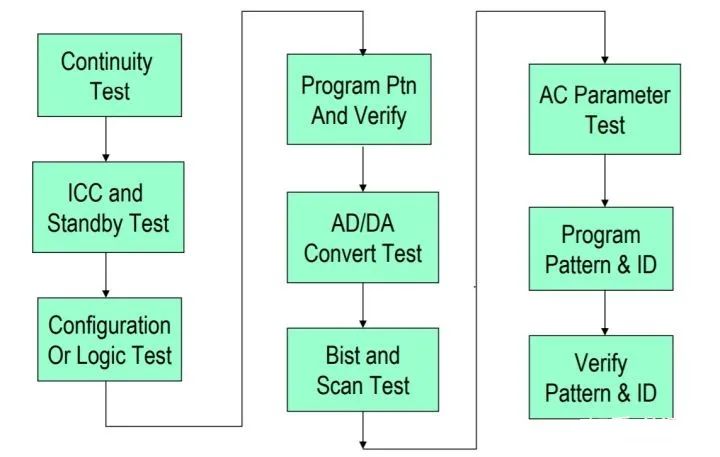

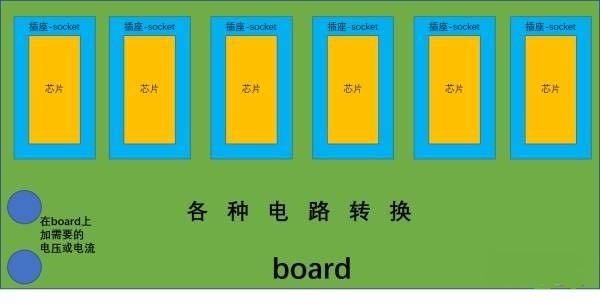

芯片测试流程

三

两个问题

四

写在最后

|推荐阅读|

© 滤波器 微信公众号