解读:先进封装的“四要素”

以下文章来源于SiP与先进封装技术 ,作者Suny Li

SiP与先进封装技术

SiP、先进封装、微系统,原创观点分享,设计仿真交流,发展前景预期~~

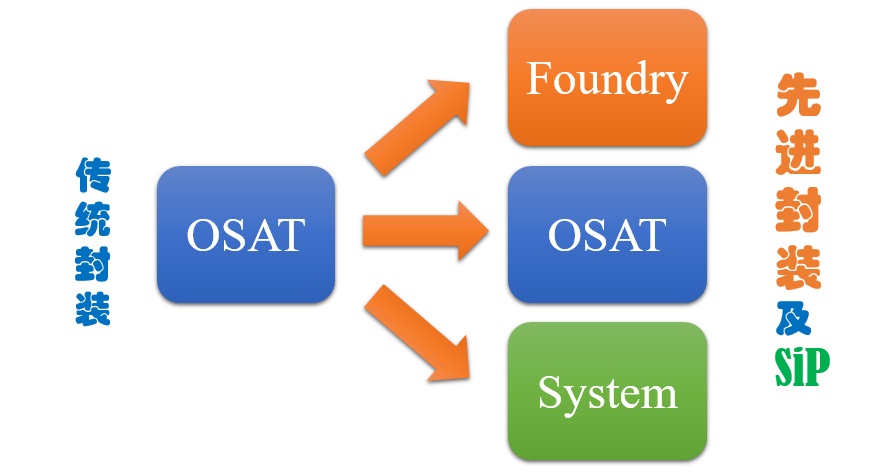

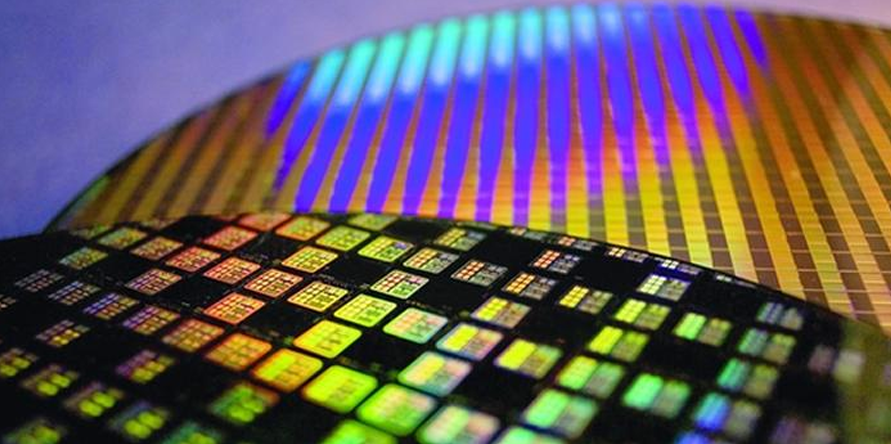

说起传统封装,大家都会想到日月光ASE,安靠Amkor,长电JCET,华天HT,通富微电TF等这些封装大厂OSAT;说起先进封装,当今业界风头最盛的却是台积电TSMC,英特尔Intel,三星SAMSUNG等这些顶尖的半导体晶圆厂IC Foundry,这是为何呢?

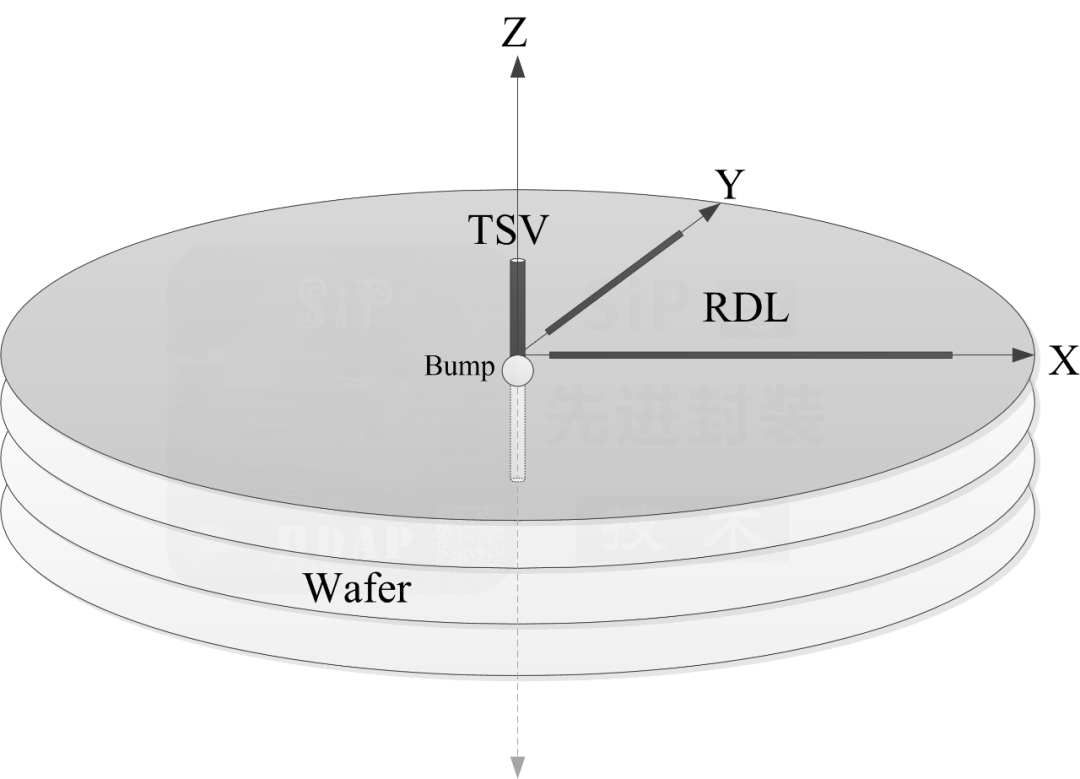

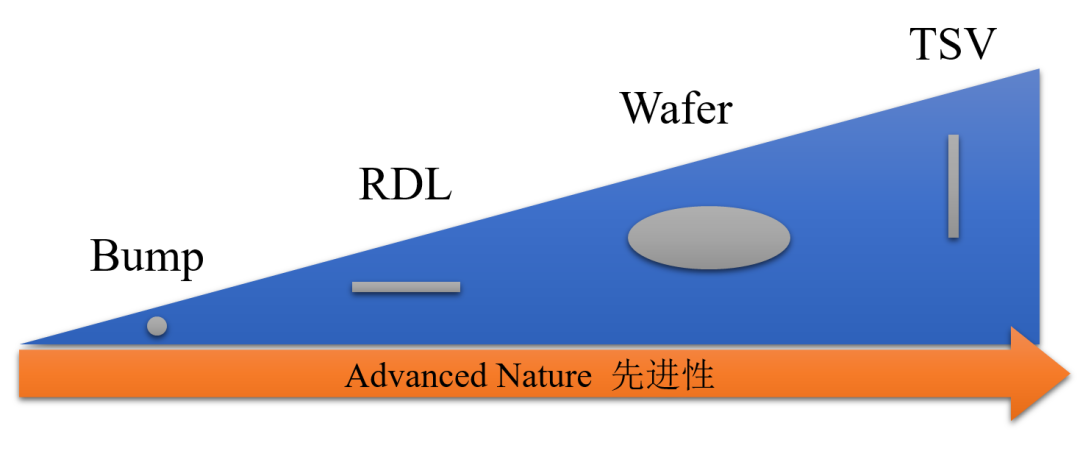

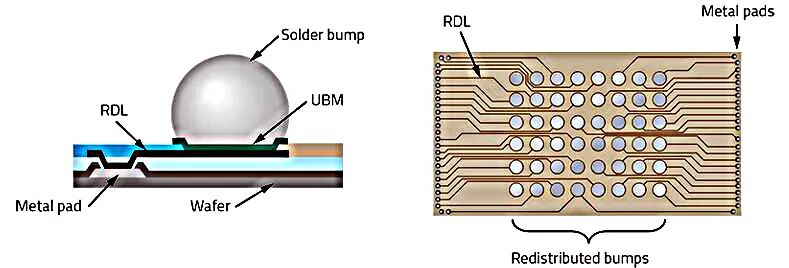

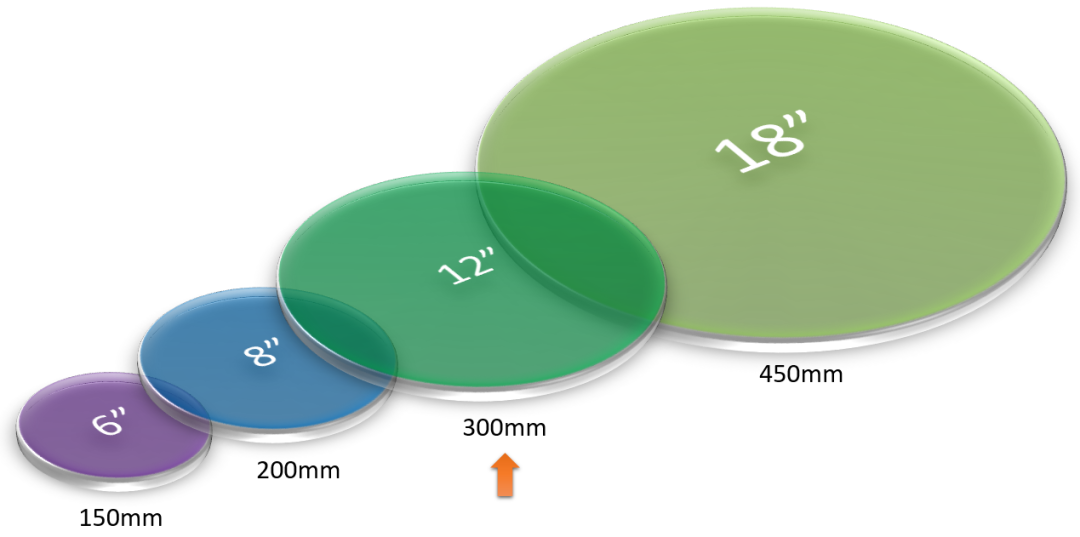

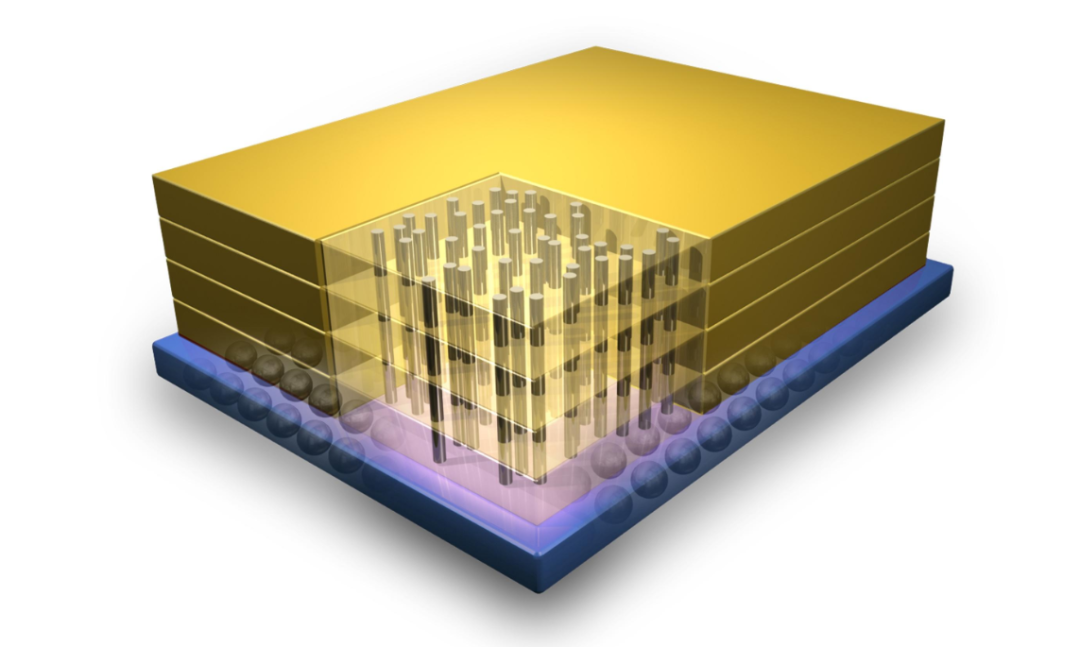

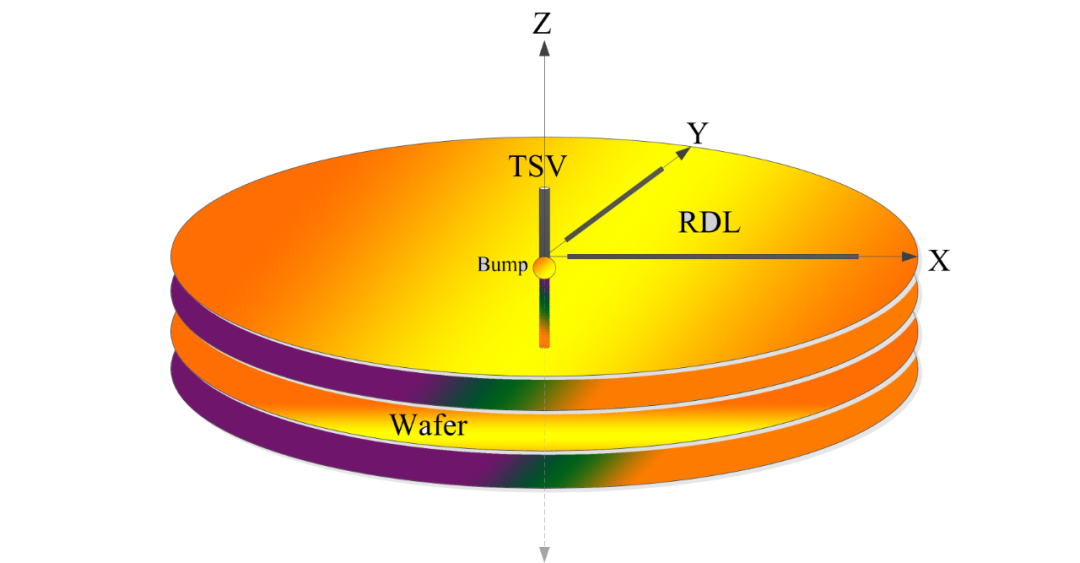

先进封装的四要素是指:RDL,TSV,Bump,Wafer,任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。

先进封装的四要素(原创)

先进封装的四要素(原创)

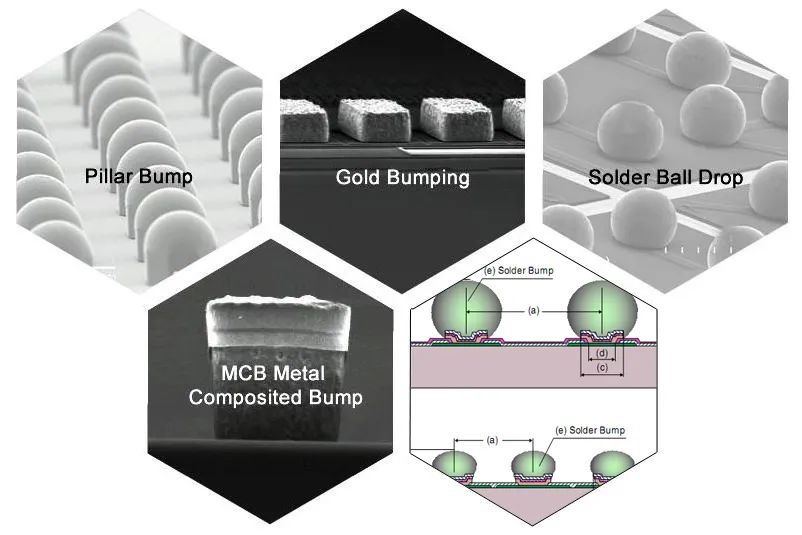

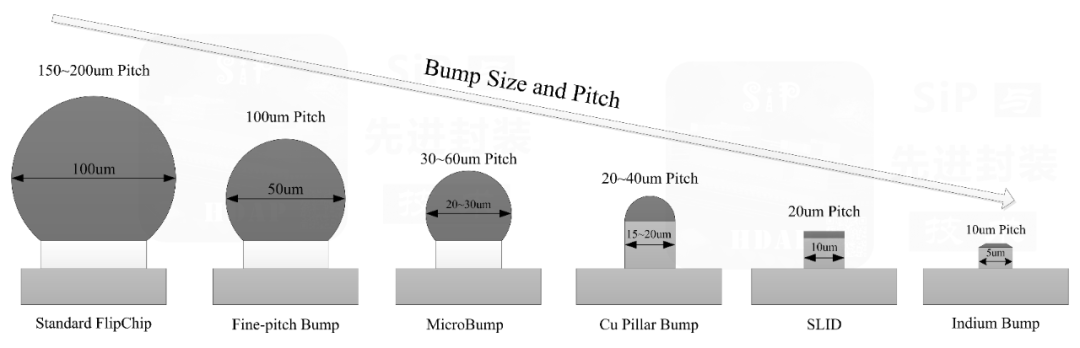

可以看出, Bump尺寸从最初 Standard FlipChip的100um发展到现在最小的5um。

那么,会不会有一天,Bump小到不再需要了呢?

确实有这种可能,TSMC发布的SoIC技术中,最鲜明的特点是没有凸点(no-Bump)的键合结构,因此,该技术具有有更高的集成密度和更佳的运行性能。

详细请参看:“先进封装”一文打尽

TSV的尺寸范围比较大,大的TSV直径可以超过100um,小的TSV直径小于1um。

随着工艺水平的提升,TSV可以做的越来越小,密度也越来越大,目前最先进的TSV工艺,可以在芝麻粒大小的1平方毫米硅片上制作高达10万~100万个TSV。

和 Bump以及RDL类似,TSV的尺寸也会随着工艺的提高变得越来越小,从而支撑更高密度的互联。

RDL,TSV,Bump,Wafer是先进封装的四要素,任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。

本文转载自 SiP与先进封装技术,仅供交流学习之用,如有任何疑问,敬请与我们联系info@gsi24.com。

今日芯闻

半导体行业的“资治通鉴”,汇聚半导体行业最新资讯,捕捉全球科技圈最新动态。专注于半导体晶圆制造、IC设计及封测、存储器、电子元器件等产业,华语圈百万半导体人睡前必读的“今日芯闻”。

公众号

全球物联网观察

为您网罗全球最新物联网行业资讯,聚焦行业前沿科技,展现优秀厂商产品方案,为您深入解读行业趋势,带您一起感知未来物联网世界!

公众号