来源:内容由半导体行业观察(ID:icbank)编译自「semiwiki」,谢谢。

半导体行业观察最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

2164篇原创内容

公众号

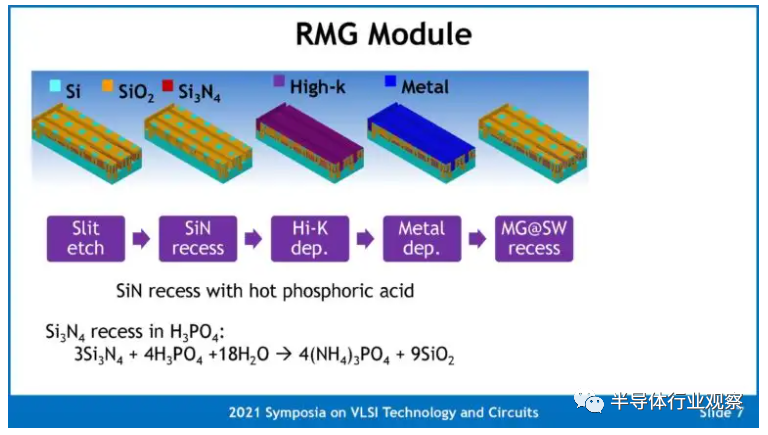

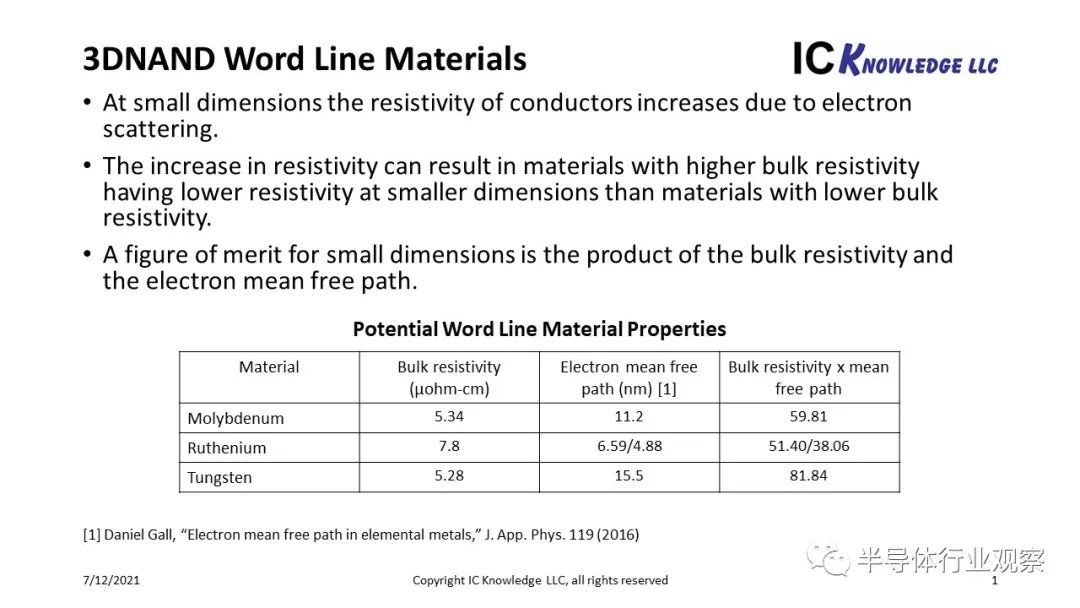

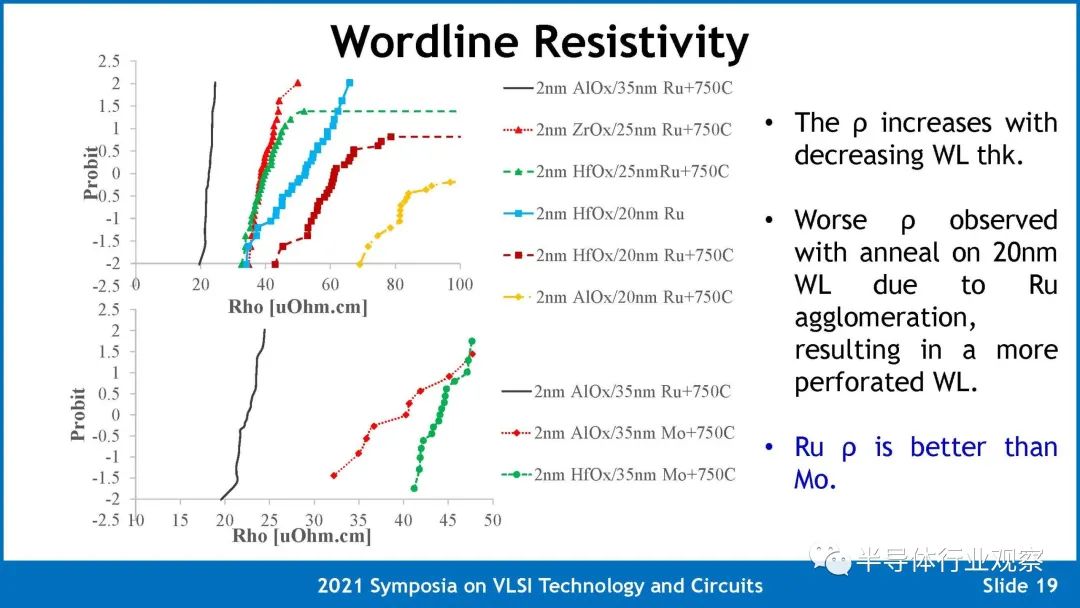

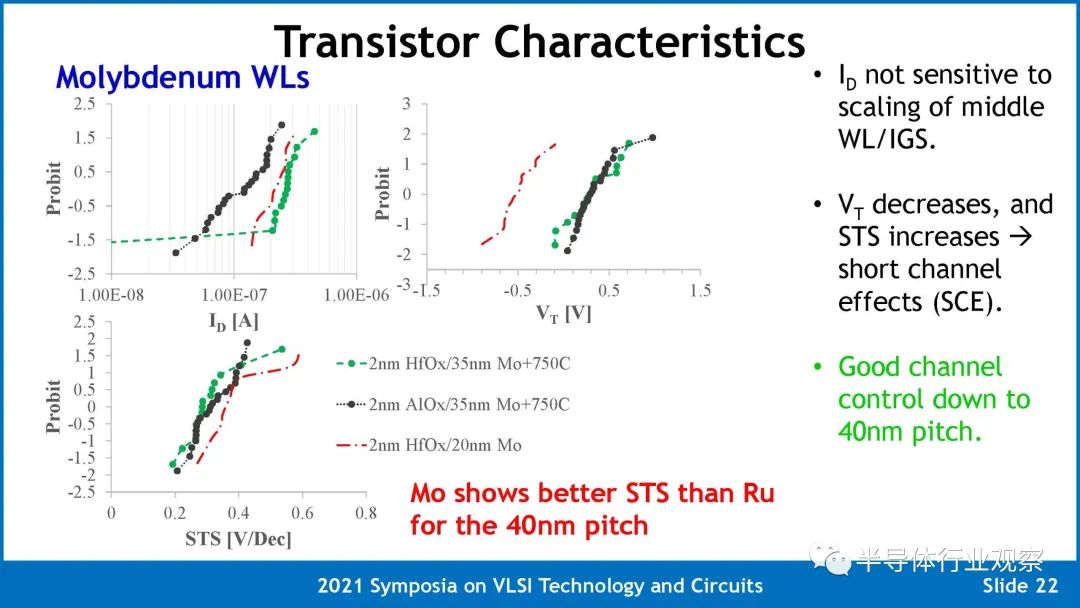

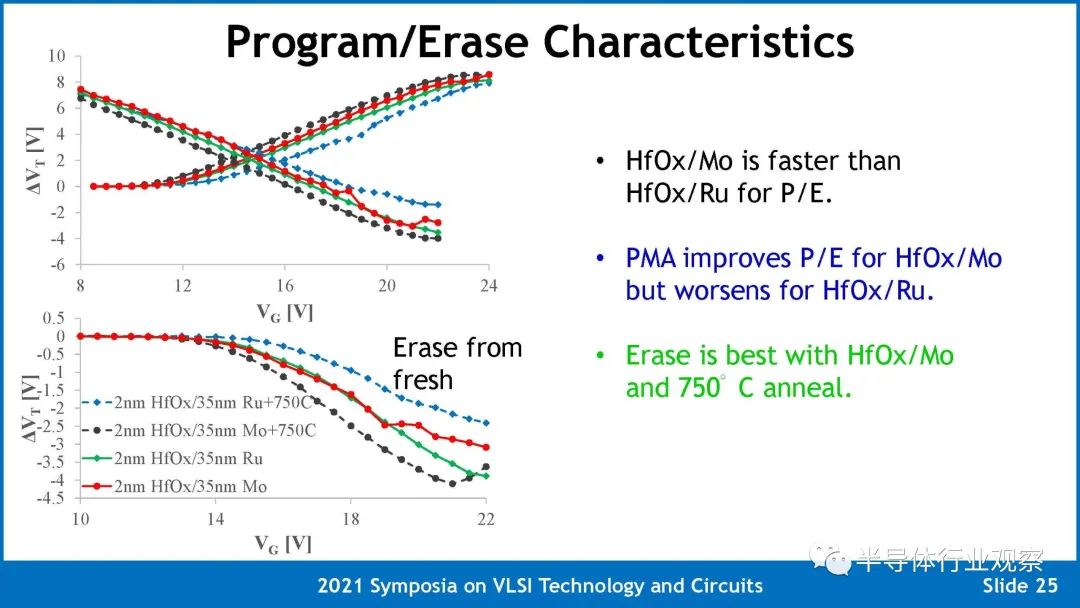

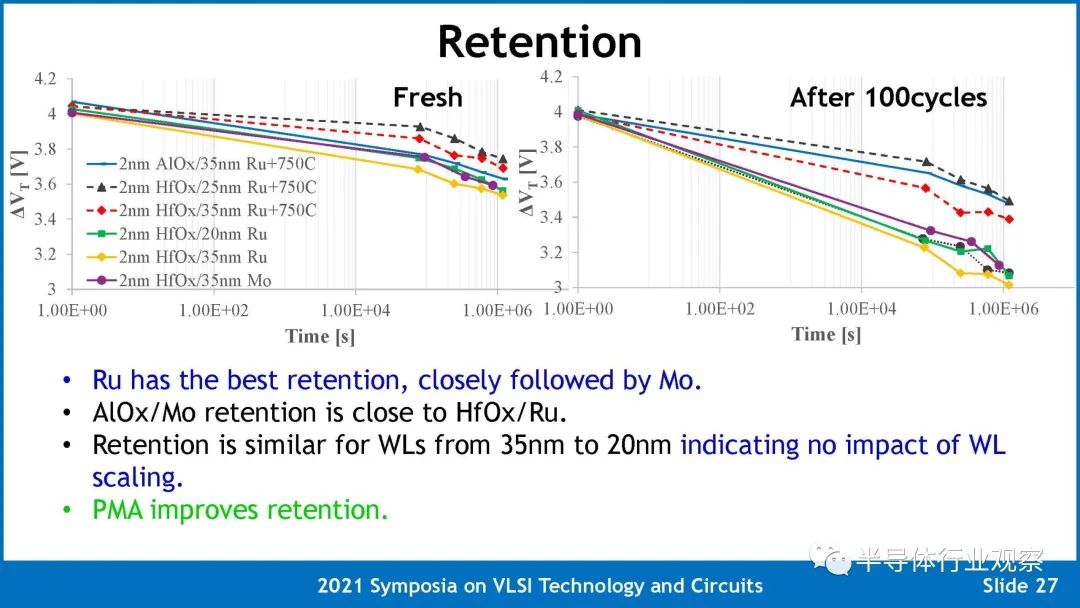

在2021年VLSI技术研讨会上,Imec介绍了钌(Ru)和钼(Mo)作为3D NAND闪存的替代Word Line (WL)材料,并“首次演示钌和钼WL集成到40nm间距的3D NAND器件”。我有机会采访其中一位作者:Maarten Rosmeulen。NAND闪存的当前技术水平是层数不断增加的3D NAND,例如,在同一次会议上,三星展示了他们即将推出的176层3D NAND工艺,这是其128层工艺的后续。一个值得注意的方面是,他们降低了176层工艺的内存单元的高度,以控制整个内存堆栈的高度。美光和SK海力士也宣布了176层工艺,而铠侠则在其128、128和112层工艺之后,宣布了162层工艺。随着层数的增加,由于图形和应力原因,需要缩小层厚以控制堆叠的高度,就像三星在其176层工艺中所做的那样。业界最流行的3D NAND类型是使用替代金属栅极(RMG)工艺的电荷陷阱闪存。在RMG工艺中,氧化层和氮化物的交替层被沉积,氮化物是一种牺牲膜,后来被去除并替换为金属栅极和用作WL的金属片,见图1。R=ρL/A,其中ρ是电阻率,L是长度,A是横截面积。随着氮化物层厚度的减小,所得到的替代金属片变得越来越薄,从而减小了横截面积,并且在小尺寸下,由于电子散射进一步加剧了电阻的增加,ρ增加。WL电阻率的增加导致产品的编程/擦除时间变慢。电阻率在小尺寸下增加的程度部分取决于材料中的电子平均自由程(free path)。小尺寸处电阻率的增加可导致块体电阻率相对较高的材料在小尺寸处具有较低电阻率。小尺寸材料的品质因数是体电阻率乘以电子平均自由程。图2显示了一些关于材料电阻率的数据。从图2可以看出,钼和钌在小尺寸下的电阻率可能低于钨。当然,图2中的值只是体积值,不一定转化为实际的器件结构,这项工作的目的是通过实验测量表现。在这项工作中,创建了一个五层NAND来评估这些替代材料的电阻率和晶体管性能。因为Imec是一个研究机构,所以他们创建176层设备是不可行的,但5层器件也保留了基本的物理特性。图3显示了厚度为35nm、25nm和20nm的WL的Mo和钌电阻率。在所有研究的情况下,钌显示出比钼低的电阻率。图5比较了钼和钌的编程擦除,钼显示出比钌更快的编程/擦除。最后,图6比较了钼和钌的数据保留率,钌比钼好,但钼性能非常接近。在性能上,钌的电阻率更好,钼的晶体管性能则更好一些。这项工作试图回答的关键问题是这些材料中的一种是否可以更好地替代钨用于细WL。在这项工作中,尚未在相同条件下测量钨的电阻率和晶体管性能,但公司表示未来将进行有关方面的工作。我问他们是否知道何时必须在商业产品中更换钨,他说他们没有,最终个别产品的具体情况不仅取决于层厚度,而且最终取决于整个器件实现的延迟,这也可能取决于应用程序。我们还简要讨论了成本,IC Knowledge LLC是半导体和MEMS成本建模的世界领导者,我提到我认为钌对于3D NAND的使用过于昂贵,他说他有大学正在研究这个。我使用该公司的战略成本和价格模型进行了一些快速计算,我看到钨和钼每片晶圆的前期成本约为10到20美元,而在我看来,钌的价格高出一个数量级,这使得钌的使用成本太高.总之,这项工作是确定钌和钼作为钨的长期替代品的适用性的重要一步,以实现3D NAND层数的增加和性能的提高。

摩尔芯闻您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

237篇原创内容

公众号

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2741内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!