刘明院士:1nm工艺展望

以下文章来源于科学出版社 ,作者刘 明

传播科学,创造未来。

来源:内容来自「科学出版社」,作者:刘明(中国科学院院士),谢谢。

图片来源:Pixabay

国内外研究现状

自1958年集成电路问世以来,以硅 CMOS 技术为基础的集成电路一直遵循摩尔定律不断向前发展,即集成电路上可容纳的晶体管数量每隔 18~24 个月增加一倍,性能提升一倍,而价格保持不变。在 CMOS 工艺中,通常用特征尺寸来表征栅长,即沟道长度,通过缩小特征尺寸来提高芯片工作速度,增加集成度及降低成本。当前特征尺寸已经从 1971 年的 10µm 缩减到10nm 左右,先进集成电路容纳的晶体管数量已经超过 10 亿个。

近年来,得益于制造技术的进步,相对于前一个技术节点,新技术节点的电路性能提升30%,功耗下降50%,面积缩减50%,可靠性基本保持不变。但是随着集成电路工艺进入 7nm 技术节点(对应沟道长度约 20nm),传统逻辑和存储器性能的继续提升遇到技术瓶颈,集成电路发展正处于重大技术革新时期。未来 5~10 年,集成电路产业将沿着扩展摩尔(more Moore)、超越摩尔(more than Moore)和超越 CMOS(beyond CMOS)三个技术路线向前发展。

(1)扩展摩尔。通过器件结构、沟道材料、集成工艺等方面的创新,微缩特征尺寸,继续提升集成电路密度,相关技术路线已经规划到近 1nm 技术节点,这正是本文讨论的重点。

(2)超越摩尔。以价值优先和功能多样化为目标,不强调特征尺寸的缩小,而是通过功能扩展及多功能集成,发展新功能器件与系统集成,实现应用层面的系统性能提高。

(3)超越 CMOS。通过新材料、新结构、新原理器件的研发推动集成电路的发展,从物理工作机理与技术实现方式上突破传统硅基 CMOS 场效应晶体管技术限制。

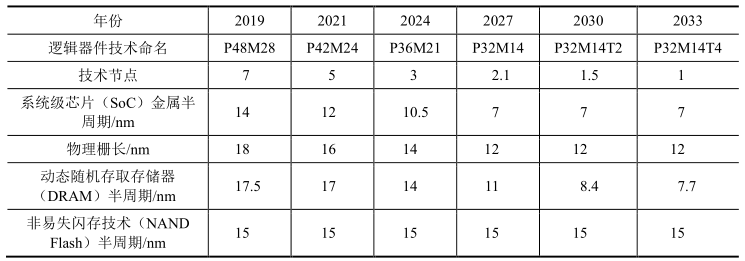

扩展摩尔技术路线是实现更小、更快、更廉价的逻辑与存储器件的重要技术路径。表1 是电气和电子工程师协会(IEEE)给出的国际器件与系统路线图(international roadmapfor devices and systems,IRDS)。

短沟道效应是 CMOS 工艺技术向更小尺寸和更高集成度方向发展面临的主要问题,当沟道长度缩小到纳米量级时,即使不施加栅极电压,也无法完全关断 MOS 晶体管,源与漏之间会存在漏电流,使电路静态功耗增大。为此,需要通过新工艺、新结构与新器件的不断创新实现更先进的技术节点。总体上来说,逻辑器件的发展呈三个重要趋势:从结构上看,将由平面转变为立体,三维晶体管技术(如 FinFET 等)成为主流器件技术;从材料上看,沟道构建材料将由硅转变为非硅,非硅成为主流;从集成上看,类似平面 NAND 闪存向三维NAND 闪存演进,未来的逻辑器件也会从二维集成技术走向三维堆栈工艺。从功耗和性能两个维度来看,有两条比较清晰的技术发展主线:采用新结构增加栅控能力,以实现更低的漏电流,降低器件功耗;采用新材料增加沟道的迁移率,以实现更高的导通电流和性能。10nm 及以下逻辑工艺将引入 Ge/Ⅲ-Ⅴ族高迁移率沟道材料、GeSi 源/漏应变材料等,结构上将采用纳米场效应晶体管和隧穿场效应晶体管(TFET)等。而存储器件,DRAM 尺寸缩小到 1x 技术节点遇到工艺复杂、良率下降、成本上升、功耗增加等挑战,DRAM 在容量增加的同时刷新功耗增加,其容量扩展性遭遇巨大挑战。新兴非易失存储技术,特别是基于非电荷存储机制的两端器件,避免了电荷型 MOS 结构尺寸缩小过程中器件可靠性的严重退化问题,有望成为未来非易失存储的主流技术。同时,三维集成是高密度存储器发展的方向和核心技术。

近 20 年来,美国英特尔公司一直是逻辑集成电路技术发展的领头羊,分别于 90nm(2003 年)、45nm(2007 年)和 22nm(2011 年)技术节点上率先研发出晶体管沟道应变、高 K 金属栅和三维 FinFET 技术,不断推动着扩展摩尔技术的进步。但是,随着制造工艺复杂度和制造成本的不断攀升,只有极少数集成电路厂商能够承受 7nm 节点以下集成电路的研发费用。目前,格罗方德半导体股份有限公司和联华电子股份有限公司均已退出先进节点集成电路的研发。目前,全球只有英特尔公司、三星公司、台积电公司有能力研发 7nm 及以下集成电路技术。三星公司、台积电公司于 2016 年年底领先研发成功 10nm集成电路技术,2018 年台积电公司的 7nm 集成电路开始量产。中国中芯国际公司 14nm工艺制程芯片 2019 年实现量产,并将于 2021 年正式出货。目前来看,考虑到技术复杂度的不断增加和应用需求有所放缓,技术节点升级的周期将可能放缓至30 个月以上。

待解决的关键技术问题

1nm集成电路对应的特征尺寸将达到7nm,硅集成电路技术在速度、功耗、集成度、可靠性等方面将受到一系列基本物理问题和工艺技术问题的限制,面临的关键技术挑战包括:①晶体管结构:如何重新定义底层设计;②沟道材料:如何获取兼容 CMOS 工艺的高载流子迁移率材料;③极紫外投影光刻技术:如何提高分辨率和产率;④互连:如何开发新材料和新集成方法,以降低RC 延迟时间;⑤设计与工艺联合优化技术:如何寻找制造技术和设计电路图形的关联性。

1

晶体管结构

当集成电路进入 22nm 节点,传统的平面场效应晶体管由于栅极不能完全控制沟道,从漏极到源极的亚阈值泄漏增大,无法进行进一步的缩微,被三维结构的 FinFET 取代。FinFET 结构类似鱼后鳍的叉状 3D 架构,由衬底上的硅体薄(垂直)翅片组成,通过在鳍片的三个面上施加栅极,可以有效控制沟道漏电流,降低沟道掺杂,提高载流子迁移率 [5] 。高 K 金属栅新材料、FinFET新器件结构和沟道倒掺杂新工艺的引入,可以降低工作电压,减少器件与电路的功耗,这对于低功耗要求较为严格的消费类芯片尤为重要。但是当集成电路进入3nm 节点后,栅控与漏电问题将再次凸显,再加上阈值平坦化和翅片上的热耗散等难题,三栅 FinFET 不再适用,有可能被围栅(gate-all-around,GAA)纳米线器件取代。GAA 在结构的四个面都施加一个栅极,从而保持沟道静电完整性,实现更好的漏电流控制和载流子一维弹道输运。为了进一步克服物理缩放比例和性能限制,需要发展三维集成技术,形成类似 3D-NAND 闪存的垂直GAA 结构,或者通过逐层堆叠的方法形成堆叠纳米线晶体管,从而提高单位面积的电路集成度。尽管如此,对于未来的 1nm 集成电路制造技术,如何重新从底层设计具有超陡亚阈值斜率、超小亚阈值摆幅的低功耗器件结构,增强栅极控制能力,仍然是有待解决的难题。

2

沟道材料

当集成电路进入 90nm 节点后,集成电路产业界开始引入应变硅材料,并寻求更高载流子迁移率的新型沟道材料。在硅衬底上外延应变 SiGe 或 Ge 沟道可以提高空穴迁移率来增大驱动电流。主要问题是需要严格控制外延层厚度和外延层与基底层之间的界面粗糙度。当应变层厚度超过临界值时,应力弛豫会导致载流子能带分布与波谷散射增加,从而造成迁移率退化。由于需要在前道工序中引入 Ge,后续工艺需要防止 Ge 沾污和采用低工艺温度。Ⅲ-Ⅴ族化合物半导体,如铟镓砷、砷化镓和砷化铟等具有很高的载流子迁移率,与 FinFET 和GAA 器件的集成在7nm 节点集成电路表现出优异的性能,其挑战在于和硅材料之间存在大的晶格失配,导致晶体管沟道的缺陷,尤其是在硅材料上生长铟镓砷材料更为严重。当前利用选择性外延技术集成Ⅲ-Ⅴ族化合物的研究正在进行中,其他技术如硅上键合技术也在探索之中。为了有效避免短沟道效应,通常要求场效应晶体管沟道厚度小于沟道长度的 1/3,1nm 节点集成电路的沟道长度小于 10nm,受量子效应限制,传统三维半导体材料很难将沟道厚度减小至 3nm以下。具有原子层厚度的二维半导体材料具有比硅更小的介电常数、更大的带隙和载流子有效质量。将这种新型材料应用于短沟道晶体管正在成为一个前沿探索方向。1nm 物理栅长的 MoS 2 场效应晶体管已经被报道,其结构是以直径1nm 的单臂碳纳米管作为栅电极,并以 ZrO 2 包裹碳纳米管形成背栅电容,以 Ni作为源漏电极,晶体管亚阈值摆幅 65Mv/dec,开关比 10 6 ,漏致势垒降低至290mV/V。但是载流子迁移率仍低于理论预期值,目前使用的微机械剥离等方法无法应用于集成电路生产。

3

极紫外投影光刻技术

光刻是集成电路制造中技术难度最大、成本最高的技术环节,成本占集成电路制造成本的 35%以上,在每一代集成电路技术更新中都扮演着技术先导的角色。透射式浸没式 193nm 步进扫描投影光刻机的单次曝光分辨力理论极限为38nm,无法通过单次曝光形成22nm节点及以下集成电路关键图层的目标图形,需要采用多重光刻技术,即把原来一层光刻的图形经过拆分之后放到两个或多个掩模上,采用多次光刻共同形成一层关键图层。通过四重图形曝光手段,集成电路特征尺寸可以达到 10nm。通过八重图形曝光手段,集成电路特征尺寸可以达到5nm。但是多重图形曝光工艺复杂,如多块掩模版、多次曝光、多次刻蚀、更为复杂的图形布局拆分算法等,导致制造成本急剧上升。为此,需要采用波长为 13.5nm 的反射式极紫外投影光刻技术,当前阿斯麦(ASML)公司商用的TWINSCAN NXE:3400B 极紫外投影光刻机数值孔径已经达到 0.33,5nm技术节点逻辑集成电路制造中金属互联层和高密度孔阵列均可以通过单次极紫外投影曝光完成。未来 5~10 年,预计数值孔径将提高到 0.6 以上,光源功率、掩模缺陷和光刻胶灵敏度三大关键技术将取得突破,结合离轴照明等分辨力增强技术,极紫外投影光刻单次曝光分辨力极限将逼近 7nm,进一步采用多重图形极紫外投影曝光技术,分辨力极限将达到 2nm 及以下,满足 1nm 技术节点集成电路光刻需求。

4

互连技术

随着互连线特征尺寸的不断缩小、布线层数和长度的不断增大,集成电路进入 130nm 节点以后,RC 时间延迟逐渐成为阻碍时钟频率提高的主要因素。通常采用铜互连和低介电常数材料两种方法来降低 RC 延迟时间。相比于铝及其合金互连,新一代的铜互连具有更低的电阻率、更高的熔点和更好的抗电迁移能力,可以降低 RC 时间延迟约 40%,从而提高器件密度和时钟频率,并降低能耗。铜互连通常采用“大马士革”结构的镶嵌工艺,且被铜种子层、衬垫和薄扩散阻挡层所包围。传统的物理气相沉积和扩散阻挡层的方法被原子层沉积方法所取代。但是,当集成电路进入 5nm 以后,铜互连方案变得越发紧凑,将面临铜线电阻过大、铜易扩散、低介电常数材料易击穿等技术挑战,光刻工艺造成的线边缘粗糙度、趋肤效应、过孔错位等因素也会使铜互连可靠性变差。延续传统镶嵌工艺的解决方案可能用钴或钌取代铜进一步降低互连电阻 [9] 。其他集成制造工艺挑战还包括均方根小于 2nm 的超低线边缘粗糙度光刻工艺、小于2nm 的扩散阻挡层沉积、无损伤化学机械抛光、无损伤化学清洗等。

5

设计与工艺联合优化技术

当集成电路进入 22nm 节点及以下,工艺偏差和波动性相比特征尺寸所占比例日益增大,导致缺陷密度急剧上升,传统的工艺和设计规则无法满足产品性能需求,设计和工艺联合优化技术 [10] (design technologyco-optimization,DTCO)成为必然的发展趋势。其基本思想是集成电路设计工程师与光刻工程师共同深入寻找制造技术和设计电路图形的关联性,既要满足器件性能的要求,又能在芯片工厂内实现制造且具有足够工艺窗口的技术方案,在集成电路生产之前就能有效评估可制造性,对晶体管架构设计、模块级物理实现、材料和关键工艺技术,以及可靠性整个流程进行协同优化。在设计层面,需要在明确的物理设计思路基础上,对电路仿真进行进一步精确化设计,确定晶体管架构,如绕栅极纳米线和纳米板器件结构,仿真范围从测试图形扩展到整个标准单元。综合考虑布线能力、功耗、时序和面积等因素,获取精确的晶体管模型和库架构,建立版图分析和模型验证方法,优化器件图形设计规则,产生适于1nm 技术节点的友好版图,用于 1nm 技术节点光刻工艺和模型的输入。在制造层面,将晶体管架构、薄膜材料沉积、极紫外光刻和等离子体刻蚀等技术协同优化整合,实现复杂纳米结构的高分辨率和高保真度。其中难度最大的是极紫外光刻协同优化,其流程涉及光源-掩模协同优化、光学邻近效应修正、亚分辨率辅助图形、高精度计量、光刻胶类型、光刻胶反应机理和随机性效应、光刻后处理等,需要设计、工艺、材料和设备等各个领域的工程师紧密合作,以获取合理的分辨率、工艺宽容度、焦深、掩模误差因子和线条边缘粗糙度等参数,并缩小标准库单元区域的面积,降低器件结构和电学性能的偏差,满足功耗、性能、面积、成本(power,performance,area,cost,PPAC)的目标需求。

优先发展技术领域

当前集成电路发展正处于重大技术革新时期,1nm 技术节点的推进面临两大基本挑战:一是由于晶体管物理性质限制,缩小特征尺寸越来越困难;二是制造工艺创新步伐放缓。这给我国的集成电路发展带来了新的机遇和挑战。建议优先考虑以下技术领域的发展。

(1)扩展摩尔技术。垂直 GAA 结构、堆叠纳米线等晶体管架构,实现晶体管栅极长度的进一步微缩。异质材料体系的器件集成,突破多种物理失配限制,提高载流子迁移率。极紫外投影光刻设备及工艺,突破光源、掩模及检测方法、光刻胶、多重曝光等技术,提高分辨率。高密度互连,形成新的互联材料和图案成形技术方案。设计与工艺联合优化,实现精确的工艺波动性控制。

(2)超越摩尔技术。发展新功能器件与系统集成方法,通过硅通孔(TSV)三维集成技术将处理器、存储器、传感器、微机电系统、能源、生物芯片等整合成一个整体,实现新功能的应用。

(3)超越 CMOS 技术。新原理逻辑器件,包括隧穿场效应晶体管、负电容场效应晶体管、纳机电逻辑器件和自旋电子器件等。新型存储器件,包括自旋转移力矩磁存储、相变存储器、阻变式存储器及其大规模集成技术。忆阻器的神经仿生功能的研发,发展适用于忆阻器的类脑神经网络计算处理机制和体系架构,开发类脑计算系统的计算模型及相关算法,以此实现大规模类脑神经网络计算系统。

我国的发展战略与对策建议

制定技术发展战略时建议考虑如下问题。

(1)加强应用基础研究,鼓励原始创新,突出颠覆性技术创新。增加在新材料、新结构、新原理器件关键技术和基础问题上的研发投入,为我国发展具有自主可控的集成电路产业提供新途径。

(2)加强集成电路关键共性技术研发工作,聚焦围栅纳米线等新器件、极紫外光刻等新工艺研发,打通 1nm 集成电路关键工艺,为高端芯片在国内制造企业的生产提供重要支撑。

(3)从国家层面对集成电路制造技术体系和产业生态建设进行系统、科学地规划和布局,遵循“一代设备,一代工艺,一代产品”的发展规律,加大集成电路关键材料、核心装备、关键工艺和器件工程化的支持力度。

(4)积极推进微电子学科教育建设。针对集成电路制造技术多学科高度融合这一特点,加强具备综合知识背景的集成电路人才培养,支撑我国新一代集成电路产业的重大跨越。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2747内容,欢迎关注。

推荐阅读

半导体行业观察

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!