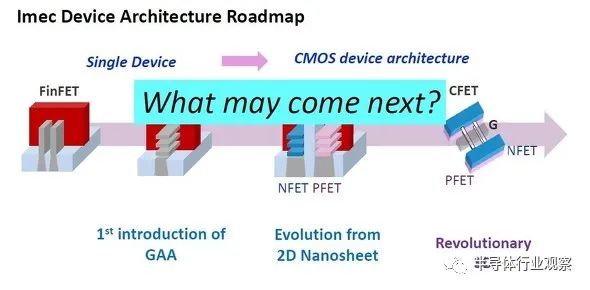

3nm后的晶体管猜想

以下文章来源于半导体行业观察 ,作者福田昭

半导体行业观察 .

最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

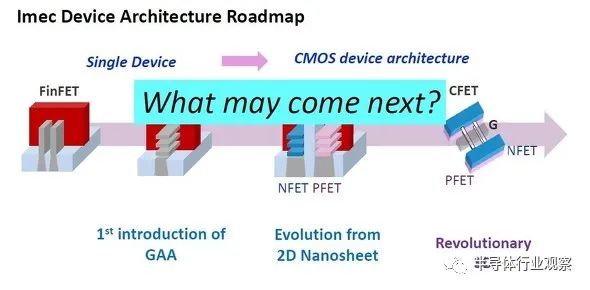

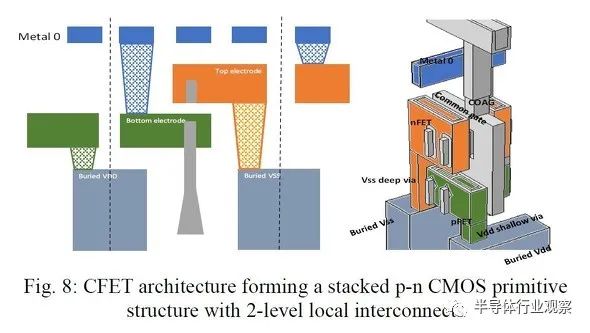

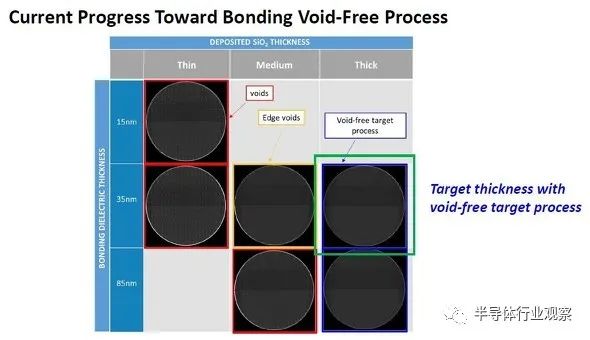

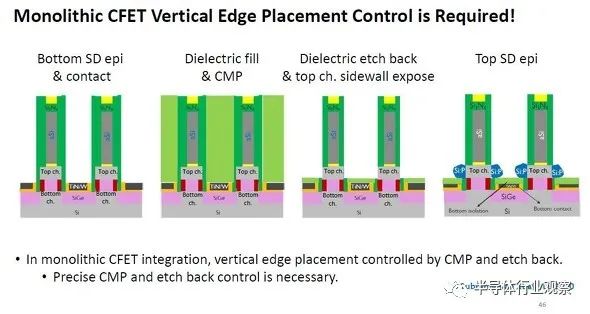

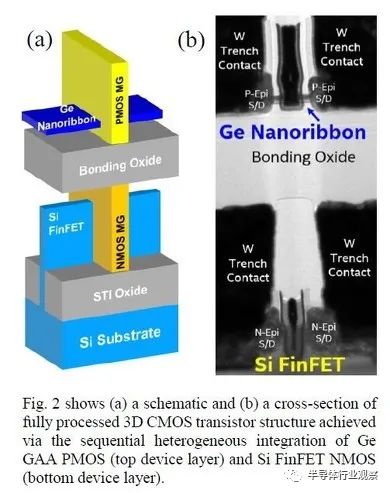

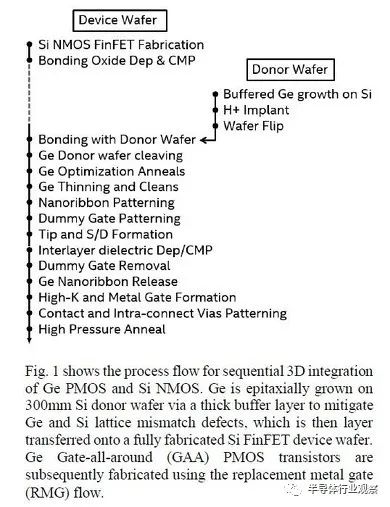

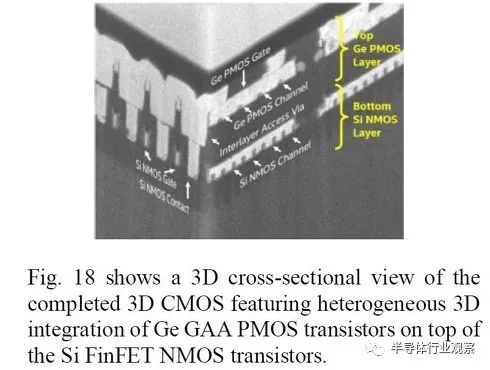

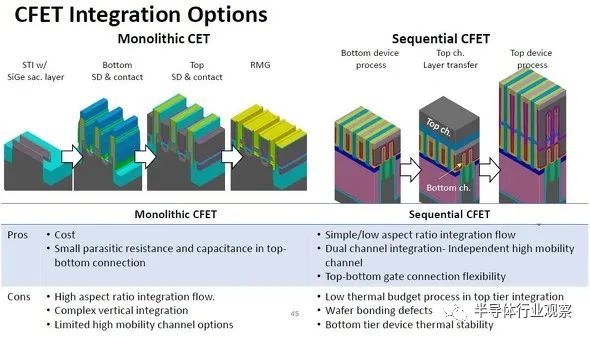

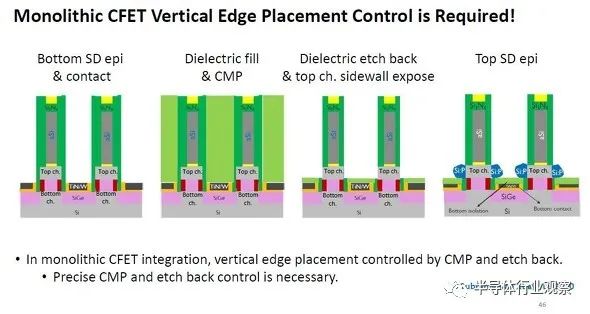

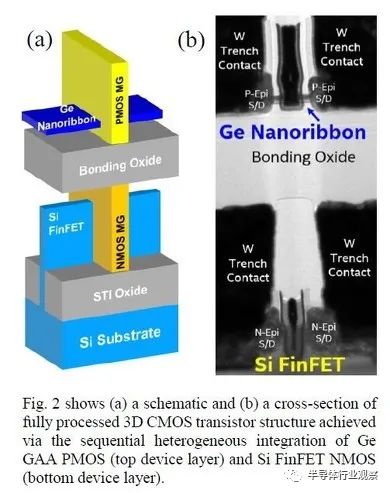

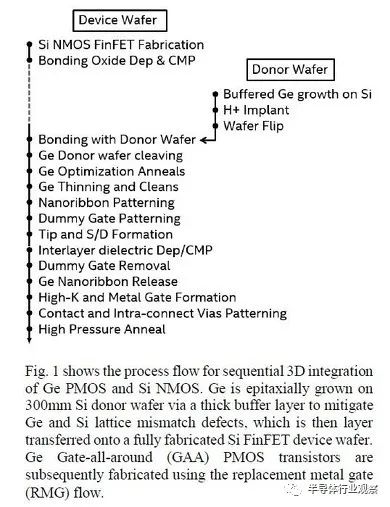

Monolithic制造和Sequential制造

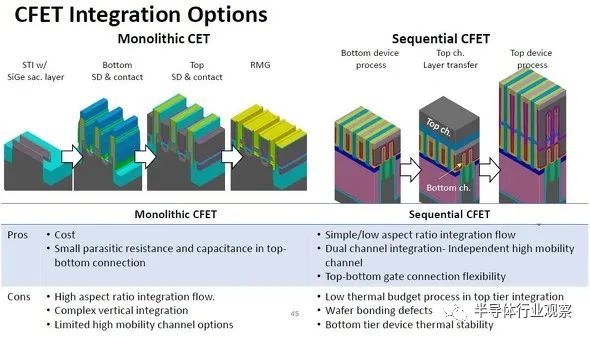

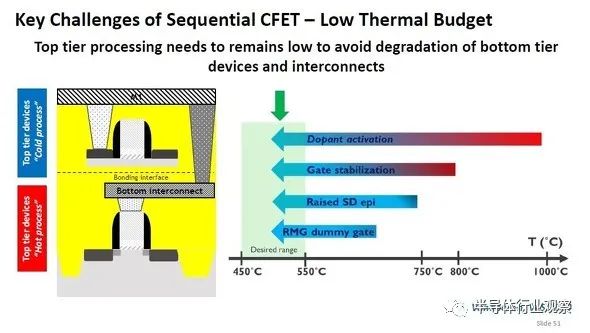

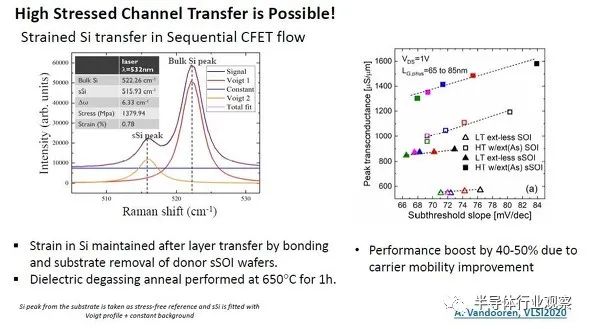

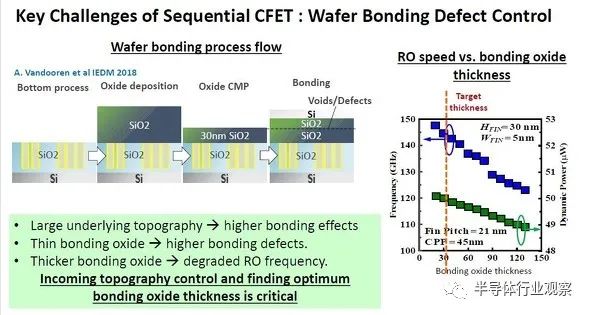

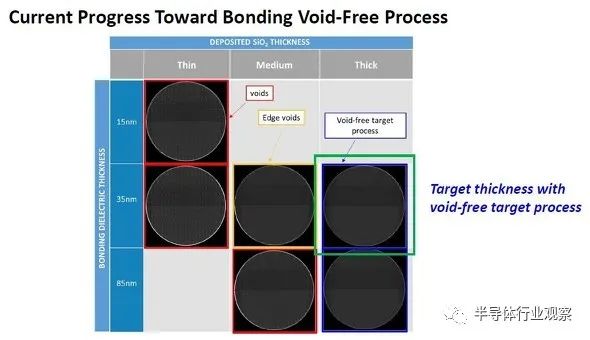

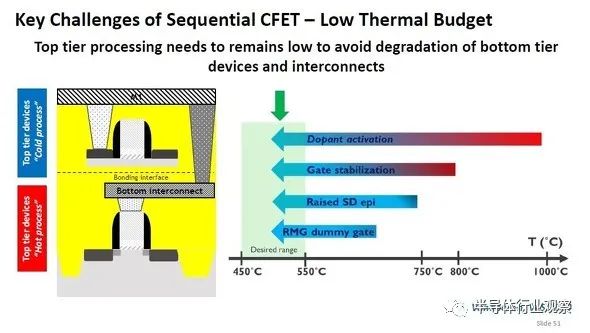

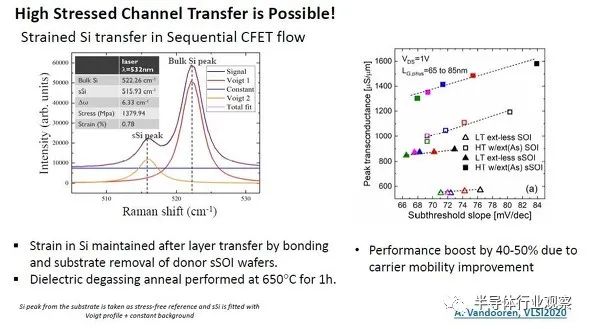

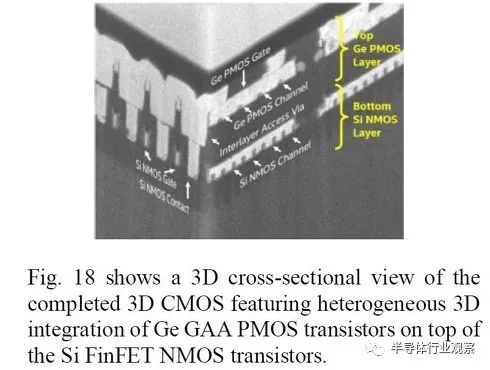

Sequential CFET面临的另一个问题

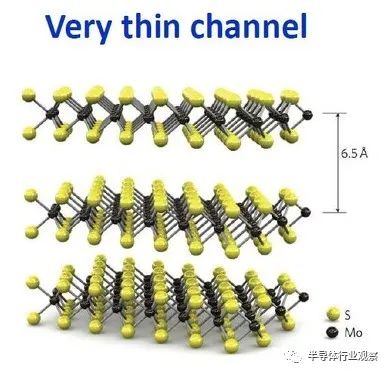

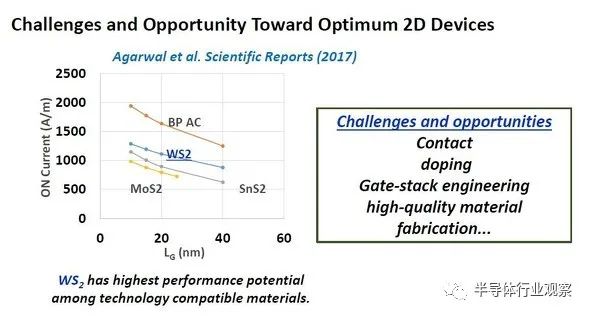

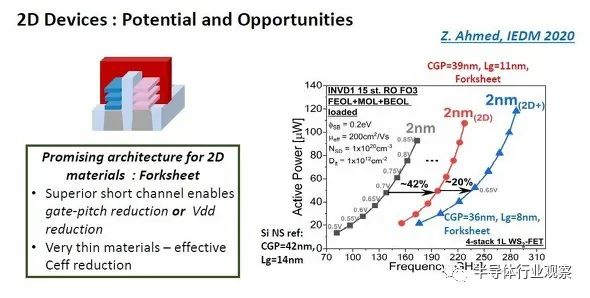

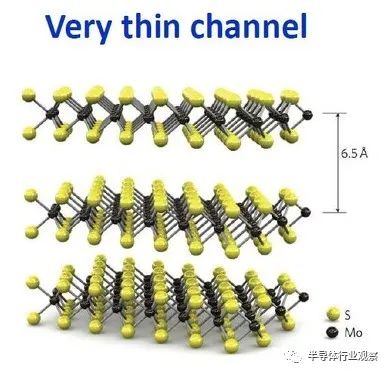

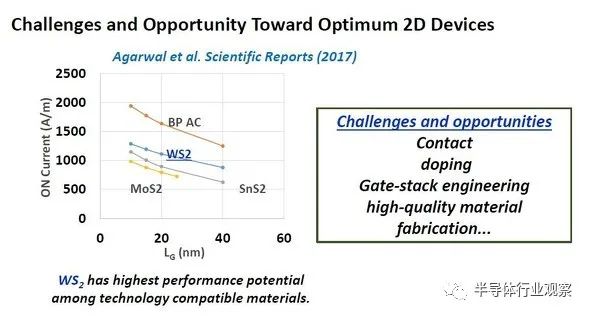

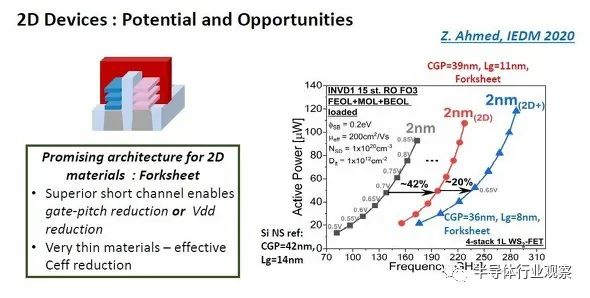

后硅时代,二维材料是选择!

以下文章来源于半导体行业观察 ,作者福田昭

最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

Monolithic制造和Sequential制造

Sequential CFET面临的另一个问题

后硅时代,二维材料是选择!