来源:内容编译自publico,谢谢。

半导体行业观察最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

2347篇原创内容

公众号

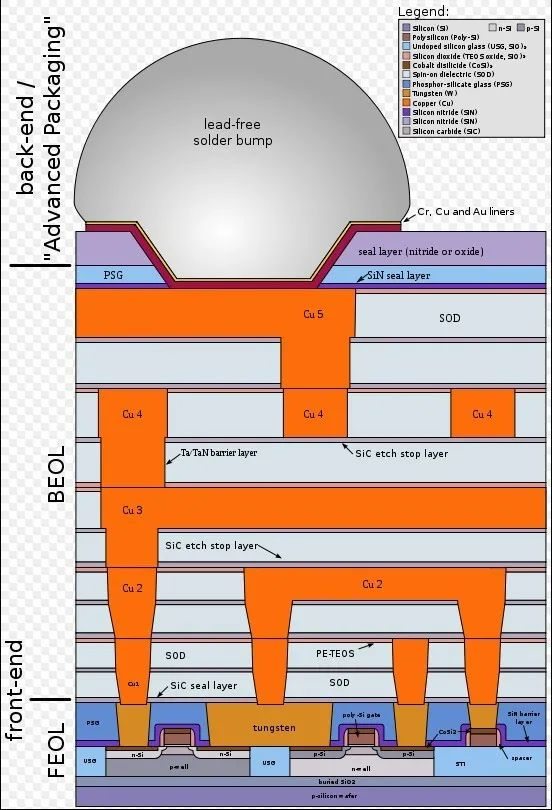

每个晶体管都有三个端子,所有端子都必须正确连接,以便芯片执行其设计功能。当数量如此庞大时,我们需要几个“基板”的金属轨道来实现目标,这是一个真正的挑战,因为互连轨道必须只连接必要的端子,并且必须与其他连接很好地隔离以避免短路。当晶体管数量关闭时会发生什么?在下图中可以看到什么,它是具有五个“基板”或金属化层的芯片的横截面图:图:芯片的横截面图,其中有五个“基板”或金属化层。晶体管位于图像的“底层”(标记为 FEOL),与外部世界的连接位于后端”。用于制作它们的每种材料都在右上角的框中指定。

为了互连如此多的晶体管,我们需要多层互连,其中金属轨道通过防止短路的绝缘层相互隔离。这就是世界上众所周知的“多级互连”,这是一种在 IBM 推出时已经生效了 25 年的范式。如您所见,晶体管位于芯片的第一层,“埋没”在无穷无尽的层中。IBM 引入的一方面是多级,另一方面是替代铝,用铜连接芯片层,因为这种材料的导电性比铝好,但电阻降低了 40%,从而提高了每个芯片的性能,因为互连中耗散的功率要小得多,因为它们从下游通过时所呈现的电阻。定义连接晶体管的金属轨道的方式是使用一种称为光刻的技术完成的,通过这种技术,定义这些轨道的几何图案被转移到芯片上。绝对主导这个市场的制造商是欧洲的ASML。5nm及以下节点的芯片制造商面临的问题是:随着晶体管数量的增加,互连轨道必须变得越来越细,这就是问题的开始:a 金属轨道对电流通过的阻力越来越大它变得更薄。反过来,如果我们有越来越多的晶体管与越来越细的轨道互连,问题就会失控。我将更详细地解释这一点:从本质上讲,制造芯片由三个关键部分组成:晶体管、端子或“腿”之间的触点以及与外界的互连:- 晶体管之间的触点通过不同的层将所有晶体管相互连接。目前的芯片由不少于10层组成,目前最多不超过15层。

- 芯片与外界的互连,即与电脑、手机、GPS等主板的互连。

一些数字可以说明最先进芯片几乎无限的复杂性:其中一种器件的互连总长度约为 30 公里!分布在一个表面上,取决于芯片,范围为 4-8 cm²。在最先进的节点(5 nm)中,据台积电称,该长度可以达到 100 公里。想象这样的事情并不容易。

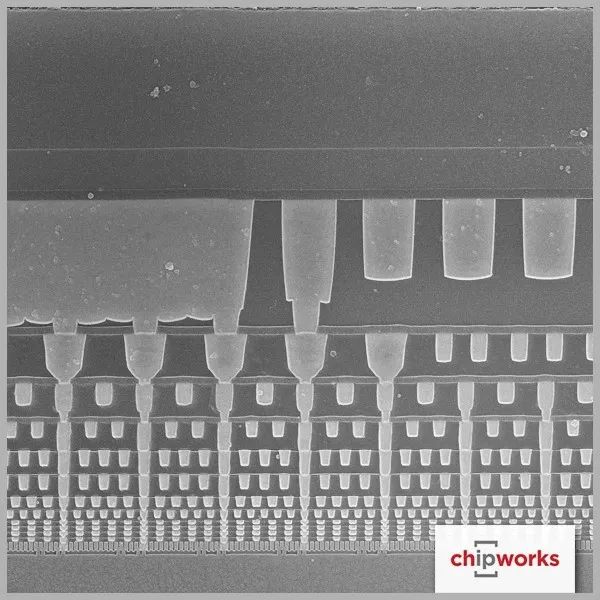

通过减小晶体管的尺寸,它们之间的不同连接层必须更加坚固,它们必须对电流的通过表现出更小的阻力,并且它们的尺寸必须越来越小,这与晶体管尺寸的减小一致。并且这些要求彼此不相容:对电流通过的较低电阻与较小的互连尺寸相矛盾。下边这张图片,真实的说明了这一点:图:英特尔 Broadwwll 芯片横截面的电子显微镜图像,采用14 纳米技术制造。显示了 13 个互连层。随着芯片设计的缩小,金属层变得更加复杂通过减小每个晶体管的尺寸,将第一层连接到最后一层需要在层间越来越小的空间中具有相同或更好的导电性和导热性的新材料。在纳米尺度上减少晶体管意味着必须减少所有尺寸:晶体管的尺寸、互连的尺寸等。也就是说,连接越来越小,尤其是将各个层连接在一起的路径,这增加了正确“填充”它们的难度,这反过来意味着填充它们并因此互连的金属更少层。,这导致对电流通过的更大阻力,呈螺旋状,似乎没有尽头。铜不再是参考材料,因为以所需的速度和精度传导电流变得完全不稳定。换句话说,你可以拥有几纳米尺寸的晶体管,但如果它们不能与合适的金属连接,你就无法制造出没有电损耗、泄漏或击穿的芯片,这会引发消耗或直接使其不切实际。目前,钴或钌似乎是铜的可行替代品,但使用的技术目前未知或未经充分证实。如果有的话,这是微电子行业在未来 2-3 年面临的又一个挑战。毫无疑问,这个行业将继续为我们提供惊喜和想象,就像每次出现新的障碍时一样。

摩尔芯闻您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

244篇原创内容

公众号

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2857内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!