案例解析:IP如何加速 800G 以太网集成

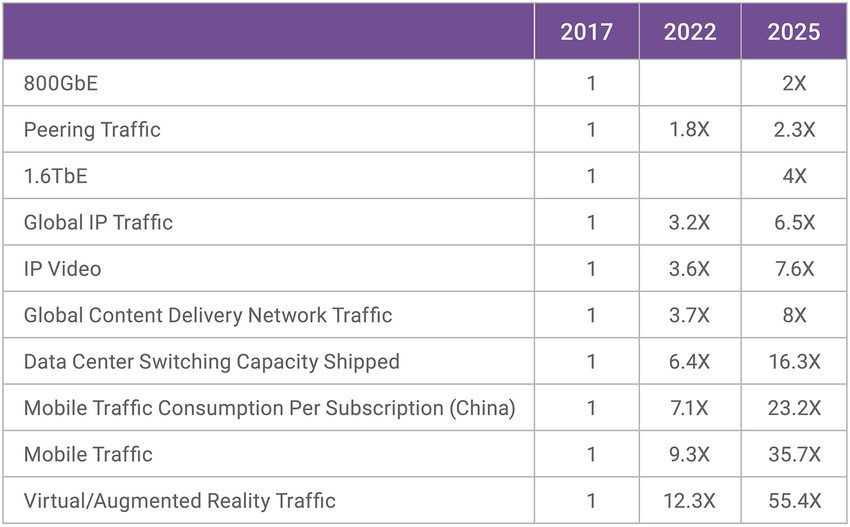

随着用户数量和每个用户设备数量的增加、访问速率的提升、访问方式的增多,以及更加多样化的服务需求的增加等各种因素的影响,处理更加复杂数据需要的带宽正迅猛提升,并驱动了800G和1.6T数据速率的增长。预计 800G 和 1.6T 在 9 年内将分别实现 2 倍和 4 倍的增长,然而,不同内容流的应用增长将达到 7 倍到 55 倍不等,详见 IEEE 802.3 以太网带宽评估报告中的表 1 。

如表 1 所示,带宽需求增加最明显的应用是数据中心的数据交换,在 8 年内达到了 16.3 倍。数据中心机架单元 (RU) 的连接主要为铜线,其他位置则使用光学器件。在 RU 中,交换机的速度将从 12.8T 增加到 25.6T、51.2T 和 102.4T。在可插拔和共封装的光学器件中也观察到相同的速度变化,速度从 400G 到 800G 增长到 1.6T ,甚至更高。以前,12.8T 交换机需要实例化 32 个8路50G SerDes。而下一代交换机,必将会采用112G 和即将出现的 224G SerDes,因为更加高速的 SerDes 拥有更小的面积、更低的成本、更低的功耗、以及更短的上市时间等优势。

IEEE 802.3 工作组定义了 400G 标准,以太网技术联盟定义并发布了更高速度的 800G 标准。400G 的 IEEE 802.3 标准使用多通道分布 (MLD) 技术把数据从单个媒体访问控制 (MAC) 通道分发到 16 个物理编码子层 (PCS) 通道。以太网技术联盟的 800G 标准使用扩展至 800 Gb/s 的 MAC,以及两个 400G Gb/s PCS(经过修改)来驱动 8x100G 通道。两个 PCS 共有 32 条通道(2 个 x16 的 400G 标准的 PCS),均采用 400G 标准支持的 RS (544,514) 前向纠错 (FEC) 技术。

本文对以太网 MAC 和 PHY Layer 进行了说明,并使用案例研究来描述 400G/800G 链路的不同以太网设计配置。

用于 400G/800G 数据速率的

以太网层和配置

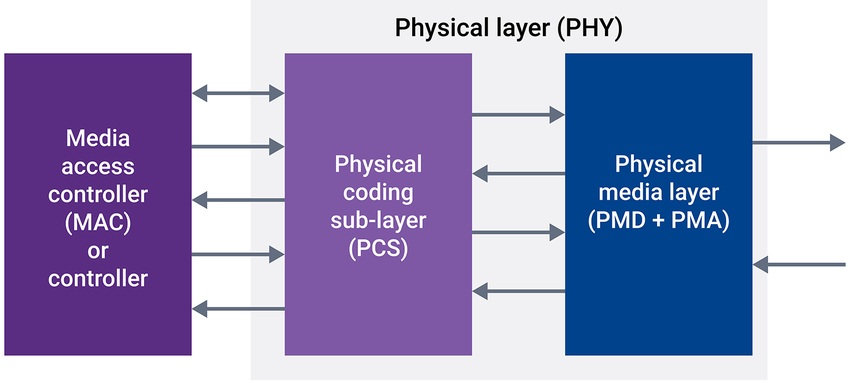

如图 1 所示,一个完整的以太网 IP 子系统包含 PHY 和 MAC。一个兼容 IEEE 802.3 的以太网 IP 子系统范围广泛,从简单的包含 100G MAC/PCS 和 50G SerDes 的系统,到更复杂的、具有多个 MAC/PCS(具有不同配置)和 56G/112G SerDes 的 800G 以太网子系统。

▲图 1:集成的以太网 IP,包括 MAC 和 PHY

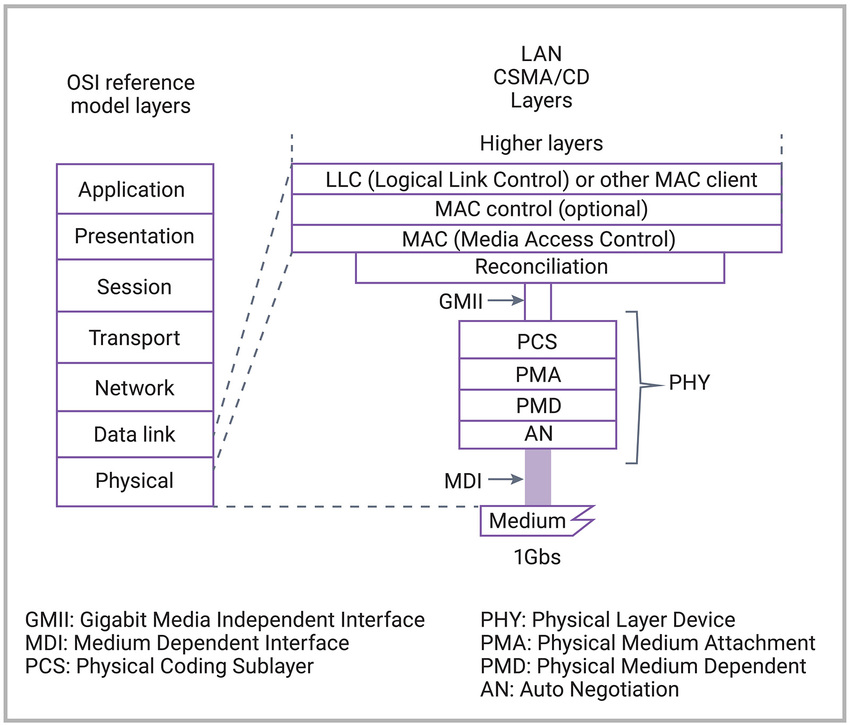

▲图 2:开放式系统互连 (OSI) 模型中的以太网层

高速 SerDes(由 PMA 和 PMD 组成)一般为 56G 或 112G,可以采用 1/2/4 通道配置作为 x1/x2/x4 SerDes。低速 SerDes 则可用于 10G、25G 和 32G PHY。 PCS 将信息传输到 MAC 或其他 PCS 客户端(如中继器),或从 MAC 或其他 PCS 客户端传回信息。

PCS 执行数据帧描述、编码/解码(如 8b/10b 或 64b/66b)、故障信息传输、所接收数据的去偏移以及数据恢复。 高速 PCS 通常提供 200G/400G/800G 数据速率,而低速 PCS 的速率范围为 1G 到 100G。

400G,8x50G SerDes

2x200G,4x50G SerDes

2x200G,8x25G SerDes

数据链路层(包括 MAC 层和逻辑链路控制 (LLC) 层)提供节点到节点间数据传输的直接互连。除了流量控制外,MAC 还处理来自物理层的数据纠错。

案例研究

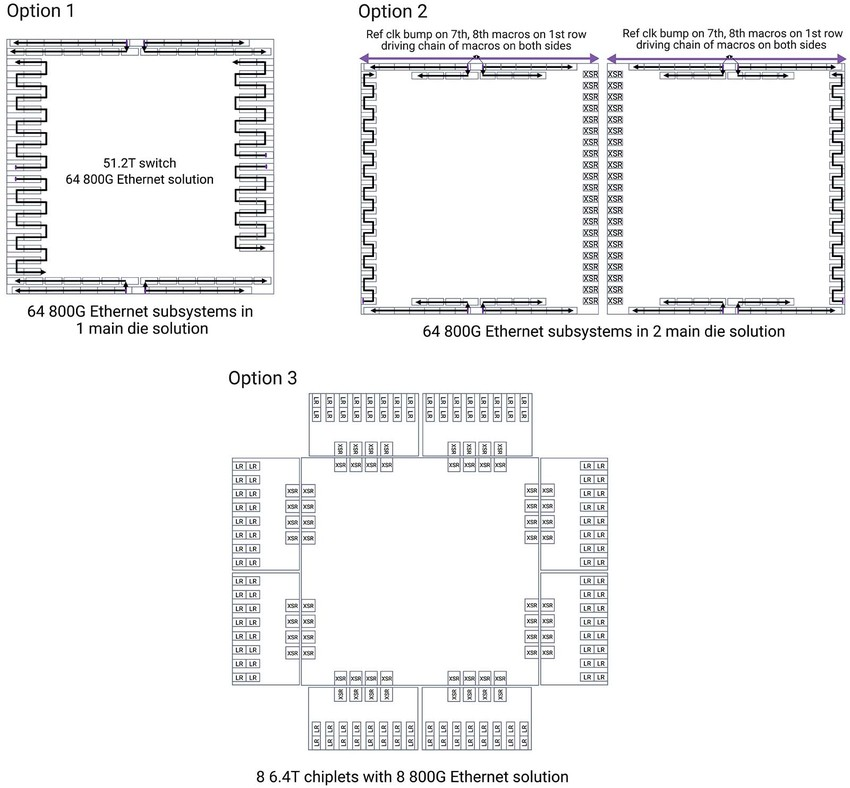

首先,需要考虑参考时钟布线。其次,必须考虑封装逃逸研究,通过满足串扰规范、构建电源供电网络和执行电源完整性仿真,确保整体性能保持一致的要求。图 3 显示了上述三种配置。

▲图 3:不同以太网配置的案例研究

▲图 3:不同以太网配置的案例研究

三是必须要考虑硬化。因为硬化涉及到对模块划分进行假设性分析。通过硬化,可优化Die边缘利用,以及使用从 RTL 到 GDS 完整设计流程的前端和后端集成工作。最后,完整的设计流程还需要了解 SerDes、PCS 和 MAC 的相关设计知识,以及与 EDA 工具密切协作,以达到签核(sign-off)标准。

高性能计算逐渐进入到 AI、自动化、器件封装等应用领域,并出现了许多新的使用和处理复杂数据的方式。这些变化使得用例也持续发生变化。除了传统的以太网外,为了解决良率和成本的问题,出现了一些功能分解的 800G 以太网用例,异构Die也变得越来越流行。OIF 也将推出 3.2T 和 6.4T 标准。800G 的设计挑战将在很多方面影响开发者,包括不断演变的小芯片 (chiplet) 市场,其中 400G/800G 解决方案是关键部分。