来源:编译自semiengineering,谢谢。

半导体芯闻您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

251篇原创内容

公众号

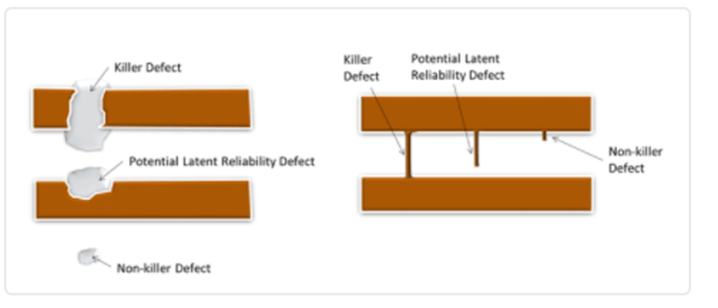

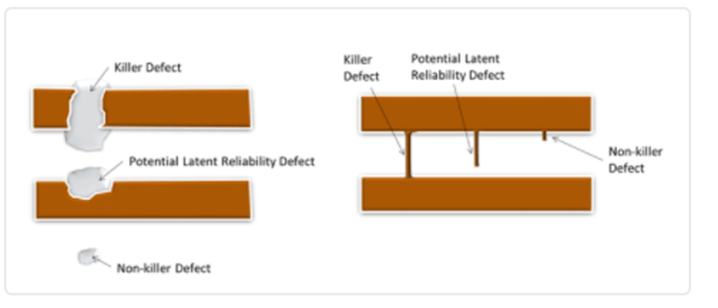

如果工程师每年只筛选 100 万个零件,他们如何向汽车制造商交付十亿分之一 (Dppb) 的缺陷零件?答:通过理解故障机制并主动筛选它们。现代汽车包含近 1,000 个 IC,它们必须在车辆的整个生命周期(15 年)内运行。这推动了更高的质量期望。虽然 10 Dppm 曾经是一个可靠的基准,但现在是 10 Dppb(10 ppm = 10,000 ppb)。这种变化正在推动巨大的工程研发工作,以筛选细微的测试逃逸并消除更多潜在的可靠性故障。在过去五年中,产品工程师和检测设备供应商都开发了新的测试方法和检测能力,帮助实现 10缺陷 Dppb 目标。这些解决方案解决了半导体器件和组件故障机制。(本文仅关注半导体器件缺陷。)所有这些都需要在汽车行业使用的不同半导体工艺的背景下进行设置。很大一部分汽车 IC 是模拟或混合信号组件,它们采用成熟的技术制造,并且具有更大的最小特征尺寸。用于汽车的成熟技术已经满足 10 Dppm 的目标已有相当一段时间了,其 ASP 明显低于以 22 纳米及更小节点开发的复杂 SoC。从 10 Dppm 升级到 10 Dppb 是一项重大的工程成本挑战。Synopsys数字设计部门的产品营销经理 Guy Cortez 说:“无法承受任何测试逃逸的质量敏感客户将愿意牺牲良率,以确保仅向最终客户提供最高质量的设备。” “汽车、医疗和数据中心是质量仍然非常重要的几个垂直领域。”由于启用ADAS功能以及处理越来越多的电子传感器的计算需求,汽车制造商现在需要采用先进 CMOS 工艺的大型 SoC。产品营销高级总监 Nir Sever 表示:“当先进节点半导体发现自己正在驱动任务和服务关键型应用时,质量和可靠性变得更加重要,对停机时间和故障零容忍,例如在数据中心和汽车领域。”在proteanTecs。高级节点 SoC 包含数亿个晶体管和数十亿个通孔,包括从多晶硅到金属和金属到金属层的所有东西。PDF Solutions的首席技术官Andrzej Strojwas 说:“所有这些通孔不仅仅是每个晶圆的十亿分之几。” “你现在真的需要用当前的芯片评估十亿分之几。如果要使用晶圆级检测,则相关数字为ppb 或 ppb 的分数。使用光学设备,您无法负担检查每个晶圆层的费用。此外,对于很多现在相关的缺陷,它们都被掩埋了。你不能用光学看到它们。”这种高期望要求工厂对汽车零部件的检查和测试操作不断创新。与往常一样,为了减少逃逸,工程师首先转向模具和单元级制造测试。添加新的测试模式可以筛选客户退货。对于可靠性故障,应用高压应力测试消除了对昂贵的老化过程的需要。在 2021 年国际测试会议论文中,恩智浦汽车工程师分享了他们的新测试模式,以筛查细微的全速缺陷。一项对汽车客户退货的调查确定了物理根本原因是 PMOS 源极触点缺少其硅化物薄膜,这增加了电阻并影响了栅极延迟。这种行为没有被任何现有的数字延迟故障模型筛选。不幸的是,这种细微的缺陷行为从未被观察到,因为现有的ATPG应用故障模型假设单输入开关。“举例说明这个问题的一个例子可能是两个输入 XOR/XNOR 门,如果两个输入同时改变,它们可能不会在输出端产生逻辑转换。然而,在存在延迟缺陷的情况下,输出端可能会出现延迟转换,这可能会导致时序违规,从而导致故障,”作者解释说。“为了生成能够暴露此缺陷的测试,我们需要有一个针对输入同时转换的刺激。在其他门中可以观察到相同的测试质量差距。尤其值得注意的是,在较小的几何形状中,米勒电容占主导地位,这会导致输入到输出之间的延迟差异,而其他输入静态与其他输入同时切换。”通过创建新的故障模型,即多过渡故障模型 (MTFM),并确定应用该模型的高风险标准单元,工程团队为汽车 IC 部署了新模式。一年多来,该团队报告了两种采用 MTFM 模式的大批量汽车设计的生产测试结果。大约900 万个零件的独特放射性尘埃被测量为大约 5 Dppm 或 5,000 Dppb。工程师继续使用测试来筛选可能对电路可靠性产生不利影响的潜在缺陷。潜在缺陷可能以部分金属线、金属纵梁或栅极氧化物针孔的形式存在。虽然封装管芯的老化应力会加速这些缺陷以表现出故障行为,但对于汽车 IC,可以通过采用晶圆级电应力来跳过这个昂贵的制造步骤。高压应力测试 (HVST) 可加速潜在缺陷,然后通过生产测试对其进行检测。可靠性工程师建议使用内部节点切换其状态的动态电压应力 (DVS),以及内部节点保持相同值的增强电压应力 (EVS)。将 finFET CMOS 器件引入汽车 IC 对应用 HVST 的工程师提出了新的良率/质量/成本三角挑战。在 ITC论文中分享他们的解决方案时,恩智浦汽车工艺工程师指出:“随着基于 finFET 技术的产品设计的引入,基本器件物理特性……对高压应力条件下的静态泄漏消耗有重大贡献。这暴露了如何在 finFET 技术上有效且高效地执行 HVST 的独特挑战。”- 在升高的电压下观察每个裸片静态泄漏的高度可变性,在晶圆探测期间保持 8X 到 32X 的平行度;

- 平衡过低电压应力对产品质量的影响与过高电压应力对产品良率的影响。

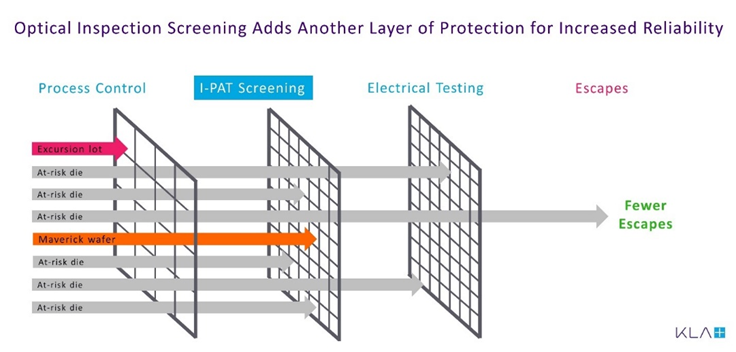

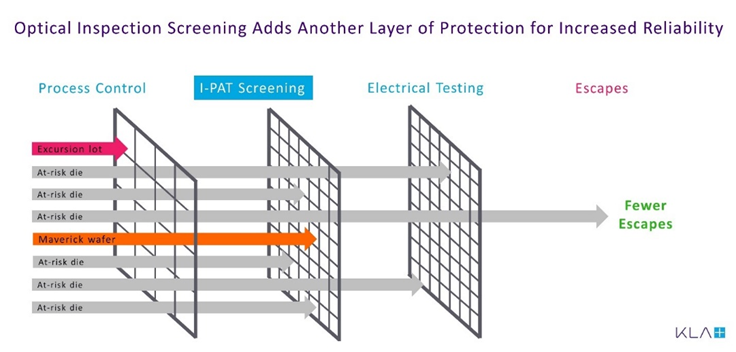

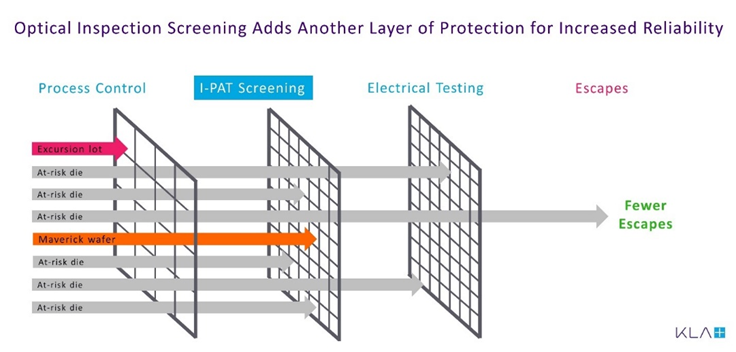

作为回应,工程团队根据 IDD 静态泄漏测量对两种不同的 EVS 限制应用了创新的自适应测试方法。他们写道:“它根据实时电流测量动态调整 HVST 应力电压,以确保每个部件在测试仪硬件电流限制内的最高可能电压下可靠地受到应力,并具有等效的外部缺陷覆盖率。” “通过这种方式,它可以实现预期的测试成本、产品利润和硬件预算,而不会危及产品质量。”通过对特定工艺节点的表征,工艺可靠性工程师达到了两个 EVS 限制。确定静态 IDD 漏电流限值需要基于产品表征方法。工程团队在 NXP 16nm finFET 产品上评估了他们的 HVST 方法,并报告说在 HVST 期间没有发生电流钳位。在制造过程中对关键层进行 100% 晶圆检测的关键驱动因素之一是需要达到足够的质量。只有高速检测系统才能满足工厂中如此高的生产率目标。基于光学和 E-probe 的系统都使汽车 IC 供应商能够识别可能无法通过电气测试的细微缺陷。明场和暗场曝光形式的光学检测仍然是最常用的生产检测技术。每个都有其优点。明场检测擅长检测结构之间的平面缺陷或沟槽内缺陷,而暗场检测擅长检测结构顶部的散射缺陷。KLA 工程师分别与 OnSemi 和 NXP 工程师合作,探索如何利用汽车 IC 零件的检测数据来识别可靠性故障。这些合作推动了异常值检测技术在检测数据中的应用。工程团队最初在 2019 年汽车电子委员会可靠性研讨会上报告了他们的试点研究。在 2020 SPIE论文中,KLA 工程师描述了异常值检测方法,即在线缺陷零件平均测试 (I-PAT),并总结了试点研究结果。“就其本身而言,过程控制方法无法决定单个模具是否健康,” KLA战略合作高级总监 Jay Thatter 说。“但I-PAT 高速检查筛选的出现正在创造一个拐点,由先进的计算能力、图像处理算法和机器学习提供支持。使用I-PAT 进行筛选会检查几个可靠性关键层上 100% 的裸片和 100% 的晶圆。将异常值识别方法引入缺陷域,现在可以将每个芯片的缺陷与更大的总体进行比较,以量化其相对可靠性风险。”

NXP/KLA 可行性研究使用了来自大约 250,000 个芯片(600 个晶圆,每个晶圆大约有 400 个芯片)的历史数据,他们将 I-PAT 缺陷分数与电气测试相关联,包括分类良率、芯片仓、参数值和老化后失败。I-PAT 分数的阈值可以应用于每个裸片缺陷的静态或动态评估。I-PAT 和晶圆测试结果比较的结果表明,有一定百分比的晶圆故障芯片将无法通过 I-PAT 阈值。I-PAT 缺陷评分还确定了一些独特的芯片,这些代表潜在的测试逃逸或潜在的可靠性故障。为了尽量减少失败的良模(又名过度杀伤),OnSemi/KLA 团队描述了他们如何在 I-PAT 分析之前将数据两个过滤器应用于缺陷数据。第一个过滤器仅识别设计关键区域中的缺陷(缺陷敏感性的物理布局分析)。第二个过滤器使用检查层,其中使用检测模式(暗场/光场)曝光检测和确定缺陷大小。结合起来,这两个过滤器将过度杀伤减少了 90%。过滤后,数据通过 I-PAT 方法运行,KLA SPIE 作者描述如下:“I-PAT 方法使用先进的相关引擎根据缺陷检查属性对缺陷概率进行加权……检查属性包括缺陷大小、位置、极性、检测通道、集群等。该方法调用智能和自适应机器学习(ML)模型为每个缺陷分配一个准确的分类。然后根据缺陷对设备可靠性的影响对缺陷进行加权。最重要的是对地面实况指标进行适当评估,以验证分类和权重。然后汇总所有缺陷的影响,以提供每个芯片的总体缺陷分数。然后使用类似于电气测试筛选中使用的 PAT 方法的统计异常值方法过滤这些芯片级缺陷分数。”

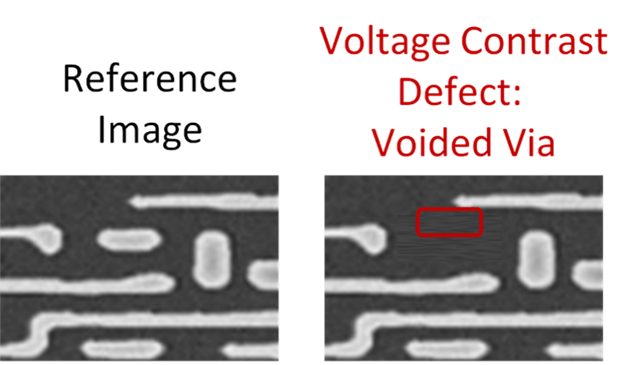

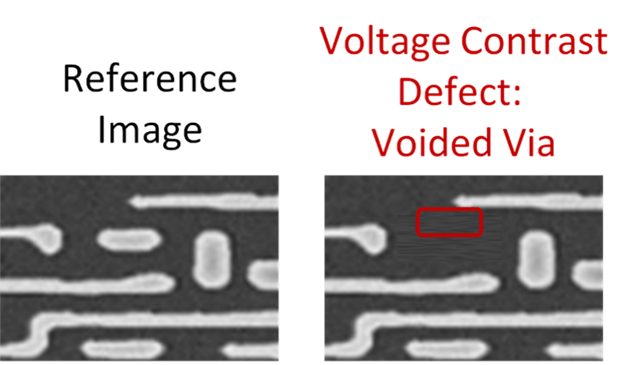

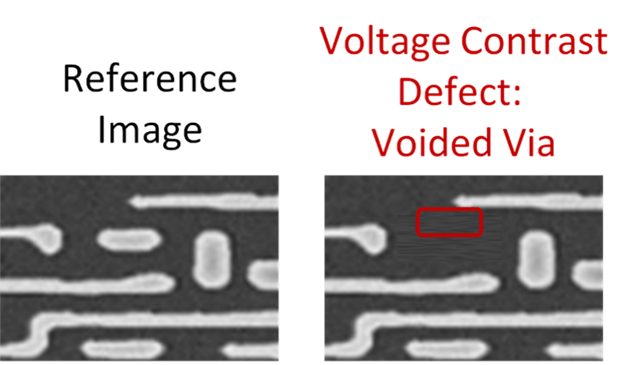

通过 SEM 成像,OnSemi 工程师验证 I-PAT 识别出独特的芯片包含潜在缺陷。电子束提供不同于光学的测量能力。特别是,电压对比使工程师能够检测触点和通孔中存在的亚表面缺陷。PDF Solutions 已调整电子束探针系统,以使用专注于有问题的布局结构的矢量扫描模式执行电压对比度测量。“如果您查看 E-probe 工具本身,我们将其构建为矢量扫描仪的重要原因之一是我们将整体 DirectScan 方法与布局分析联系起来。您基本上可以使用风险最高的模式或诊断工具将模式识别为出错的模式来获取关键层,”PDF Solutions 领先的副总裁 PK Mozumder 说。“你可以运行矢量扫描仪来达到这些点,基本上在两个小时内你就可以获得 ppb 级的分辨率。因此,现在它成为一种制造工具,您可以在生产中使用它来有效地进行非破坏性处置。”识别要探测的有风险的布局模式需要在创建掩模组之前进行预工作。确定设计的有问题的布局结构可为检查设计 (DFI) 填充单元的设计和布局提供信息。这些被放置在非常接近实际设计的单元布局的地方,使用单元之间的空白空间。电子束系统对 DFI 填充单元中的金属垫进行测量。因此,一个产品晶圆可以有数十亿个 DFI 填充单元,这自然提供了十亿分之一的测量分辨率。

图4:将易受攻击的布局模式与DFI 的 E-probe 扫描联系起来然后可以使用电子束探头测量来识别空隙、短路和潜在的可靠性缺陷。在 NANOTS2021论文中,PDF Solutions 工程师描述了这种测量能力:“当用于开路故障模式的 DFI 填充单元垫变暗时,会检测到开路。当不存在缺陷时,由于存在接地路径时发射的二次电子,焊盘将变亮。当 DFI Fill 电池垫变亮时检测到短路。DFI 系统能够测量与软短路或泄漏电流相对应的“灰度”级别——我们将其称为 DFI 电气响应指数 (ERI)。为了将灰度级校准为漏电幅度,将 DFI 测试结构放置在划线中,以便在同一测试结构上测量漏电和 DFI ERI。”

将灰色单元包含在从坏到好芯片的黑白单元之间的能力为工程师提供了下一个制造测试步骤的选择。此外,该电子束测量数据补充了电气测试数据,可检测其中一些软缺陷。泄漏量大的将无法通过电气测试,而泄漏量小的则无法通过电气测试,最终可能会在现场失败。“尽管如此,您仍然希望从测试数据中受益,因为这样您就知道除了测试中弹出的信号之外,您还获得了哪些信号。PDF Solutions 的可制造性设计总经理 Marcin Strojwas 说,您的测试签名中会出现一些漏洞。“然后,仅仅由于这些泄漏的性质,将会有一些略低于你在零时间在测试中能够检测到的阈值。”在过去十年中,工程师一直在以新的组合方式使用不同的数据源来执行根本原因的良率偏差,同时通过更早地识别质量问题来优化晶圆、组装和测试工厂的运营。检测数据——光学、内插晶圆图、电子束——可以与电子筛选相结合,以识别潜在的测试逃逸和与可靠性相关的故障(潜在缺陷)。“当今整合这些不同数据源的一个关键驱动力是努力阻止低可靠性设备逃逸到汽车供应链中,在这些供应链中可能会发生关键任务或安全关键故障。业界众所周知,测试无法识别和阻止每个坏芯片,因此即使测试覆盖率极高,也会发生逃逸,”KLA 的拉特说。“当汽车制造商使用来自新发布节点的设备时,产量较低,问题会变得更糟。并且这种逃逸的统计可能性比指定的期望的十亿分之一要求高出几个数量级。需要新的方法来确定哪些模具适合用途。”晶圆上的划痕可能会导致芯片级可靠性故障。通过结合晶圆测试数据和特定层的 100% 晶圆检测,工程师可以增加对划痕的检测。在 2021 年先进半导体制造会议论文中,来自 SkyWater TechnologyFoundry 和 Onto Innovation 的工程团队描述了他们对晶圆划痕检测的关注:“由于划痕图案独特且对于准确检测至关重要,我们意识到我们需要超越 SPR Engine提供的标准划痕检测算法。因此,我们构建了一个额外的后处理算法,专门用于运行基于图像的划痕检测,而不是使用动态阈值确定(基于密度和分布)的基于缺陷的检测,以消除或减少误报。”

图 6:基于图像的晶圆划痕检测建立在基于缺陷的检测之上识别划痕导致识别潜在的可靠性故障。带有划痕的裸片或其相邻裸片可能会通过晶圆测试,但可能会在单元级测试或现场测试中失败。这是为什么?“从物理上讲,晶圆划痕可以是密集的,也可以是薄的。它们可以指示微裂纹。并且由于晶片切割时的材料物理特性,这种划痕/裂纹将扩散到受影响的管芯边缘和/或相邻管芯。那些相邻的芯片代表了可靠性故障,” Onto Innovation销售和客户解决方案总监 PrasadBachiraju 说。“特别是在汽车领域,当他们检测到这些类型的故障 [SiC 划痕] 时,他们不想冒任何风险。所以它们会在距离划痕不到两毫米的地方死掉。”混合信号/模拟设备在汽车电子控制单元(ECU) 中占主导地位,它们是在非常成熟的半导体工艺上制造的。然而,这些 IC 供应商也需要将质量目标从 10 Dppm 提高到 10 Dppb。在 2020 年欧洲测试研讨会论文中,OnSemi 工程师和 Katholic 大学的研究人员探索了将模具检测数据与每个模具电气测试数据相结合,以增强动态零件平均测试。称为视觉增强 DPAT (VE-DPAT),他们的目标是筛选出动态 PAT 未检测到的细微潜在缺陷,几乎没有产量损失。工程团队研究了将两个数据源与乘法相结合。他们将其描述为新的指标。“筛选参数 α A,D i被构造为两个标准化数的乘积,并作为结果给出一个标准化数。选择这种配方是因为它具有优越的性能。它可以用于不同的规格,从以纳安表示的泄漏测量到以 MHz 表示的振荡频率。这两个标准化数字的一般解释几乎可以被认为是有缺陷设备的概率。”其他方面的标准化值,异常值检测率显着提高,并且在生产测试过程中更易于实施。关于通过/失败限制,他们写道:“在计算测量 A的筛选参数 α A,D i之后,如果值 α A ,D i超过由设计。在实践中,模具 D i被赋予一系列异常值参数 α A,D i,即针对发现缺陷的每一层,结合激活异常值方法的每个测量值。”直接的乘法可能会导致具有不相关电气偏差的缺陷,从而导致不必要的良率损失。为了改进乘法,他们使用了设计工程师对布局、缺陷大小和电气测试的潜在相关性的了解。他们评估了采用 0.35µm 双极CMOS DMOS (BCD) 技术制造的升压双降压 LED 驱动器(用于 60V 和 1.6 安培的汽车照明应用)的 VE-DPAT 指标。数据是从 5 个批次的 25 个晶圆中收集的,数据包括 7 个晶圆制造步骤的检查和每个芯片约 400 次电气测试。在将第一种乘法方法应用于各种检测阈值时,他们报告了当 TH 等于 4 时额外的 1% 拒绝,以及当 TH等于 10 时 0.1% 的拒绝。他们进一步分享了这一指标,独特地发现了一个有影响的缺陷,被描述为“大与同一 DMOS 上的异常电流泄漏相关的输出驱动器的 DMOS。”工程团队在满足汽车制造商极其严格的 10 Dppb 质量目标方面取得了长足的进步。工程师选择部署的方法将对应于半导体技术成熟度和产品的 ASP。随着车辆中发现的广泛的半导体技术,人们可以期待广泛的解决方案。工程师必须同时找出细微的缺陷,同时保持最小的成本——以美分和 0.01% 的良率损失来衡量。因为在汽车行业,虽然质量至关重要,但保持供应商盈利能力也是如此。

半导体行业观察最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

2518篇原创内容

公众号